引言过去18个月,关于半导体制造以及美国国内芯片制造方面落后的充分担忧,已经有了大量的书面报道和讨论。

针对这一问题,美国政府颁布了《CHIPS和科学法案》。这项法案提供的资金旨在推动美国国内芯片制造的更快发展。

虽然,这一切的初衷都很好,但一旦这些先进的芯片被制造出来,它们将何去何从?正如人们所说,“光有芯片也没用”。

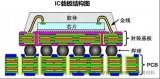

这些芯片需要高阶PWB来支持这些封装。PWB和IC载板是这些芯片、微处理器、电容器、存储器、逻辑等安装和互连的物理平台。

如果没有高可靠性、高密度的平台,芯片将无处可去。这正是必须采用关键技术、工艺和材料来支持芯片生产和高阶封装的原因。

定位和材料选择

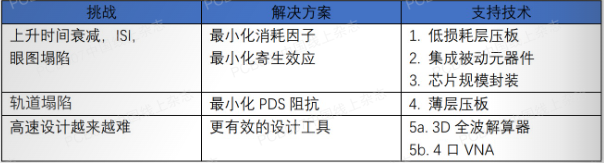

HDI板的特点是特征更小和对准更严苛。为此,特征补偿和缩放比普通电路板更重要。HDI板也用于高频应用,因此,满足这些需求为工程设计、定位部门带来了新的挑战。表1显示了工程设计高频板的三大挑战。

表1:高速HDI板面临三大挑战

材料选择同样重要,特别是因为无铅组装温度及其对层压板分层和可靠性的影响。重要的新功能包括:

使用“共面波导”和共面带状线模型的高频板的阻抗计算和堆叠。

新型酚醛环氧树脂和无卤FR-4的特性和放大、特征补偿。

能够添加局部基准以对准激光钻孔CCD相机。

根据直径、深度和材料类型存储激光钻孔参数的系统。

塞孔的特征,以确定埋孔的放置是否会产生问题。

从材料的角度来看,低Dk和低损耗层压材料是首选的层压材料。需要满足信号完整性和阻抗匹配要求。最小化高频信号损耗对于支持高阶封装的IC载板技术至关重要。这使人们能够更好地理解导通孔形成和去钻污、去金属化。

小孔、小孔微导通孔形成

虽然HDI通常与激光钻孔相关,但也可以通过机械钻孔和化学蚀刻形成小盲孔。重要的是确保每个板都能接收到正确的微导通孔钻孔参数。理想情况下,形成的导通孔形状时在通孔顶部有更宽的开口,向下逐渐变细。

导通孔的形状对于实现均匀镀铜至关重要。电镀操作的流体动力学要求不断补充关键电镀添加剂,以确保更换新鲜电解液以减少浓度极化。随着浓度极化,扩散层会缺少铜离子和其他添加剂。

注意,盲孔的直径在顶部略窄。此外,整体导通孔的质量受到影响,是过度去除粘合剂材料。在这种情况下,电解液到盲孔的层流被破坏,进一步影响均匀电镀。

需要考虑的其他重要因素和条件包括:

确保外层的层压厚度一致,否则将严重影响激光钻孔。

注意能级,以免在盲孔底部产生分层或环氧树脂残留物。仔细选择要激光钻孔的电介质(可激光钻孔的半固化片)。

检查激光钻孔设备的景深,以验证可以激光钻孔的最厚板材。

制造商必须投资最新的对准和导通孔形成设备。

可能存在孔和导通孔的定位精度问题

可用于预测材料移动的系统

去钻污和金属化

从纯材料的角度来看,这些高性能树脂更难去钻污和金属化。因为模量更高,材料更脆。这些材料也更耐化学工艺,包括碱性高锰酸盐化学工艺。人们不能依赖常见的具有较低Tg材料树脂的高表面积和蜂巢状结构。

然而,为了确保清除钻屑和其他碎屑,碱性高锰酸盐工艺还必须活化树脂和玻纤,以确保后续镀铜的附着力。松散的碎屑和光滑的树脂表面将无法提供足够的附着力,因而无法承受热偏移和机械冲击。

精细走线成像、显影

光刻法是高阶封装和IC载板生产的基石。激光直接成像现在是生产高密度与超高密度载板的必备技术。在不断突破超高密度技术极限的过程中,传统的接触式印制技术显现出了不足之处,于是促进了激光直接成像(laser direct imaging,简称LDI)技术的发展与应用。

与接触式印制技术相比,LDI系统有诸多优势。例如使用LDI技术生产的PCB具有更小的对准容差,直接通过CAD系统印制图形也不再需要使用底片。

而使用接触式印制技术时,底片或面板的尺寸变化会引起对准错误。尺寸之所以发生变化是因为掩模和面板材料(如FR-4)尺寸会随着温度及湿度(在一般的工厂环境下分别控制在±2°C和±5%RH)的变化而变化。

下方列出了制造电路时的5个步骤:

表面制备

抗蚀剂贴合

曝光

显影

蚀刻

先来看曝光工艺。

在使用LED、LDI技术时,总是能听到“焦距”(depth of focus,简称DOF)这个术语。设置正确的DOF是实现最佳分辨率的关键。反之,如果DOF设置不当,就会导致线宽或线距增加、断开或出现走线扭曲缺陷。所以说一定要确保DOF准确无误。

另一个必不可少的步骤是找到成像工艺中的应力点。可以使用精细走线螺旋或精细走线和细间距等测试图形找到应力点。其中包括标有刻度的精细走线和线距,例如100、75、50和25微米的精细走线和线距。这种评估还有助于深入了解其他会影响成像分辨率的工艺参数。

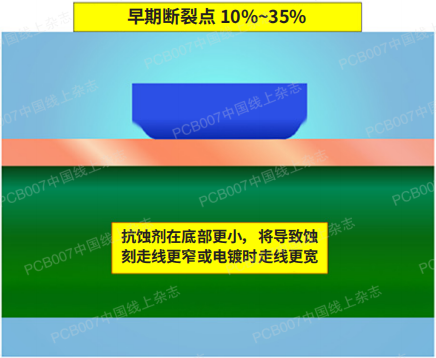

例如较高的曝光能量会增强抗蚀剂的附着力。此外,铜箔类型(ED、RTF、RA)、表面制备方式和显影点提前都会影响成像的分辨率。千万不要低估显影点的威力。图1示意图中展示了显影点提前。

图1:显影过程中早期形成的断裂点(来源:Tim Blair,Tim Blair LLC)

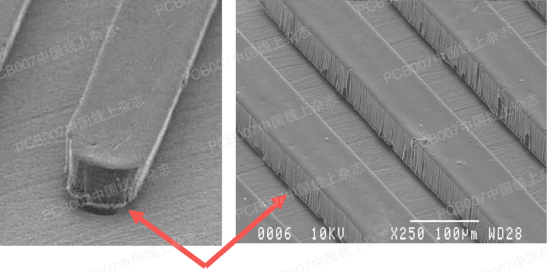

即便使用了理想的曝光能量和表面制备方式,抗蚀剂宽度减少的风险也是相当高的。图2显示了此类问题的实际扫描电子显微图。显影点提前会导致显影过度和侧蚀问题,而这种情况会进一步导致内层走线宽度变窄。

图2:早期形成断裂点会导致显影过度(来源:Tim Blair,Tim Blair LLC)

蚀刻

可以说显影和蚀刻是相通的。万事万物皆有联系,这是排除故障时的基本规则。值得注意的是,无论是使用碱性蚀刻液还是酸性蚀刻液,蚀刻都是各向同性的。这就意味着Z轴的铜被蚀刻去除后,侧面的铜也会被横向去除。

一定要严格控制蚀刻的关键工艺参数。碱性氨水蚀刻技术可用于蚀刻内层和外层。但控制精细走线蚀刻工艺的关键参数是碱性蚀刻溶液的pH值。将溶液的pH值保持在8.0~8.2之间有助于降低横向蚀刻和侧蚀。当然,溶液的比重也很重要。将溶液比重保持在上限水平附近有助于减轻横向蚀刻。

另外,像氯化铜这样的酸性蚀刻剂只能用于内层。这种蚀刻剂与金属抗蚀剂不兼容。但与碱性蚀刻技术相比,酸性蚀刻具备更理想的蚀刻因数和侧蚀。有报告称,将酸性蚀刻剂控制在很低的游离酸常态下可以提高蚀刻系数。

还有其他研究对比了不同蚀刻蚀和不同光致抗蚀剂厚度下的蚀刻因数。T.Yamamot等人的早期研究证明了蚀刻通道加宽、抗蚀剂变薄之后产生的有利影响。以上引用的研究也证实了:与碱性蚀刻剂相比,铜蚀刻剂在侧蚀方面具备的优势。

减成法蚀刻加工出的电路密度是有极限的。这是众所周知的常识。蚀刻剂去除目标位置铜的过程越长,就越有可能出现侧蚀和走线宽度变窄。改用半加成型工艺并减小铜箔厚度,或使用介质薄膜可大幅提高蚀刻因数。

审核编辑:汤梓红

-

芯片

+关注

关注

463文章

54412浏览量

469191 -

电容器

+关注

关注

64文章

6970浏览量

108516 -

封装

+关注

关注

128文章

9329浏览量

149039 -

HDI板

+关注

关注

2文章

65浏览量

16181 -

IC载板

+关注

关注

7文章

54浏览量

16384

原文标题:生产高阶封装使用IC载板的初步挑战

文章出处:【微信号:actSMTC,微信公众号:actSMTC】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

迈开3D IC量产脚步 半导体厂猛攻覆晶封装

IC制造商克服精度挑战的技术有哪些?

26亿红板5G高阶HDI和IC载板项目签约江西

Orbotech Corus™ 8M全自动双面直接成像(DI)专为高阶HDI和IC载板生产而设计

UHDI及高阶封装技术对检测系统的挑战

生产高阶封装使用IC载板的初步挑战

生产高阶封装使用IC载板的初步挑战

评论