16阻抗补偿技术

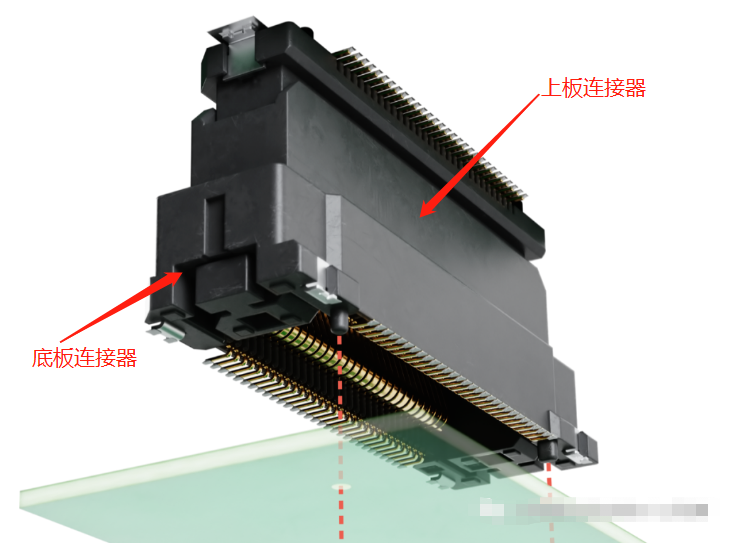

针对传输线上寄生电容和寄生电感带来的反射噪声,在现实PCB设计中是无法避免的。例如2个PCB板通过B2B连接器结合时,B2B连接器的寄生电感。下图是一对B2B连接器,可以将两块PCB连接起来。

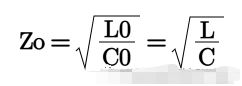

使用补偿设计可以抵消一部分反射噪声。此种补偿设计的出发点就是尽量让信号,在传输线上传输的过程中,不要感受到很大的感性突变,即信号遇到的传输线阻抗始终是一致的。在之前的文章《信号完整性之传输线--四》的文章中提到,理想传输线的一阶模型

Z0是传输线特征阻抗(单位Ω);L0是单位长度电感(单位nH/in);C0是单位长度电容(单位nF/in);L是整段传输线总电感(单位nH);C是整段传输线总电容(单位nF)。

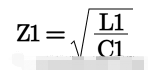

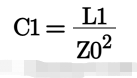

在感性阻抗突变L1的附近添加补充电容C1,可以将感性突变补偿成一段阻抗可控的传输线。

为了将反射信号噪声降低到最小,需要找到一个合适的电容值。使感性阻抗突变这一段传输线的阻抗等于传输线目标,即Z0=Z1。由此得知:

例如某连接器的寄生电感为10nH,传输线阻抗是50R,则总的补充电容为

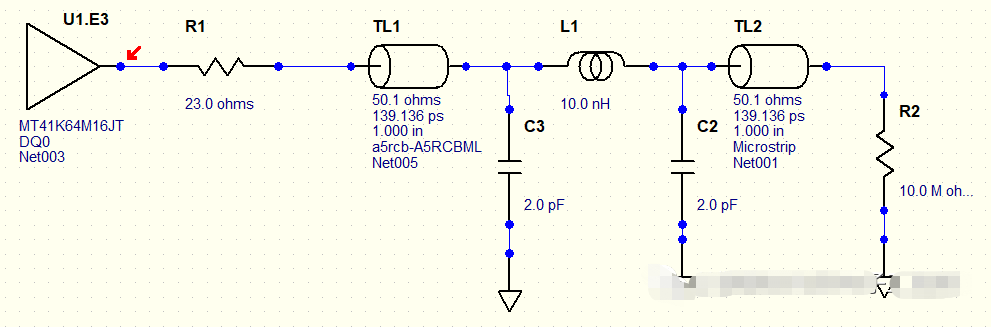

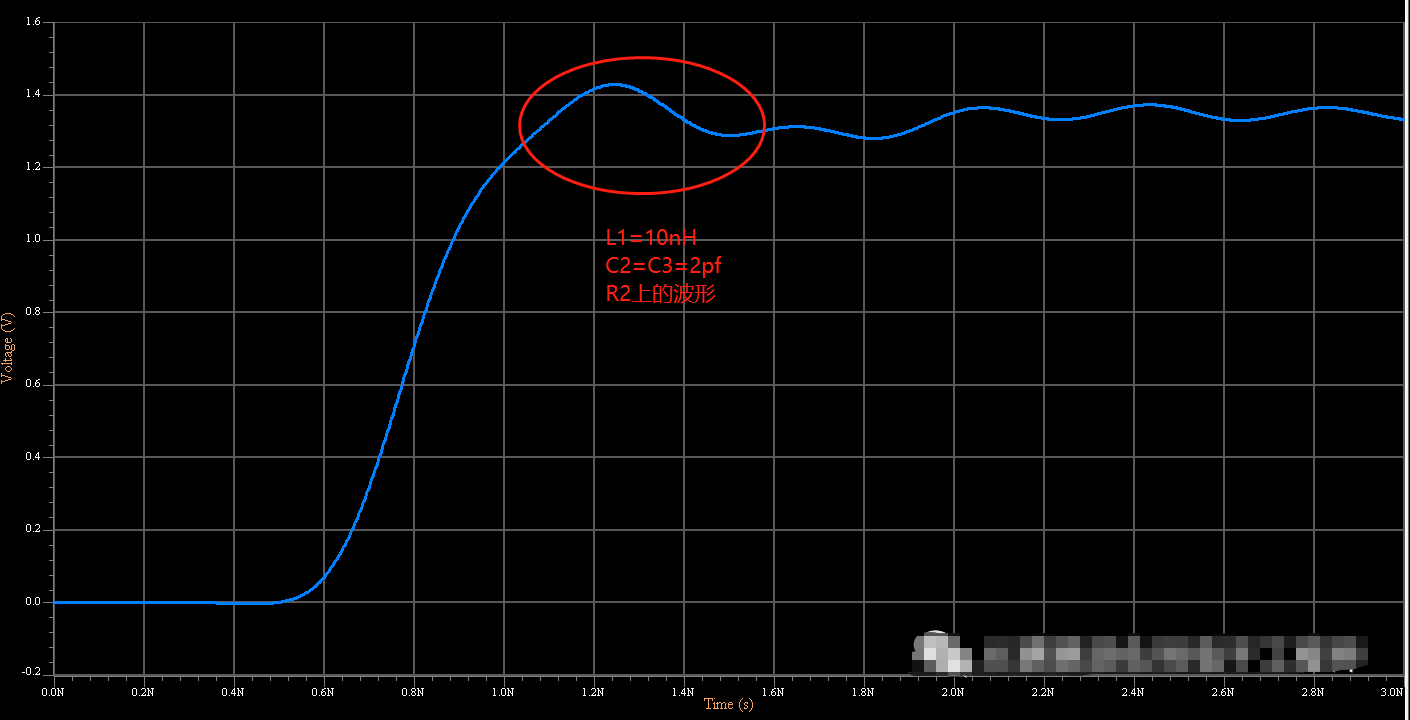

C1=10/50*50=4pF。连接器左右两边各1个2pf的电容是比较推荐的补偿方式。

上述的这种方法,根据信号上升时间不同,对反射噪声的补充不同。有时可以降低75%的反射噪声。除了连接器,此方法也可用在其他有感性突变的电路中,例如过孔、电阻等。

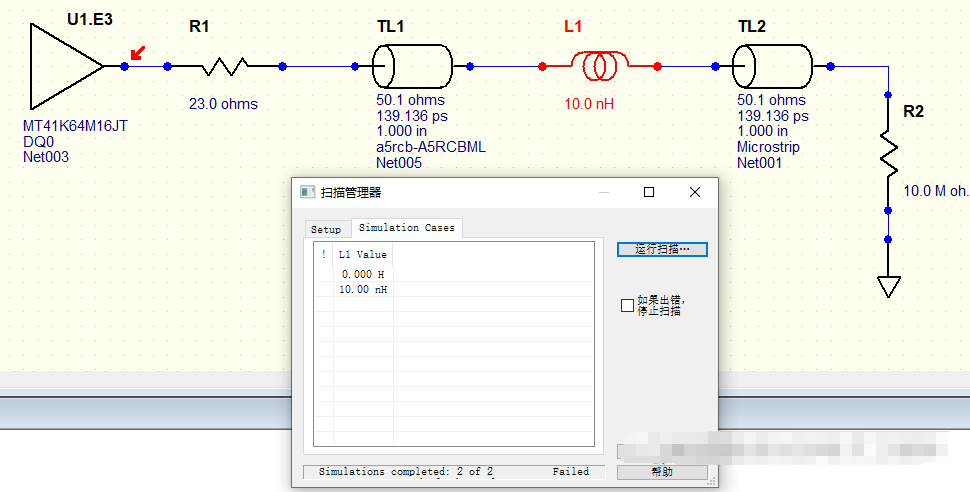

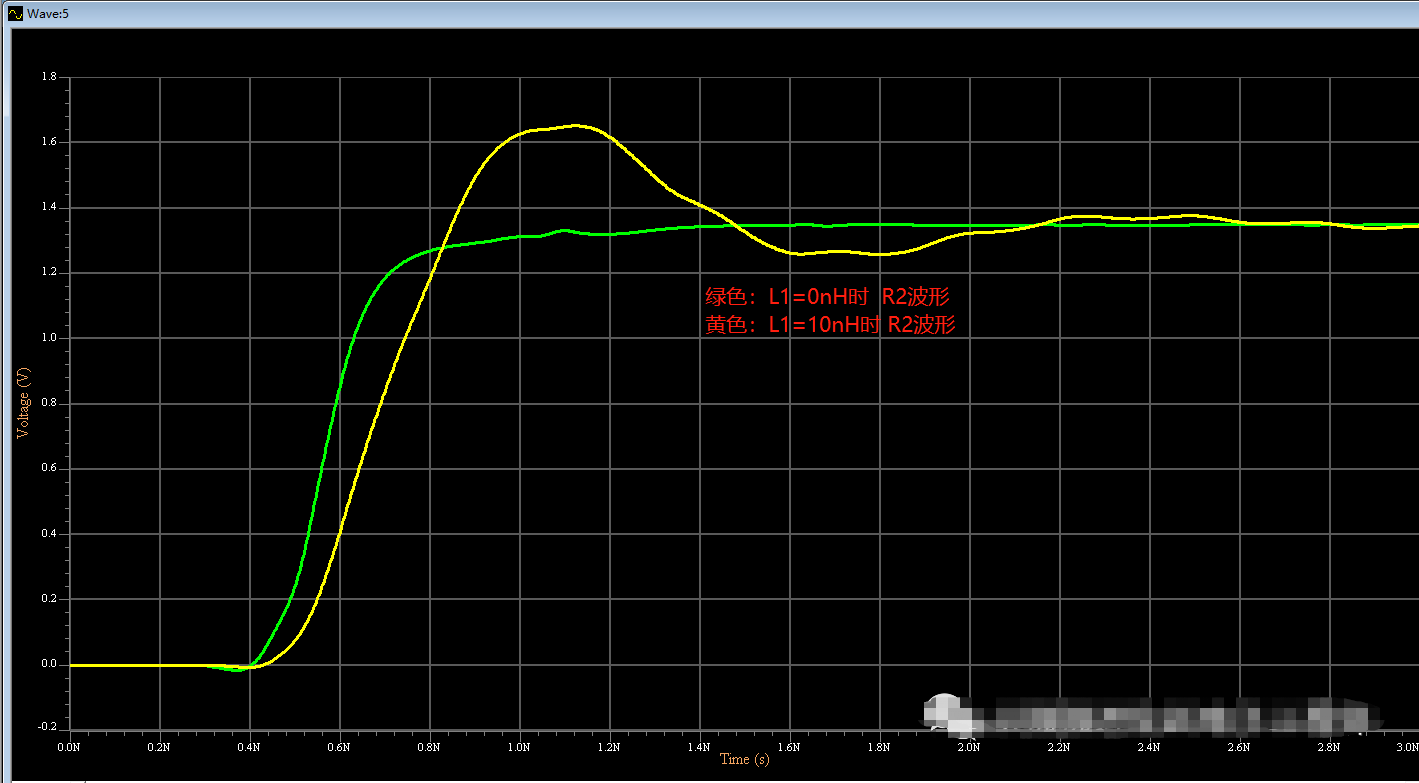

如下是仿真数据。首先是L1=0nH和L1=10nH的波形

看仿真结果,传输线上没有寄生电感时,波形没有反射(绿色波形)。当有一个10nH的寄生电感存在时,波形明显反射(黄色过冲)。

针对L1=10nH,在L1左右两边各放置1个2pf电容C2和C3(C2+C3=4pf),仿真电路如下

看仿真结果,信号过冲已经比电容不存在时降低了大约0.2V。

-

pcb

+关注

关注

4391文章

23742浏览量

420729 -

连接器

+关注

关注

102文章

15919浏览量

145382 -

PCB设计

+关注

关注

396文章

4907浏览量

94065 -

信号完整性

+关注

关注

68文章

1473浏览量

97768 -

反射

+关注

关注

0文章

69浏览量

16186

发布评论请先 登录

信号完整性(五):信号反射

信号完整性简介及protel信号完整性设计指南

信号完整性之反射(八)

信号完整性之反射(八)

评论