6 使用TDR测试反射

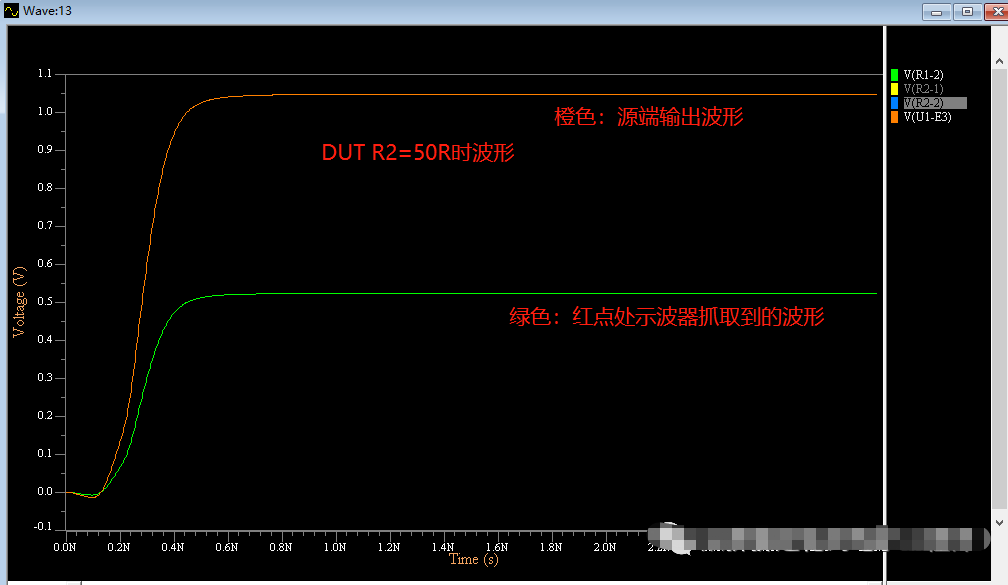

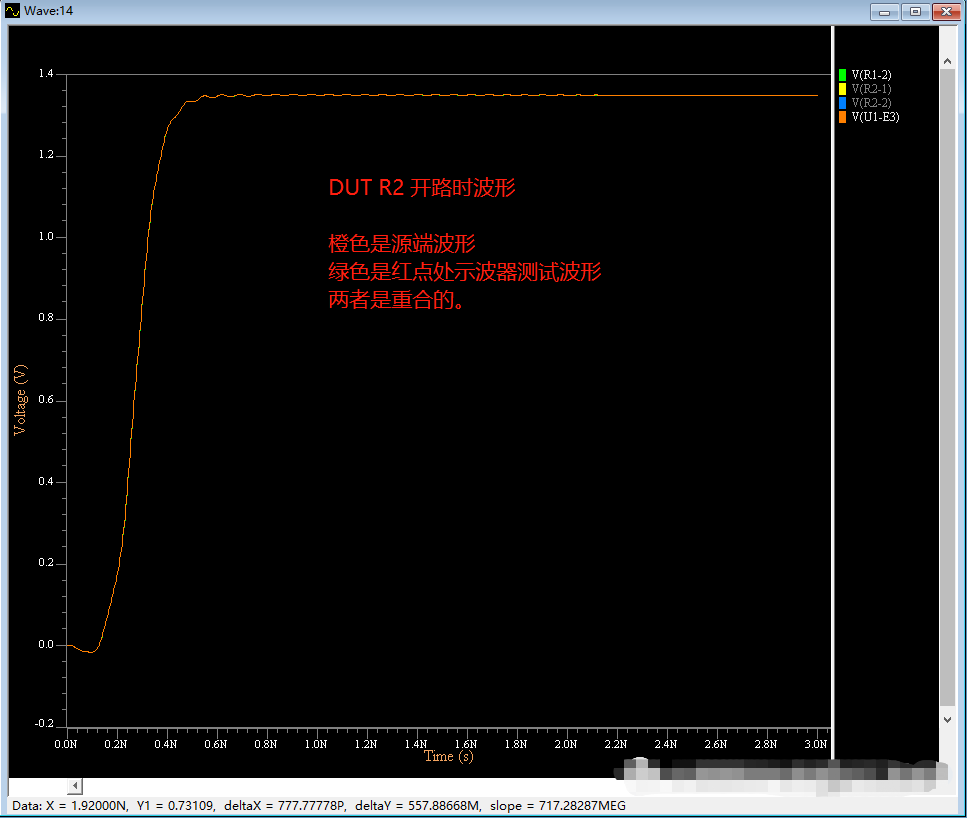

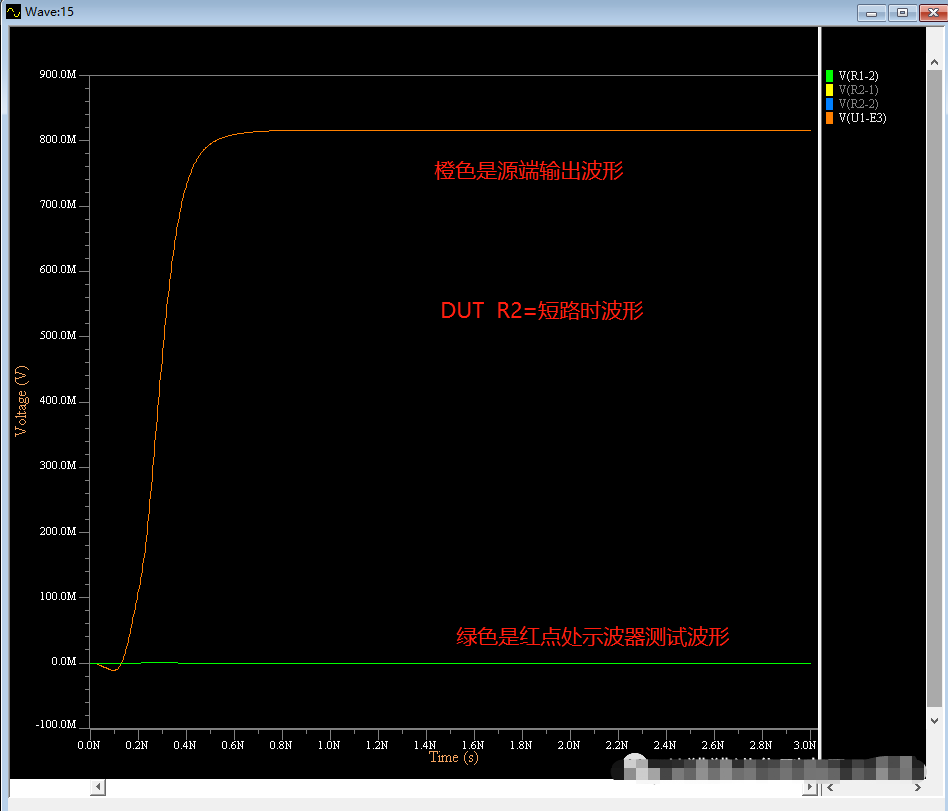

TDR称为时域反射计,可以用来测量本身没有电压源的无源互连线特性。下图是TDR的内部结构。源端输出一个35ps~150ps的快速上升沿信号。信号经过一个50R的校准电阻和一段很短的50R同轴电缆线,到达设备的前面板连接端子。此连接端子连接到DUT(待测无源传输线)。高速采样放大器测试红色点的电压值。

例如源端在发射信号之前,红点处的电压是0V。当一个400mV的脉冲信号从源端输出到达红点时,50R校准电阻和50R的同轴电缆分压,使红点处的电压为400mV x 50R/(50+50)R=200mV。高速采样放大器记录下此200mV。剩余的200mV继续向前传输。

①如果DUT是一个50R的终端,则没有反射发生。红点处不会收到反射信号,只有最初的200mV原始信号。

②如果DUT是开路,在DUT处有200mV的反射,这个反射信号会立刻反射回到红点处,此时红点处的电压是400mV。

③如果DUT是短路,在DUT处有-200mV的反射,这个反射信号会立刻反射回到红点处,此时红点处的电压是0mV。

因此TDR就是基于红点处的电压,知道DUT的阻抗是多少。

如下是对上述几种情况的仿真:仿真结果和上述情况一致。

7 传输线的非故意阻抗突变

即使PCB设计时使用阻抗可控的PCB走线,还是有一些因素会造成阻抗突变,进而造成反射,影响信号质量。例如:

封装引线

输入门电容

信号层间的过孔

走线拐角

走线分支和桩线

测试焊盘

返回路径上的间隙

走线交叉

信号的上升时间和阻抗突变的大小,对信号失真程度的影响很大。电容和电感的阻抗是由电压、电流的瞬时变化率决定(上升或者下降时间)。现实中,设计一个没有反射的互连线是不可能的。只能将反射噪声设计的低于电路允许的噪声范围。通常反射噪声应该被控制在电压振幅的10%之内,要求严苛的是小于5%。

终端阻抗是电阻时,阻抗是常数,很容易计算得到反射电压。当终端是较复杂的元件时(例如电感、电容等),计算就没那么简单了。用仿真工具会比较好。

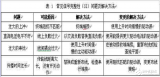

8 何时需要端接

最基本的传输线结构是有一个驱动端、短的可控传输线、接收器(负载)组成。信号通常会在低阻抗驱动端和高阻抗负载端之间来回反贪。当传输线很长时,多次反射会引起信号完整性问题,表现为振铃。如果传输线很短,即使发生反射也被上升沿或者下降沿覆盖,有可能不会带来问题。

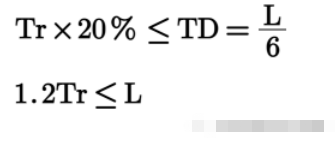

当时延小于上升时间的20%时,反射几乎看不见。当时延超过上升时间的20%时,振铃就会明显了。因此当时延TD>Tr x 20%时,就要考虑在传输线上进行端接了。

例如某信号的上升时间是Tr(ns),某段走线的长度时L(in),因为针对FR4的走线,信号速度是6in/ns,信号延迟是TD,因此

即当走线长度L大于1.2倍的Tr时,需要考虑端接。当走线长度L小于1.2倍时,可以考虑不端接。

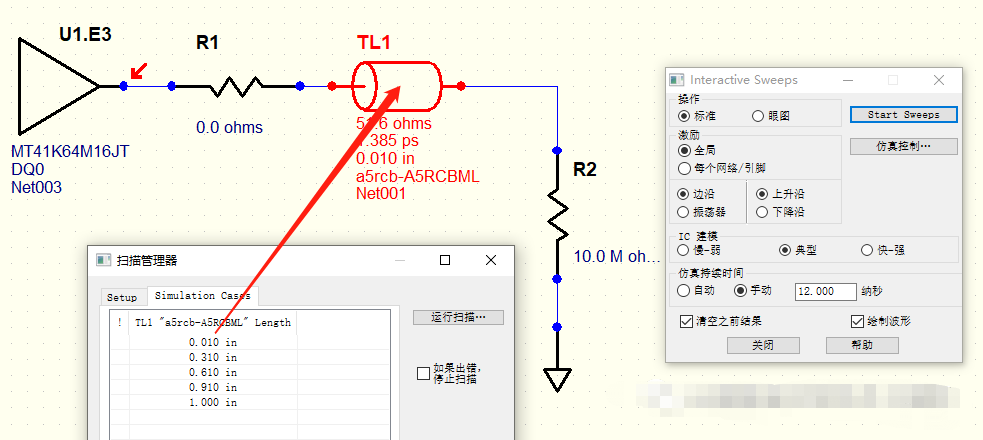

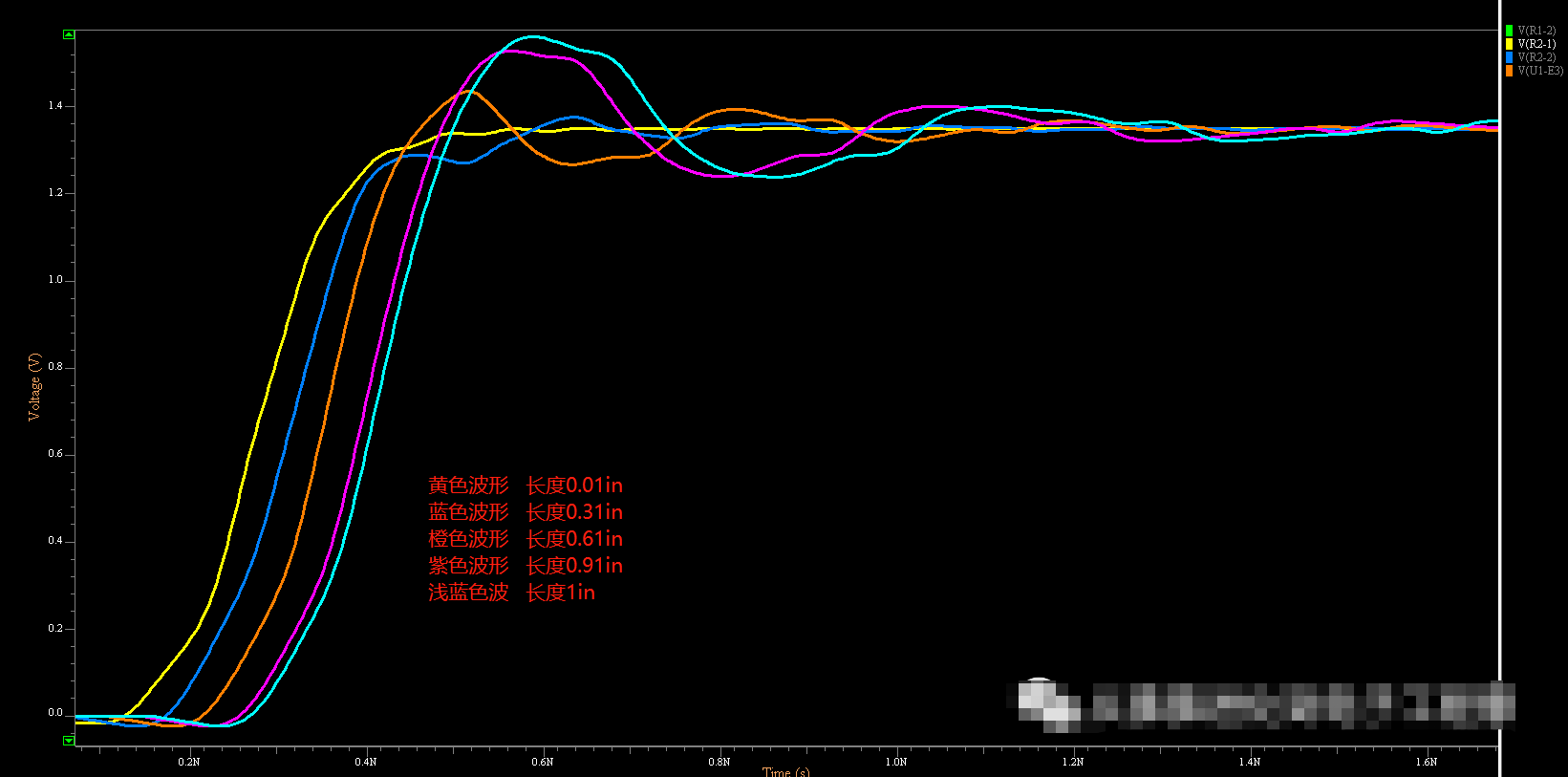

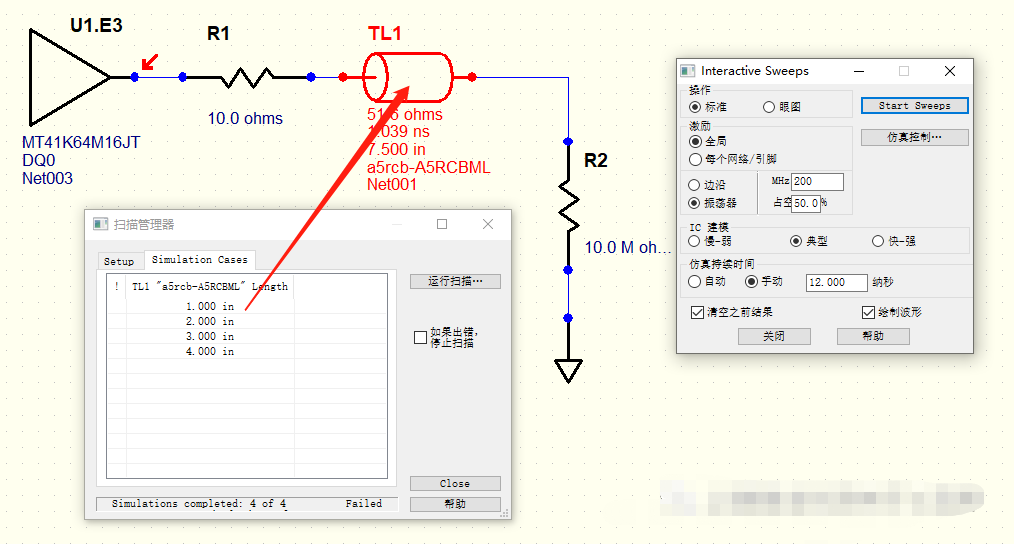

下图是对不同时延的仿真。TL1取不同的长度,造成的信号时延不同。

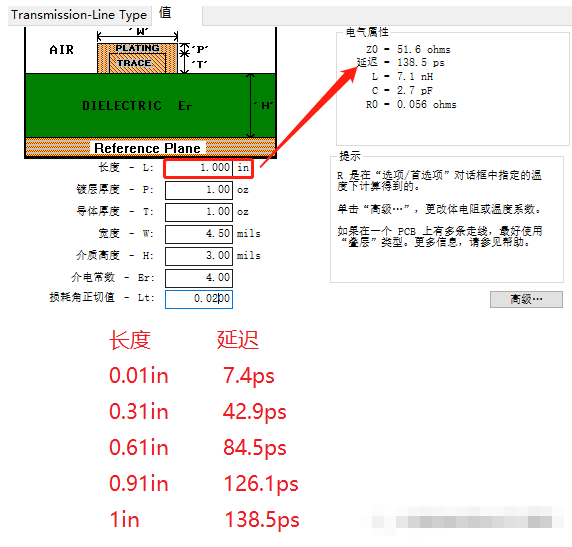

如下这种叠层的微带线,TL1不同长度对应的信号延迟分别是:

看仿真结果,长度越短,延迟越少,信号越没有振铃。

9 点对点拓扑的通用端接

振铃是由于源端和负载端阻抗突变,造成信号在两端之间来回多次反射引起的。减小任何一端的反射,都可以减小振铃噪声。控制传输线在一端或者两端的阻抗,从而减小反射的方法称为传输线的端接。通常是在传输线的某些位置放置一个或者多个电阻。

一个源端一个负载端,相互连接起来的称为点对点拓扑结构。

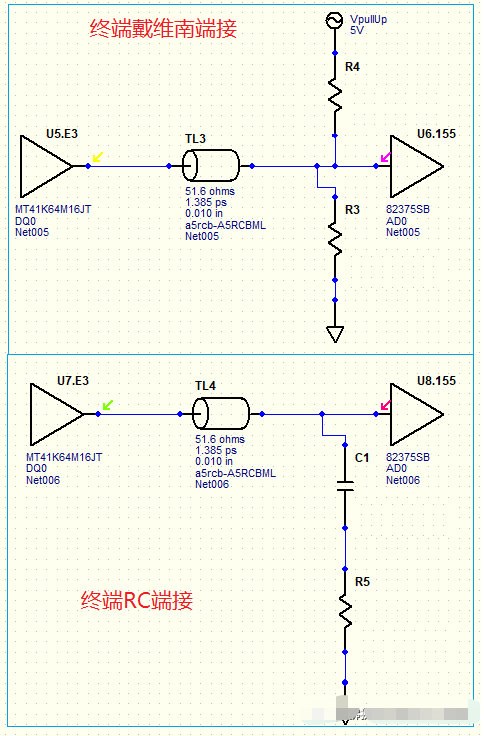

(一)下图是四种常见的端接方式。

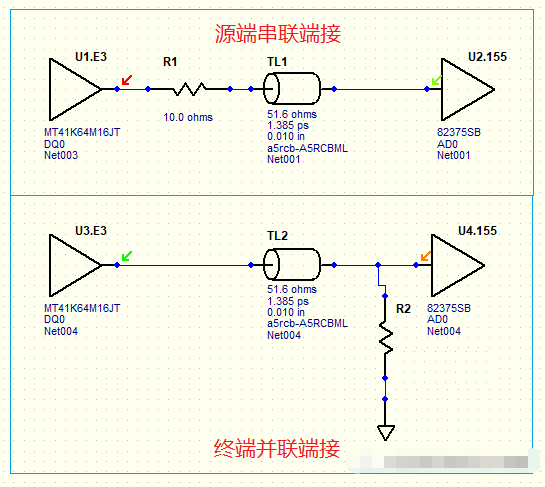

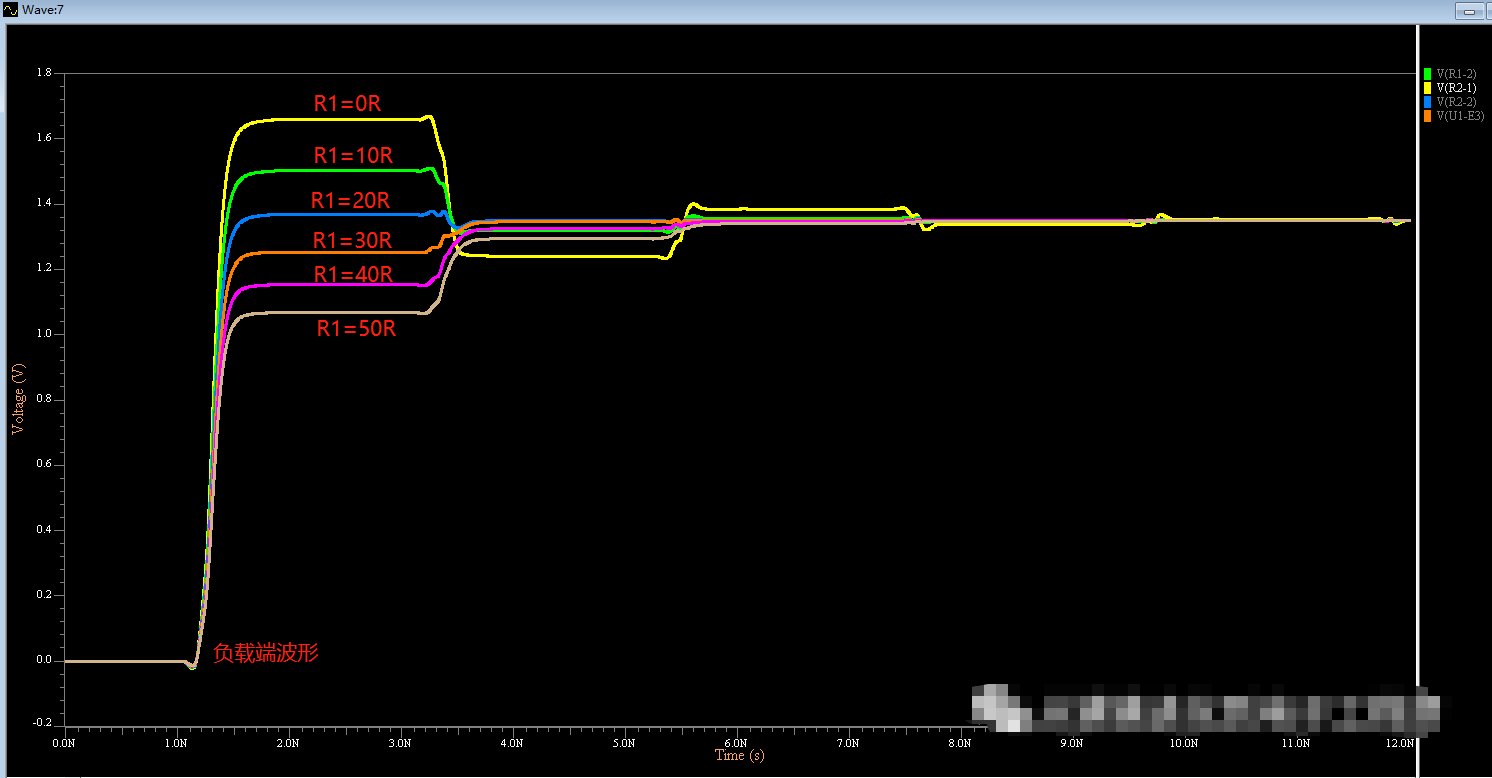

(二)源端串联端接的仿真--终端波形

针对第一种情况,如果源端内阻是10R,传输线阻抗是50R,在源端串联一个40R的电阻是合适的。例如源端输出1V的入射电压,此电源被50R总电阻和50R的传输线分压,因此有0.5V的电压进入传输线。当这0.5V的电压到达传输线的开路端时,它会被反射,产生反射电压0.5V。因此在负载端0.5V的输入电压和0.5V的反射电压,合成1V的电压。同时0.5V的反射电压向源端反射回去,在源端看到的是40R+10R的,合计50R的电阻,传输线也是50R的电阻,因此没有瞬态阻抗变化,不会发生反射。

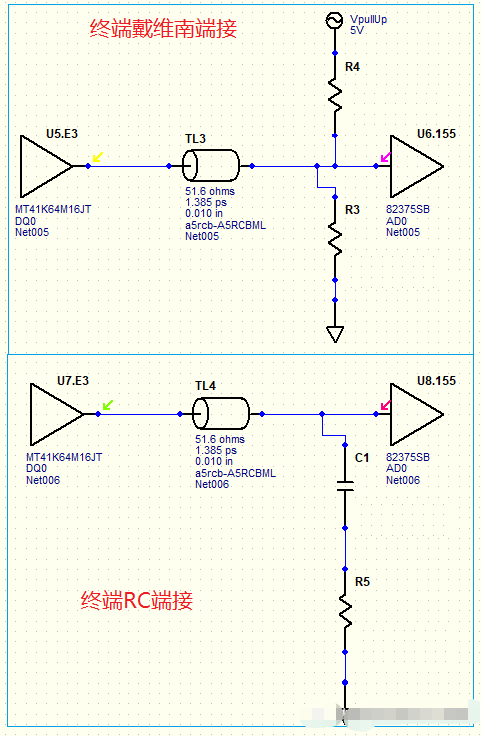

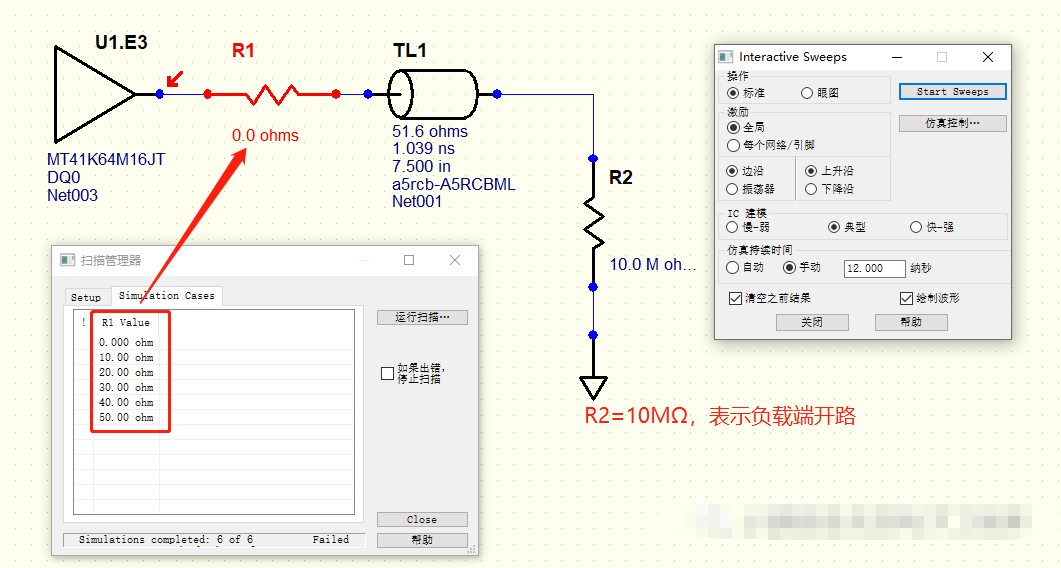

如下图是对源端串联仿真。R1分别取值0R、10R、20R、30R、40R、50R。

看仿真结果,R2=20R或者R2=30R时,负载端波形的振铃最小。如果对R1取值更精细(在20~30欧姆之间的某个值),应该可以得到振铃更小的波形。

(三)源端串联端接的仿真--源端波形

关于源端波形的台阶,分析如下。在源端的串联电阻之后测量到的初始电压正是进入传输线的入射电压,大约为信号电压的一半。源端在等待反射波的到来,只有反射波回到源端,才会使源端的总电压达到全电压摆幅。源端等待的时间就是信号往返时间。因此等待时间越久,源端串联电阻上测量到的台阶时间越长。

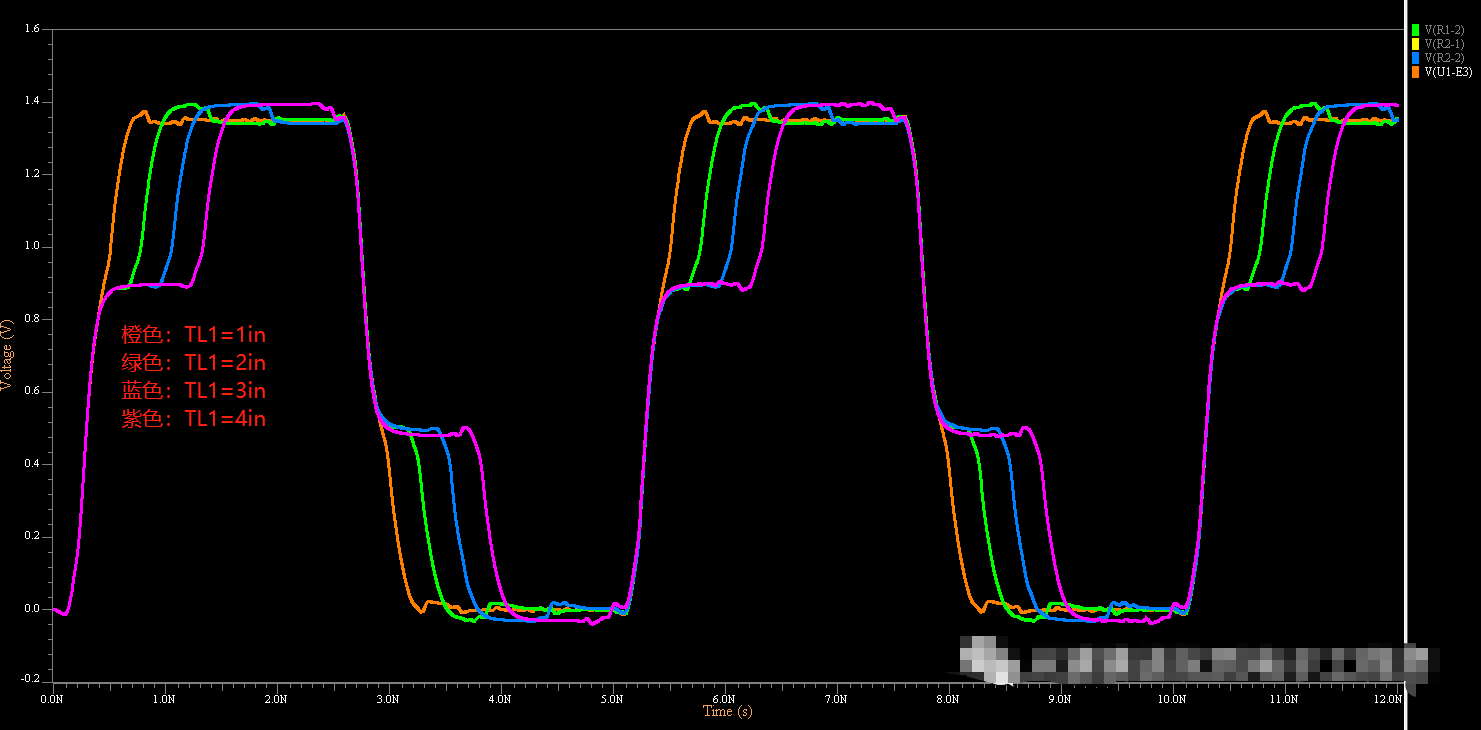

如下是仿真结果,TL1长度分别是1in、2in、3in、4in时,R1和TL1中间那个点的电压波形。

和上述论述一致,TL1越短,源端等待反射波形的时间越短,R1和TL1中间那个点的电压波形的台阶越不明显(橙色波形)。TL1越长,源端等待反射波形的时间越长,R1和TL1中间那个点的电压波形的台阶越明显(紫色波形。)

如果电路建构是点对点拓扑,源端信号上有台阶没什么关系。如果不是点对点架构,除了源端和负载端,还有第三个芯片在电路上,那么这个台阶可能会影响到第三个芯片(需要测量信号在第三个芯片管脚上的波形,才能知道第三个芯片是否被影响到?)。如果第三个芯片被影响到,源端串联端接的方案就不可行了,需要使用其他端接方式(例如终端端接)。

-

放大器

+关注

关注

146文章

14299浏览量

221010 -

信号完整性

+关注

关注

68文章

1473浏览量

97768 -

反射

+关注

关注

0文章

69浏览量

16186 -

传输线

+关注

关注

0文章

382浏览量

25360 -

DUT

+关注

关注

0文章

193浏览量

13368

发布评论请先 登录

信号完整性(五):信号反射

信号完整性简介及protel信号完整性设计指南

信号完整性之反射(三)

信号完整性之反射(三)

评论