0 信号反射的基本描述

信号沿互连线传播时,如果感受到的瞬态阻抗发生变化,则一部分信号被反射回源端,另一部分信号发生失真并且继续向负载端传输过去。这是单一信号网络中信号完整性主要的问题。反射和失真会导致信号质量下降,例如振铃。过强的振铃会超过逻辑电平的阈值,造成误触发。

信号线上的过孔、线宽变化、大的元件焊盘、接插件、连接器等都会造成瞬态阻抗突变,导致信号反射。

控制走线几何机构、减小桩线长度、使用菊花链结构、点对点拓扑结构等都对保持阻抗恒定有好处。

1 阻抗变化处的反射

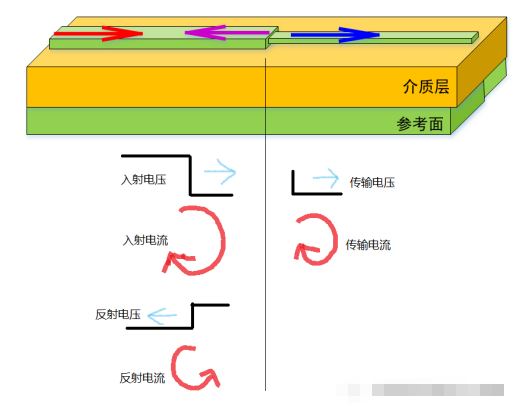

信号沿传输线传播,无论什么原因使传输线上瞬态阻抗发生变化,有一部分信号沿着与原传播方向相反的方向反射(即向源端反射回去),剩余部分将继续向负载端传播,但幅度有所改变。

有多少信号被反射回去,由瞬态阻抗的变化量决定。两个区域的阻抗差异越大,反射信号量越大,到达负载端的信号越少。下图红色是入射电压,紫色是反射电压。蓝色是反射后剩余电压,继续向前传播。Z2的区域可以不是传输线,可能是相应阻抗的元件,例如电阻、电容、电感或者它们的组合。

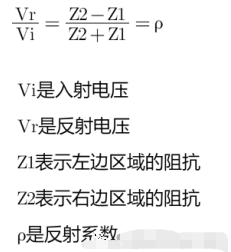

反射系数:

例如1V(Vi)的入射电压顺着50R阻抗(Z1)的传输线传播,当到达传输线变窄的区域,阻抗变大到75R(Z2),计算可知反射系数是20%,反射电压是0.2V。无论波形是什么形状,只要到达Z1和Z2的交界处,波形的各个部分都有20%的波形被反射回去。

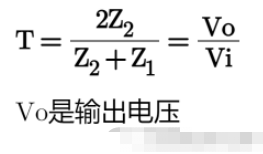

传输系数:

2 反射是怎么形成的?

那么究竟是什么造成信号在两个阻抗不同区域交界处发生反射呢?假设信号在区域1中的电压和电流是V1和I1,信号在区域2中的电压和电流是V2和I2。理论上在交界处的两侧电压和电流应该是相同的,即V1=V2,I1=I2,Z1=Z2。当交界处两侧的阻抗不同时,为了使整个系统协调稳定,在区域1产生一个反射回源端的电压。它唯一的目的就是吸收入射信号传输信号之间不匹配的电压和电流。

为了减小信号反射造成的信号完整性问题,如下四个设计要点需要注意

(1)使用阻抗可控的传输线

(2)传输线末端至少有一个终端匹配

(3)设计使多分枝产生影响最小的布线拓扑结构

(4)最小化几何结构的不连续性

3 阻性负载的反射

传输线的终端匹配有三种特殊情况:开路、短路、终端阻抗和传输线阻抗匹配。

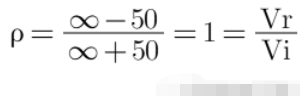

情况一:终端开路(假设传输线阻抗是50R)

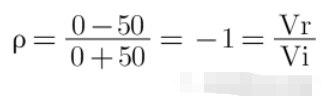

当传输线终端开路,则传输线模末端的瞬态阻抗是无群大,此时反射系数是:

即当信号到达传输线的终端时,在终端将产生与入射波大小相同,方向相反,返回源端的反射波。

情况二:终端短路(假设传输线阻抗是50R)

当传输线终端短路,则传输线模末端的瞬态阻抗是0,此时反射系数是:

即1V入射信号到达远端时,将产生-1V反射信号,向源端传播。短路突变处的电压为入射电压和反射电压之和,即1V-(-1V)=0V。

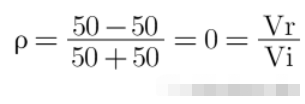

情况三:终端阻抗和传输线阻抗匹配

当终端阻抗和传输线阻抗匹配时,此时反射系数为:

没有反射信号,终端电阻两端的电压就是入射信号。

总之:当末端为一般性阻性负载时,信号在终端感受到的瞬态阻抗在0~无群大之间,反射系数在1~-1之间。

例子

例子一

Vi=1V,Z1=50R,Z2=25R

反射系数=(25-50)/(25+50)=-0.33

Vr=Vix-0.33=-0.33V

传输系数=2x25/50+25=0.66

Vo=Vix0.66=0.66V

即当信号线变窄时,Vo会减小。

例子二

Vi=1V,Z1=25R,Z2=50R

反射系数=(50-25)/(50+25)=0.33

Vr=Vix0.33=0.33V

传输系数=2x50/50+25=1.33

Vo=Vix1.336=1.33V

当信号线变宽时,Vo会增大。

-

信号

+关注

关注

11文章

2902浏览量

79664 -

信号完整性

+关注

关注

68文章

1473浏览量

97768 -

反射

+关注

关注

0文章

69浏览量

16186 -

传输线

+关注

关注

0文章

382浏览量

25360 -

焊盘

+关注

关注

6文章

597浏览量

39571

发布评论请先 登录

信号完整性(五):信号反射

信号完整性简介及protel信号完整性设计指南

信号完整性之反射(一)

信号完整性之反射(一)

评论