10 传输线中某一段传输线宽度和阻抗变化对反射的影响

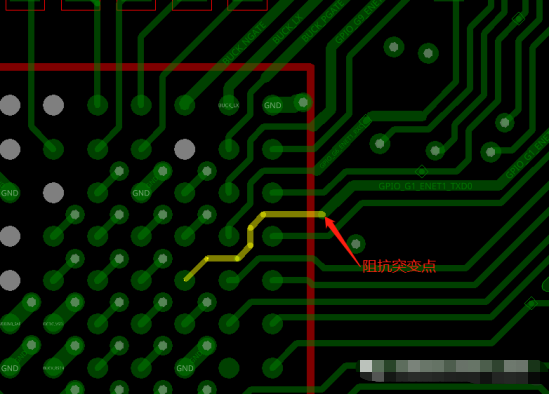

现在的芯片管脚越来越多,管脚间距越来越小。有些走线即使想做阻抗控制,也受限于芯片管脚数和管脚间距,在芯片下方走线不得不变窄。当这些走线从芯片下方走出来后,宽度又会恢复到阻抗要求的值。如下图所示,黄色部分的走线是在SOC下方(红框中)走过,线宽比较窄。走出SOC之后(红框外面),走线变粗。在走线宽度变化点,就是阻抗突变点。

走线变窄,阻抗变大。走线变宽,阻抗变小。

问题来了,多长的线段、多大的阻抗变化会造成信号完整性问题呢?针对这个问题,有三个因素影响信号完整性,这段阻抗突变走线的长度、阻抗突变的阻抗值、传输在这段走线上的信号上升时间。

(一)传输线阻抗偏差(阻抗突变)对信号的影响

上一篇提到过,希望反射信号(噪声)要小于电压摆幅5%。想达到这个目的,就需要保证传输线特性阻抗变化率小于10%。这也是为什么很多芯片的design guide中要求高速信号阻抗控制的公差是±10%的原因。

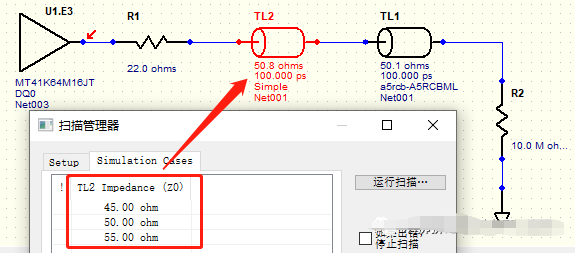

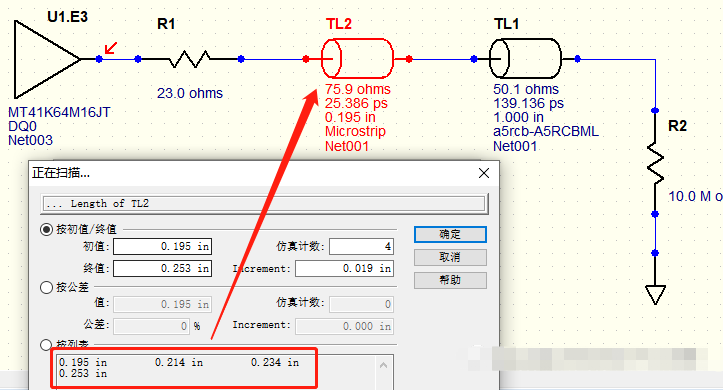

如下仿真电路,在源端和负载端之间有两段串联的传输线组成,即TL2和TL1。TL2类似上图中在芯片下方宽度较窄的走线。TL1类似红框外面,正常宽度(50R阻抗控制)的走线。通过仿真,调整TL2的阻抗,看看TL2的阻抗突变对信号有什么影响。首先将TL2的阻抗控制在50R±10%

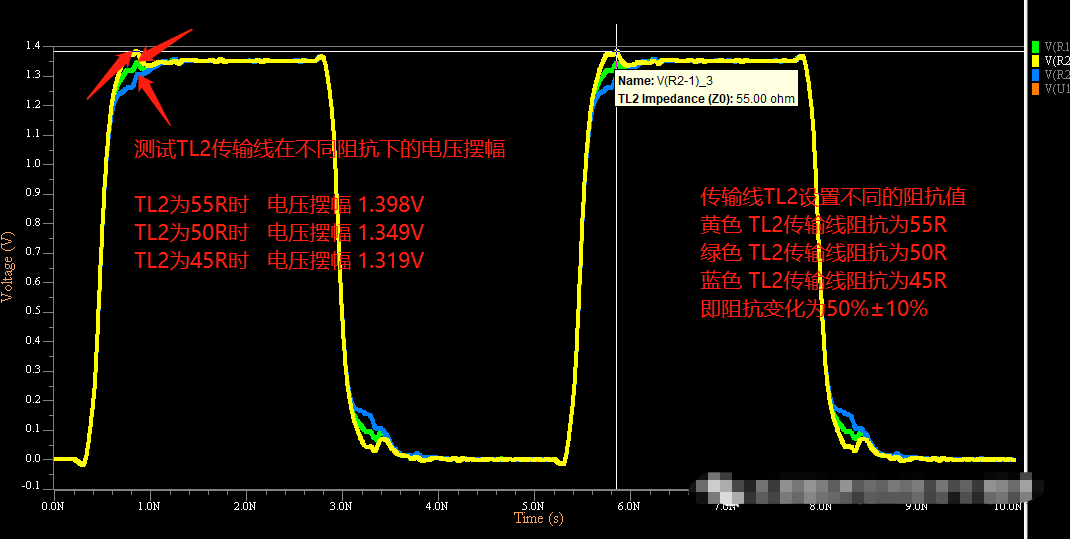

本仿真电路中,电压标准摆幅是1.35V(因为是LPDDR3),那么电压摆幅的±5%分别为

上限:1.35+1.35x5%=1.4175V

下限:1.35-1.35x5%=1.2825V

即信号振荡(包括振铃)不超过这两个限值即可。

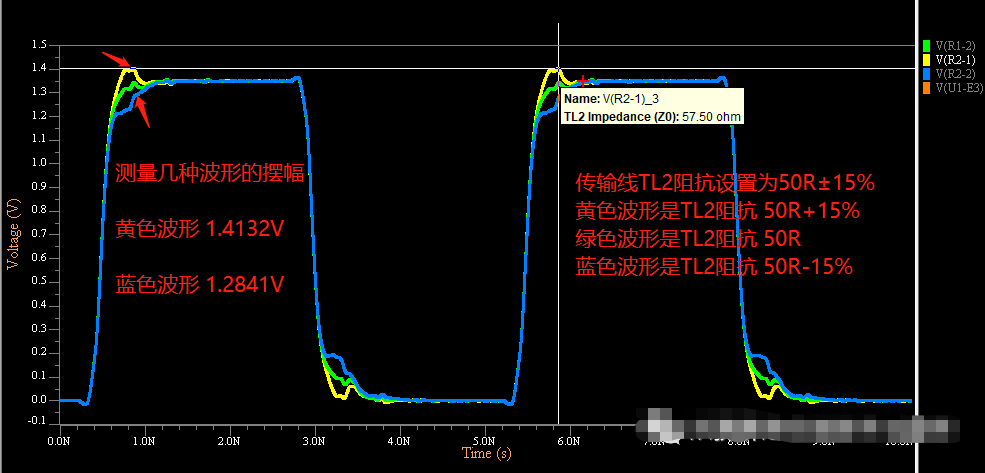

如下为TL2传输线阻抗分别设置为55R,50R和45R时的仿真结果。可以看到TL2传输线阻抗控制在±10%时,虽然有振荡,仿真结果显示的电压摆幅都在1.35V的±5%之内。

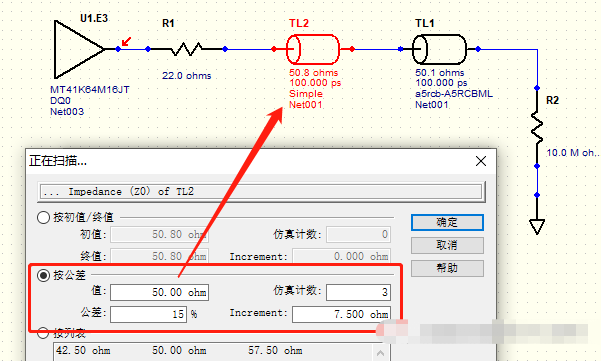

接下来,如下图,将TL2传输线阻抗调大到50R±15%。

可以看到TL2传输线阻抗为57.5R或者42.5R时,信号摆幅已经很接近1.35±5%的限值。考虑到实际的PCB生产中,实物并非如理论那般精确(例如理论上一条导线是根长方体,即上下一样宽。实际PCB生产时,一条导线的上边比下边窄,是一种梯形体)。实际信号摆幅很有可能会超过5%的限值。因此阻抗控制在Z0±10%之内,是我们在设计中要遵守的一个规则。

(二)有阻抗偏差的传输线长度对信号的影响

阻抗突变线(本文开头那张图,红色框中芯片下方,宽度变窄的走线)越短,反射对信号完整性的影响越小。那么问题是,这段走线多短,才不会影响信号完整性呢。和上一篇中提到的结果一样,当时延小于上升时间的20%时,反射几乎看不见。当时延超过上升时间的20%时,振铃就会明显了。因此当时延TD>Tr x 20%时,这段阻抗突变线对信号完整性的影响就比较大了。

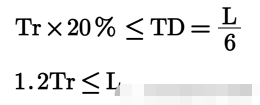

例如某信号的上升时间是Tr(ns),某段走线的长度时L(in),因为针对FR4的走线,信号速度是6in/ns,信号延迟是TD,因此

经验结论是:即当走线长度L大于1.2倍的Tr时,这段走线会影响信号完整性。当走线长度L小于1.2倍的Tr时,这段走线对信号完整性的影响比较小。

如下是电路仿真,设置信号频率是200MHz

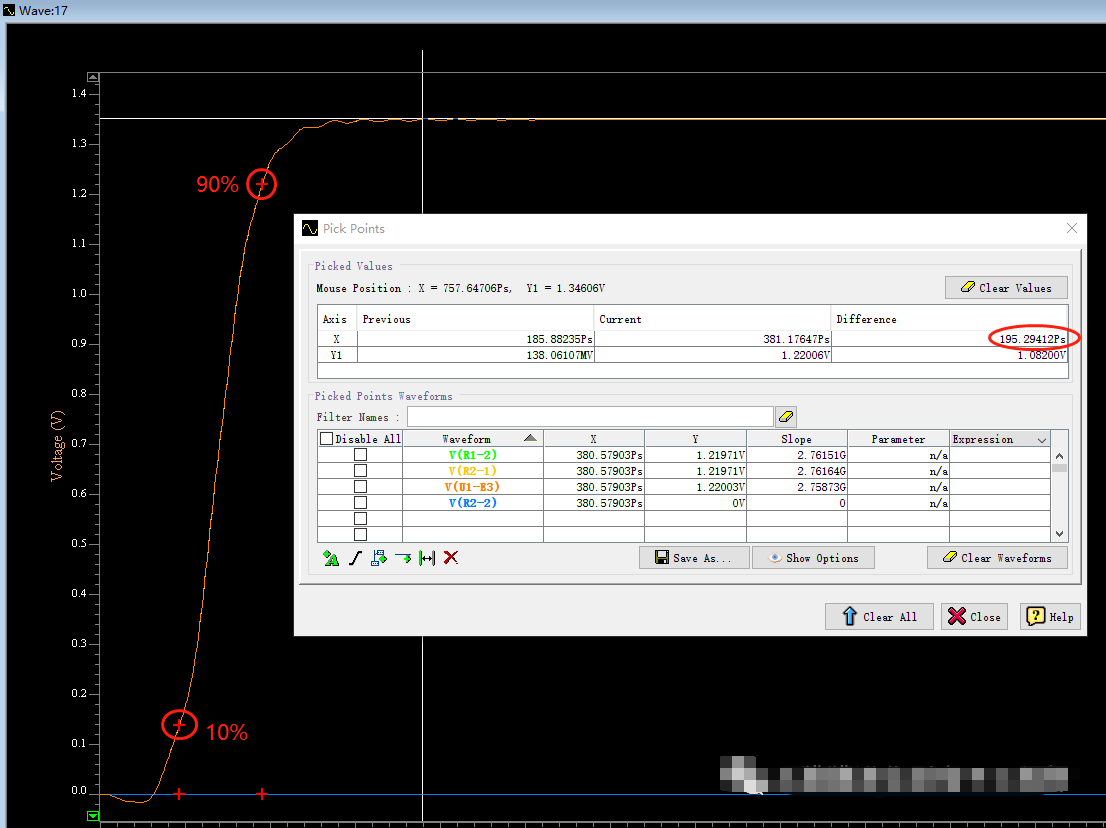

首先测量信号的上升时间(注:有些芯片的IBIS模型中会给出上升时间)。我使用的这颗芯片,是仿真软件自带的IBIS模型。在其中没有找到相关参数,因此我试着自己测量它的上升时间。按照10%~90%的电压振幅,测量上升时间如下图大约在195ps,即0.195ns

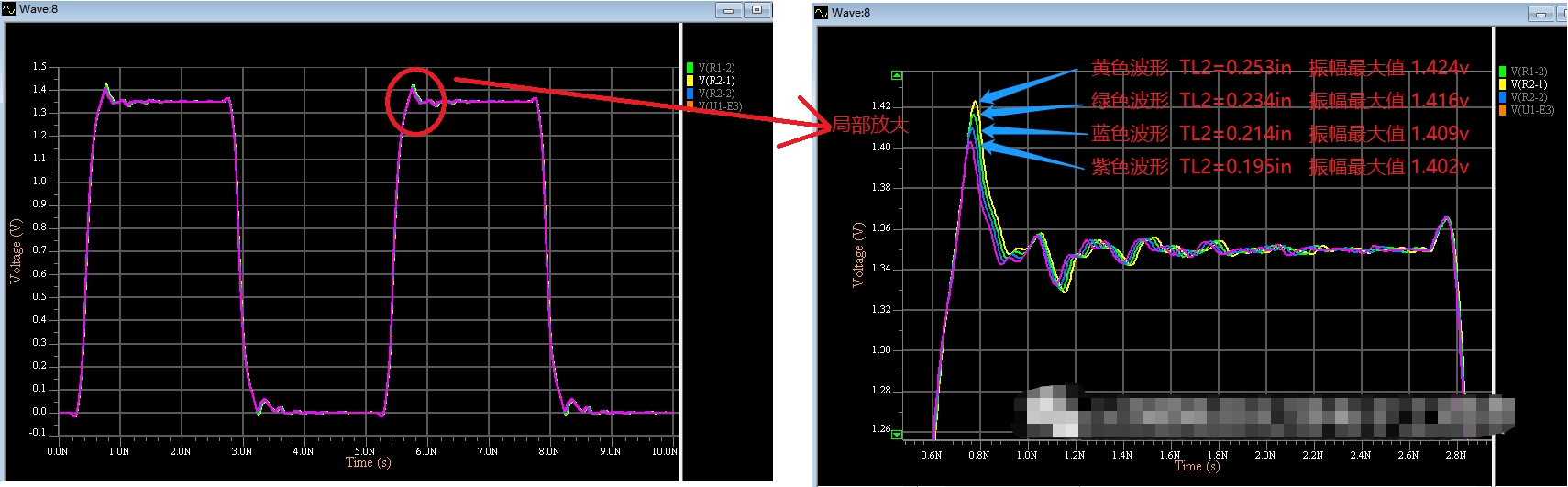

按照经验公式,当TL2的长度L>信号上升时间的1.2倍时,即当TL2的长度达到0.234in时,这段阻抗突变的走线就会影响信号质量了。

本次仿真信号上升时间Tr=0.195ns,Tr的1.x倍如下:

Tr x 1=0.195

Tr x 1.1=0.214

Tr x 1.2=0.234

Tr x 1.3=0.253

设计仿真电路,调整TL2的长度,分别为0.195/0.214/0.234/0.253in,看看结果是什么。

仿真结果如下:

按照要求,按照电压摆幅不能超过5%,

上限:1.35+1.35x5%=1.4175V

下限:1.35-1.35x5%=1.2825V

当TL2的长度是Tr上升时间的1.2倍时,仿真波形的电压摆幅已经很接近极限值。当TL2的长度是Tr上升时间的1.3倍时,仿真波形的电压摆幅超过极限值。

本文结论:因此针对本文的话题,传输线中某一段走线阻抗突变了,为了使这段阻抗突变走线不至于影响信号质量,需要:

(1)阻抗突变控制在目标阻抗的±10%以内

(2)阻抗突变的走线长度不超过信号上升时间的1.2倍,最好是阻抗突变的走线长度不超过信号上升时间的1倍。此处走线长度单位是in,信号上升时间单位是ns。

注:就我的理解(不一定准确),以上两个条件满足其中任何一个,都对信号质量有好的改善。当然两个都做到最好。

-

soc

+关注

关注

38文章

4514浏览量

227642 -

信号

+关注

关注

11文章

2902浏览量

79679 -

信号完整性

+关注

关注

68文章

1473浏览量

97773 -

管脚

+关注

关注

1文章

230浏览量

33461 -

传输线

+关注

关注

0文章

382浏览量

25362

发布评论请先 登录

信号完整性(五):信号反射

信号完整性分析

信号完整性简介及protel信号完整性设计指南

信号完整性之反射(四)

信号完整性之反射(四)

评论