电子发烧友网报道(文/周凯扬)自从2.5D/3D封装、Chiplet、异构集成等技术出现以来,CPU、GPU和内存之间的界限就已经变得逐渐模糊。单个SoC究竟集成了哪些逻辑单元和存储单元,全凭借厂商自己的设计路线。这样的设计其实为单芯片的能效比带来了一轮新的攀升,但也极大地增加了开发难度。即便如此,还是有不少厂商在不遗余力地朝这个方向发展,最典型的莫过于AMD。

AMD的存储堆叠之路

要说玩堆叠存储,AMD确实是走得最靠前的一位,例如AMD如今在消费级和数据中心级别CPU上逐渐使用的3D V-Cache技术,就是直接将SRAM缓存堆叠至CPU上。将在今年正式落地的第四代EPYC服务器处理器,就采用了13个5nm/6nm Chiplet混用的方案,最高将L3缓存堆叠至了可怕的384MB。

在消费端,AMD的Ryzen 7 5800X3D同样也以惊人的姿态出世,以超大缓存带来了极大的游戏性能提升。即将正式发售的Ryzen 9 7950X3D也打出了128MB三级缓存的夸张参数,这些产品的出现可谓打破了过去CPU厂商拼时钟频率、拼核心数的僵局,让消费者真切地感受到了额外的体验提升。

MI300 APU / AMD

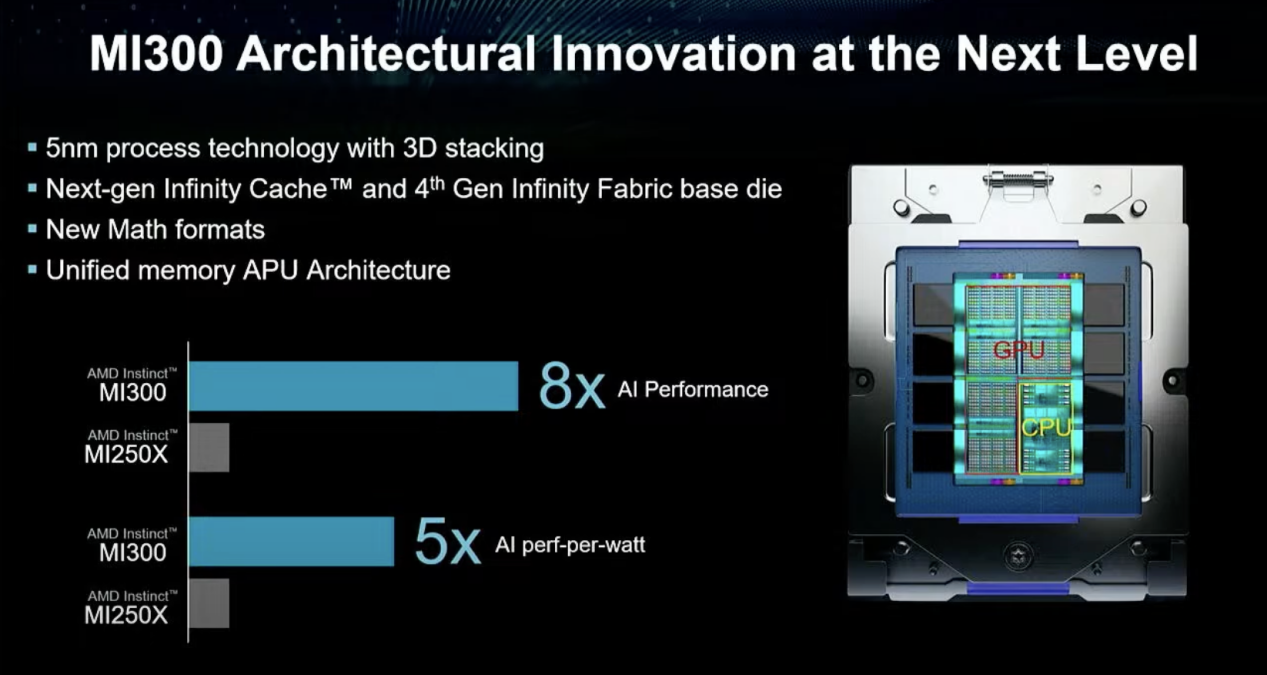

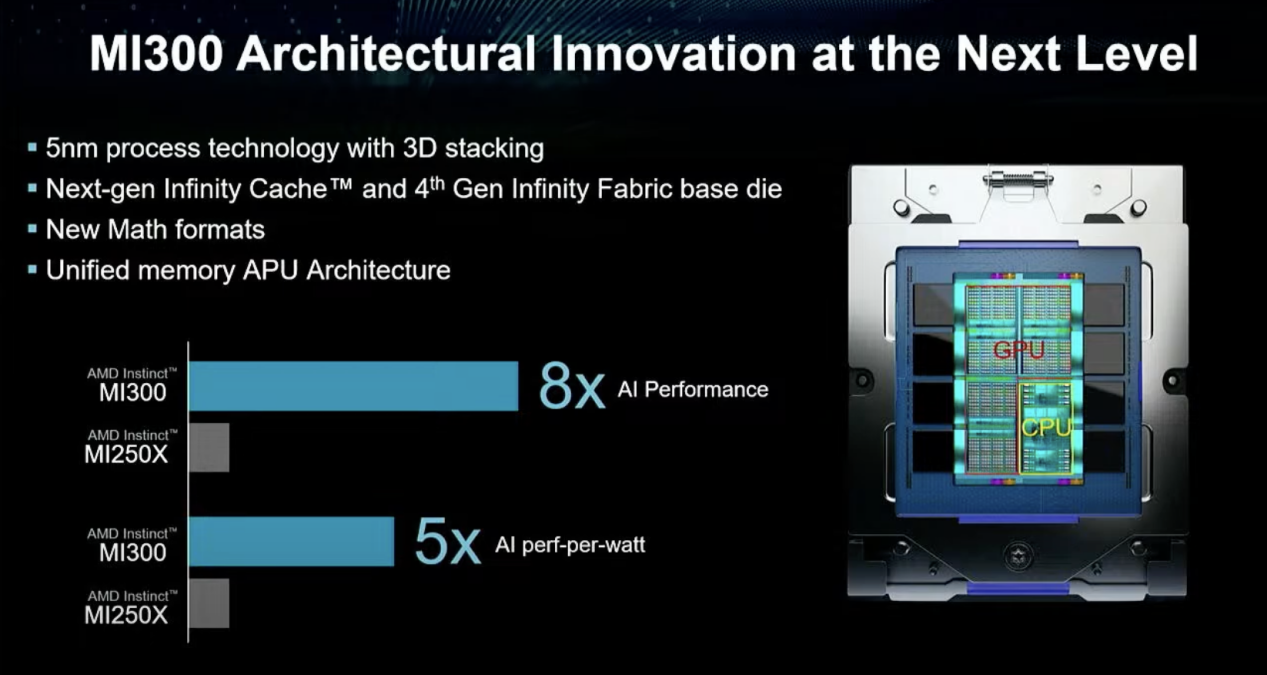

GPU也不例外,虽然AMD如今的消费级GPU基本已经放弃了HBM堆叠方案,但是在AMD的数据中心GPU,例如Instinct MI250X,却依然靠着堆叠做到了128GB的HBM2e显存,做到了3276.8GB/s的峰值内存带宽。而下一代MI300,AMD则选择了转向APU方案,将CPU、GPU和HBM全部整合在一起,以新的架构冲击Exascale级的AI世代。

其实这也是AMD收购Xilinx最大的收获之一,早在十多年前Xilinx的3DIC技术也已经为多Die堆叠打下了基础。在收购Xilinx之际,AMD也提到这次交易会扩张AMD在die堆叠、封装、Chiplet和互联技术上的开发能力。在完成Xilinx的收购后,也可以看出AMD在架构上的创新有了很大的飞跃。

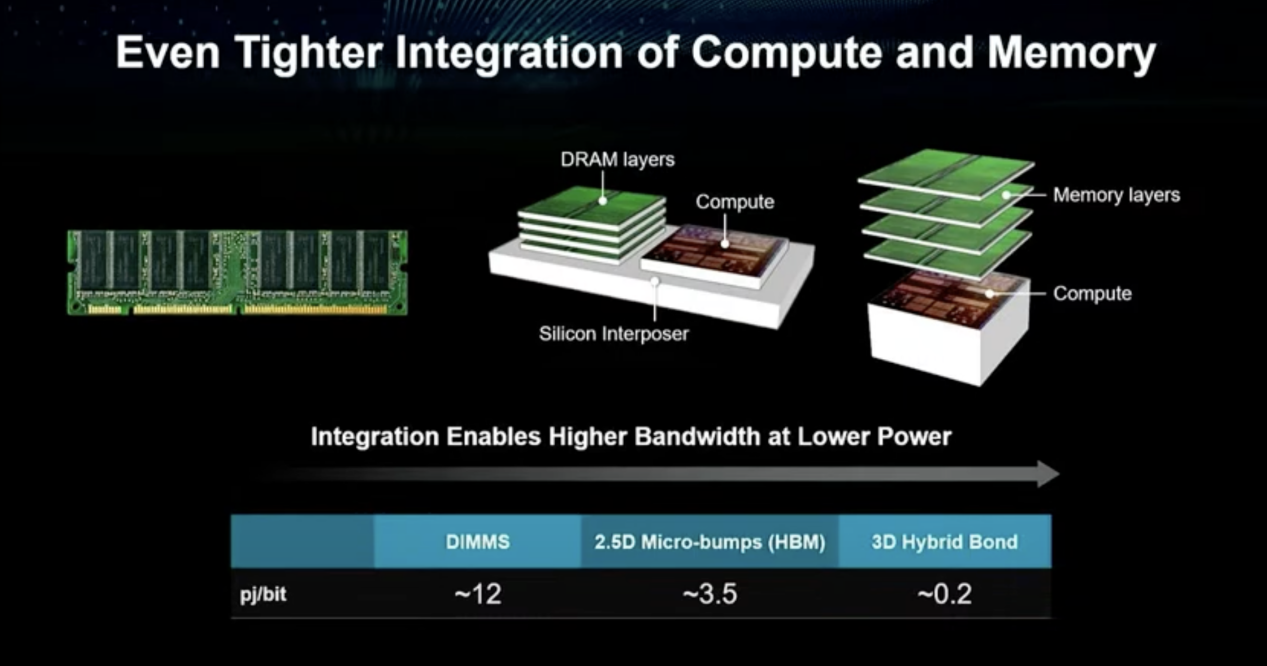

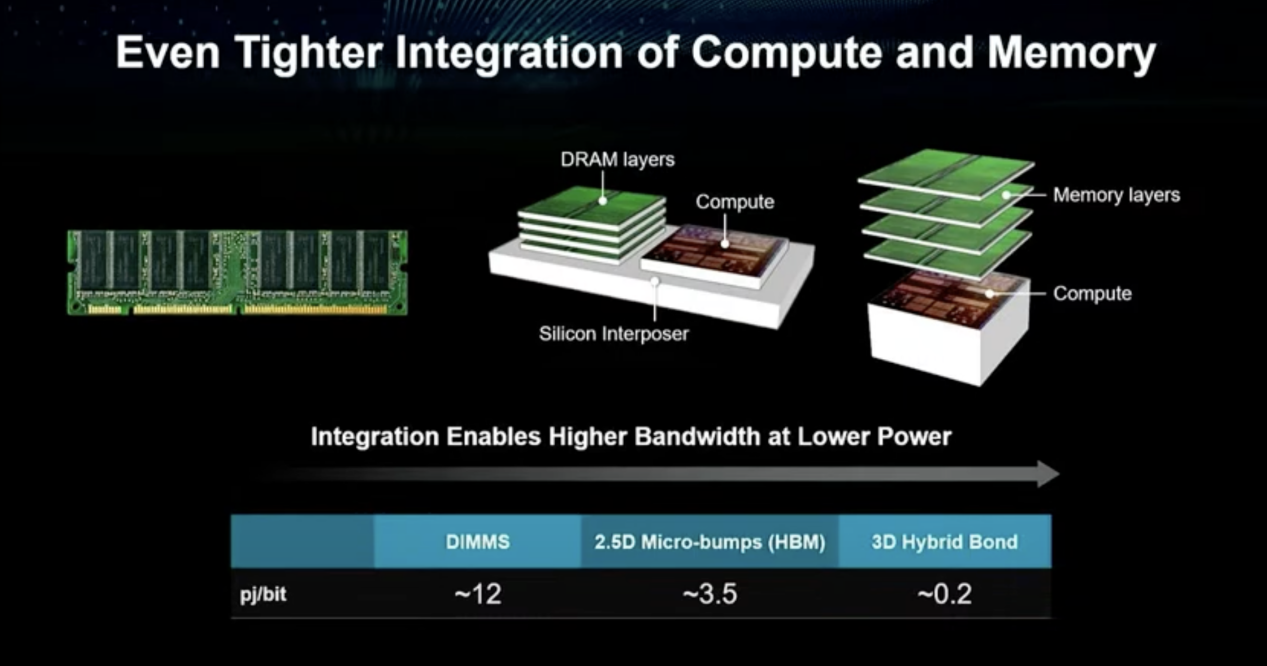

在近期的ISSCC 2023上,AMD CEO苏姿丰透露了他们的下一步野心,那就是直接将DRAM堆叠至CPU上。这里的堆叠并非硅中介层互联、存储单元垂直堆叠在一起的2.5D封装方案,也就是如今常见的HBM统一内存方案,AMD提出的是直接将计算单元与存储单元垂直堆叠在一起的3D混合键封装方案。

CPU与DRAM垂直堆叠

主流服务器性能的提升速度,已经快要赶上过去的摩尔定律了。根据AMD统计的CPU供应商数据,每过2.4年主流服务器性能就会翻一倍。可限制其继续发展的不再只是放缓的摩尔定律,还有内存上带来的限制。内存墙这样的性能瓶颈,不仅在限制CPU的性能发挥,同样限制了GPU的性能发挥。

考虑到明面上解决这个问题的主力军是存储厂商,所以提出的大部分创新方案,例如存内计算等等,也都是创造算力更高的存储器产品。苏姿丰博士也指出,从她这个处理器从业者的角度来说,这一路线有些反常理,但从系统层面来说,她也可以理解该需求存在的意义。而AMD这次提出的方案,则是从计算芯片出发,将存储器堆叠整合进去。

CPU与DRAM垂直堆叠 / AMD

从AMD给出的能量效率分析来看,DIMM这样的片外内存访问能量效率在12pj/bit左右,2.5D的HBM方案在3.5pj/bit左右,而3D垂直堆叠的键合方案却可以做到0.2pj/bit,从而利用更低的功耗来做到大带宽。况且由于计算单元和存储单元的集成度更高了,传输的延迟必然也会有显著的降低。

这套方案的出现意味着至少堆叠的内存容量足够大,服务器CPU甚至可以省去DIMM内存插槽,进一步减小空间占用。但这套方案具体能做堆叠多少内存,AMD并没有给出具体的数字,如果可堆叠的内存数量与如今的L3缓存一样仅有数百兆的话,那带来的性能提升很可能不值一提。

另外就是散热问题,从AMD给出的示意图来看,他们选择了内存单元在上,计算单元在下的方案,这种3D架构很可能会对散热产生一定负面作用,但性能损失会相对较少一些。比如MI300方案中,AMD就换成了CPU和GPU单元在上,缓存和互联在下的方案。

捆绑销售嫌疑?

在消费级领域,其实CPU与内存捆绑销售已经不是什么新鲜事了,就拿苹果的M系列芯片为例。自打苹果转向Arm阵营,推出M系列芯片后,Mac生态的定制空间就基本只存在于购买前了,虽然华强北的大神们依然能够找到一些方式来扩展固态硬盘闪存,但内存基本就与SoC彻底绑定了,用户只能忍受高昂的容量定价,才不会在高负载工作时出现内存不够用的窘境。

可在服务器市场,已经有了相当成熟的DIMM内存生态,甚至未来还有CXL内存虎视眈眈,AMD这套“捆绑销售”的方案究竟能否收获良好的市场反响我们无从得知,很明显这对内存模组厂商是存在一定威胁的。但话又说回来,AMD这套方案并没有彻底断绝扩展内存的可能性,在需要超大容量的内存池时,依然可以选择传统的扩展方案,而不是死磕堆叠内存的方案。

AMD的方案更像是给到了一个片上高速方案,从当下的工艺来看,应该还难以实现大容量的堆叠。所以在CPU上垂直堆叠DRAM,更像是AMD的另一套负载加速方案。毕竟根据苏姿丰博士的说法,AMD也很清楚现有的3D V-Cache SRAM堆叠方案只能提高特定负载的性能,DRAM堆叠方案的性能加速覆盖面无疑要更广一些。

写在最后

其实ChatGPT这样的应用出现,不仅带动了一波GPU订单量的狂飙,也让HBM、DDR5这些大带宽的内存有了用武之地,让人们终于看到了打破内存墙的应用价值,而不只是将其视为一个徒增成本的性能瓶颈。

而AMD虽然提出了将内存堆叠至CPU上的技术路线,也并没有放弃对其他方案的考量,比如他们也在和三星展开HBM2上的存算一体研究。如果AMD选择将CPU堆叠内存与存算一体结合在一起的话,或许会给其数据中心产品带来更大的优势。

AMD的存储堆叠之路

要说玩堆叠存储,AMD确实是走得最靠前的一位,例如AMD如今在消费级和数据中心级别CPU上逐渐使用的3D V-Cache技术,就是直接将SRAM缓存堆叠至CPU上。将在今年正式落地的第四代EPYC服务器处理器,就采用了13个5nm/6nm Chiplet混用的方案,最高将L3缓存堆叠至了可怕的384MB。

在消费端,AMD的Ryzen 7 5800X3D同样也以惊人的姿态出世,以超大缓存带来了极大的游戏性能提升。即将正式发售的Ryzen 9 7950X3D也打出了128MB三级缓存的夸张参数,这些产品的出现可谓打破了过去CPU厂商拼时钟频率、拼核心数的僵局,让消费者真切地感受到了额外的体验提升。

MI300 APU / AMD

GPU也不例外,虽然AMD如今的消费级GPU基本已经放弃了HBM堆叠方案,但是在AMD的数据中心GPU,例如Instinct MI250X,却依然靠着堆叠做到了128GB的HBM2e显存,做到了3276.8GB/s的峰值内存带宽。而下一代MI300,AMD则选择了转向APU方案,将CPU、GPU和HBM全部整合在一起,以新的架构冲击Exascale级的AI世代。

其实这也是AMD收购Xilinx最大的收获之一,早在十多年前Xilinx的3DIC技术也已经为多Die堆叠打下了基础。在收购Xilinx之际,AMD也提到这次交易会扩张AMD在die堆叠、封装、Chiplet和互联技术上的开发能力。在完成Xilinx的收购后,也可以看出AMD在架构上的创新有了很大的飞跃。

在近期的ISSCC 2023上,AMD CEO苏姿丰透露了他们的下一步野心,那就是直接将DRAM堆叠至CPU上。这里的堆叠并非硅中介层互联、存储单元垂直堆叠在一起的2.5D封装方案,也就是如今常见的HBM统一内存方案,AMD提出的是直接将计算单元与存储单元垂直堆叠在一起的3D混合键封装方案。

CPU与DRAM垂直堆叠

主流服务器性能的提升速度,已经快要赶上过去的摩尔定律了。根据AMD统计的CPU供应商数据,每过2.4年主流服务器性能就会翻一倍。可限制其继续发展的不再只是放缓的摩尔定律,还有内存上带来的限制。内存墙这样的性能瓶颈,不仅在限制CPU的性能发挥,同样限制了GPU的性能发挥。

考虑到明面上解决这个问题的主力军是存储厂商,所以提出的大部分创新方案,例如存内计算等等,也都是创造算力更高的存储器产品。苏姿丰博士也指出,从她这个处理器从业者的角度来说,这一路线有些反常理,但从系统层面来说,她也可以理解该需求存在的意义。而AMD这次提出的方案,则是从计算芯片出发,将存储器堆叠整合进去。

CPU与DRAM垂直堆叠 / AMD

从AMD给出的能量效率分析来看,DIMM这样的片外内存访问能量效率在12pj/bit左右,2.5D的HBM方案在3.5pj/bit左右,而3D垂直堆叠的键合方案却可以做到0.2pj/bit,从而利用更低的功耗来做到大带宽。况且由于计算单元和存储单元的集成度更高了,传输的延迟必然也会有显著的降低。

这套方案的出现意味着至少堆叠的内存容量足够大,服务器CPU甚至可以省去DIMM内存插槽,进一步减小空间占用。但这套方案具体能做堆叠多少内存,AMD并没有给出具体的数字,如果可堆叠的内存数量与如今的L3缓存一样仅有数百兆的话,那带来的性能提升很可能不值一提。

另外就是散热问题,从AMD给出的示意图来看,他们选择了内存单元在上,计算单元在下的方案,这种3D架构很可能会对散热产生一定负面作用,但性能损失会相对较少一些。比如MI300方案中,AMD就换成了CPU和GPU单元在上,缓存和互联在下的方案。

捆绑销售嫌疑?

在消费级领域,其实CPU与内存捆绑销售已经不是什么新鲜事了,就拿苹果的M系列芯片为例。自打苹果转向Arm阵营,推出M系列芯片后,Mac生态的定制空间就基本只存在于购买前了,虽然华强北的大神们依然能够找到一些方式来扩展固态硬盘闪存,但内存基本就与SoC彻底绑定了,用户只能忍受高昂的容量定价,才不会在高负载工作时出现内存不够用的窘境。

可在服务器市场,已经有了相当成熟的DIMM内存生态,甚至未来还有CXL内存虎视眈眈,AMD这套“捆绑销售”的方案究竟能否收获良好的市场反响我们无从得知,很明显这对内存模组厂商是存在一定威胁的。但话又说回来,AMD这套方案并没有彻底断绝扩展内存的可能性,在需要超大容量的内存池时,依然可以选择传统的扩展方案,而不是死磕堆叠内存的方案。

AMD的方案更像是给到了一个片上高速方案,从当下的工艺来看,应该还难以实现大容量的堆叠。所以在CPU上垂直堆叠DRAM,更像是AMD的另一套负载加速方案。毕竟根据苏姿丰博士的说法,AMD也很清楚现有的3D V-Cache SRAM堆叠方案只能提高特定负载的性能,DRAM堆叠方案的性能加速覆盖面无疑要更广一些。

写在最后

其实ChatGPT这样的应用出现,不仅带动了一波GPU订单量的狂飙,也让HBM、DDR5这些大带宽的内存有了用武之地,让人们终于看到了打破内存墙的应用价值,而不只是将其视为一个徒增成本的性能瓶颈。

而AMD虽然提出了将内存堆叠至CPU上的技术路线,也并没有放弃对其他方案的考量,比如他们也在和三星展开HBM2上的存算一体研究。如果AMD选择将CPU堆叠内存与存算一体结合在一起的话,或许会给其数据中心产品带来更大的优势。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

amd

+关注

关注

25文章

5647浏览量

139001 -

DRAM

+关注

关注

40文章

2373浏览量

188119

发布评论请先 登录

相关推荐

热点推荐

东芝硬盘率先完成12盘片堆叠技术验证 预计在2027年推出新一代40TB硬盘

东芝硬盘率先完成 12盘片堆叠技术验证 – 预计在2027年推出新一代40TB硬盘 – 日本川崎2025年10月14日 东芝电子元件及存储装置株式会社(简称“东芝”)成为首位[1] 成功验证

新一代嵌入式开发平台 AMD嵌入式软件和工具2025.1版现已推出

AMD 2025.1 版嵌入式软件和工具是面向新一代嵌入式系统开发而打造的综合平台,全面加速概念构想到部署落地。 2025.1 版嵌入式软件和工具的新 增功能 AMD 嵌入式开发框架( EDF

新一代高效电机技术—PCB电机

纯分享帖,点击下方附件免费获取完整资料~~~

*附件:新一代高效电机技术—PCB电机.pdf

内容有帮助可以关注、点赞、评论支持一下,谢谢!

【免责声明】本文系网络转载,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请第

发表于 07-17 14:35

DRAM代际交替中的技术赋能:德明利新一代高性能内存方案

DRAM内存市场“代际交接”关键时刻2025年PC及服务器市场中,DDR4的渗透率约为20%-30%,而DDR5的渗透率约为70%-80%(TrendForce集邦咨询)。在AI算力爆发和先进

富瀚微新一代双摄MC632X系列概述

富瀚微新一代双摄MC632X系列,采用全新内存优化引擎,64MB轻松实现双摄400万,助力客户应对视觉多目化趋势。

美光宣布 1γ DRAM 开始出货:引领内存技术突破,满足未来计算需求

率先向生态系统合作伙伴及特定客户出货专为下一代 CPU 设计的 1γ(1-gamma)第六代(10 纳米级)DRAM 节点 DDR5 内存样

发表于 02-26 13:58

•475次阅读

新思科技推出基于AMD芯片的新一代原型验证系统

近日,新思科技宣布推出全新基于AMD Versal™ Premium VP1902自适应系统级芯片(SoC)的HAPS®原型验证系统,以此进一步升级其硬件辅助验证(HAV)产品组合。 此次推出的全新一代

嘉合劲威研发新一代AI专用内存MRDIMM

深圳市嘉合劲威电子科技有限公司(简称“嘉合劲威”)正在积极研发一款专为AI专业应用设计的新一代内存产品——MRDIMM。这款产品的诞生,旨在通过技术创新,为AI运算提供更加高效、经济的

2025年Q1 DRAM内存市场步入淡季,价格预计下滑

近日,据TrendForce最新分析,2025年第一季度,DRAM内存市场将进入传统淡季阶段。受智能手机等终端设备需求持续萎缩的影响,加之部分产品已提前进行库存备货,预计明年一般型

佰维存储发布新一代LPDDR5X内存与DDR5内存模组

近日,存储领域的领先企业佰维存储推出了其新一代高效能内存——LPDDR5X。这款内存产品采用了先进的1bnm制程工艺,相较于上一代产品,其数据传输速率有了显著提升,高达8533Mbps

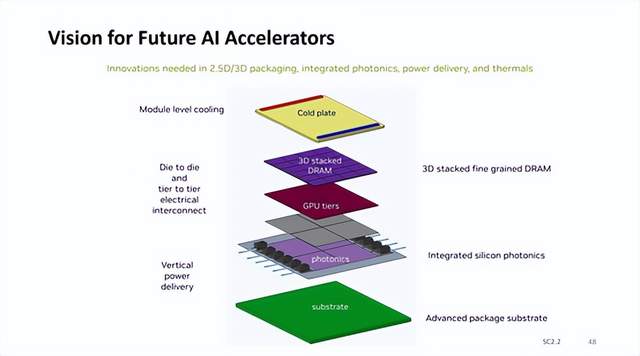

英伟达AI加速器新蓝图:集成硅光子I/O,3D垂直堆叠 DRAM 内存

加速器设计的愿景。 英伟达认为未来整个 AI 加速器复合体将位于大面积先进封装基板之上,采用垂直供电,集成硅光子 I/O 器件,GPU 采用多模块设计,3D 垂直堆叠 DRAM 内存,并在模块内直接整合

iPhone的DRAM封装,有变!

的要求。 这意味着 LPDDR 将与系统半导体分开封装(即分立封装)。库比蒂诺计划从 2026 年开始应用这一变化。 目前,LPDDR 采用堆叠封装在系统芯片之上(封装堆叠,PoP)。 对分立封装的改变

AMD要在CPU上堆叠DRAM内存,新一代捆绑销售诞生?

AMD要在CPU上堆叠DRAM内存,新一代捆绑销售诞生?

评论