前言

HPC、AI、数据中心以及汽车自动化等应用对于高效能和高性能算力需求持续增长,单芯片系统实现方案从设计、实现、生产制造、可靠性等各个方面都遇到了严峻的技术挑战。三维异构集成的3DIC chiplet设计,通过水平和垂直方向上的多芯片集成堆叠,使得芯片系统在性能、面积/体积、功耗、生产工艺、良率、成本、市场等诸多因素中获得最佳平衡,经过十多年的发展目前已逐渐成为后摩尔时代新的技术趋势。

3DIC异构集成设计分析全流程EDA平台简介

芯和3DIC异构集成设计分析全流程是一个适用于2.5D/3D系统级协同设计的统一平台。从架构规划、设计创建、物理实现,到分析验证和系统签核,它是一个高度集成、可扩展的平台,具有灵活高效的工作流程环境,支持超大容量的系统级设计管理、架构探索和自动化布局布线,支持2D/3D交互式可视操作模式,同时集成了业界可信的golden签核级分析工具,助力于实现产品最佳PPAC目标。

3DIC系统顶层的创建管理

在系统架构方面,与传统的2D架构不同,3DIC系统需要建立一个顶层结构来进行系统的设计实现和管理,管理来自于不同fab、不同工艺的不同设计库,基于系统顶层来实现系统级的逻辑互连的定义,多芯片布局,以及系统级的各类仿真、分析、验证工作等。

本文主要介绍如何使用该EDA平台中的3DIC Compiler便捷高效地实现3DIC系统顶层的创建管理。

1. Die Design创建

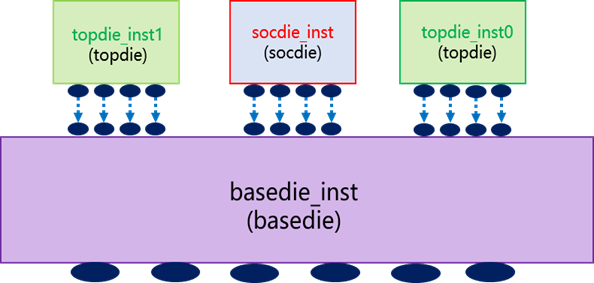

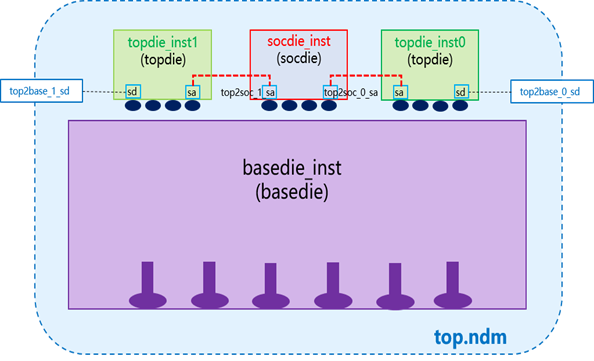

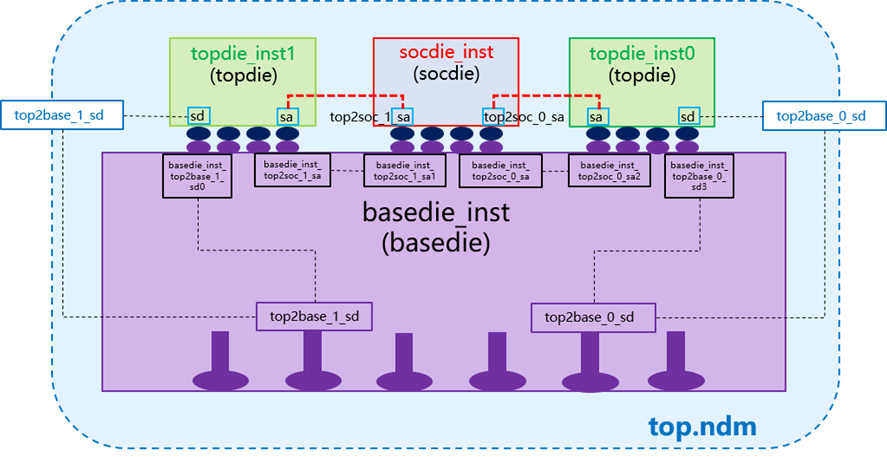

图 1

3DIC系统架构

topdie/socdie Die原型创建:使用基本输入(Die的尺寸、工艺文件、I/O信息)开始创建新设计:

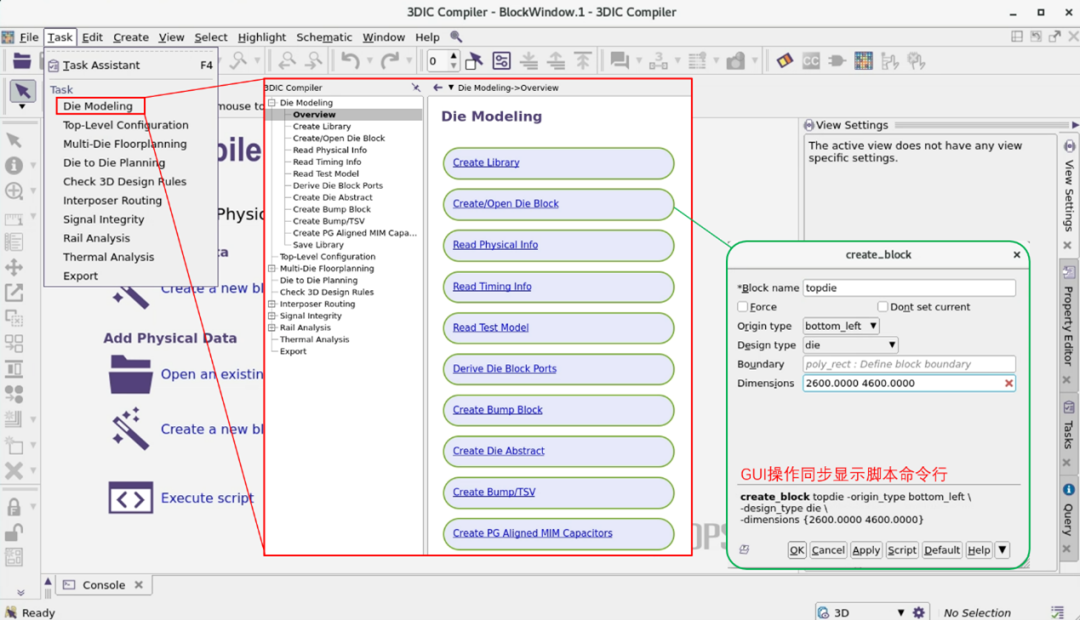

1)在菜单栏选中Task->Die Modeling,如图2所示,在设计流程任务列表中选择所需操作按序执行。通过Create Library -> Create Die Block完成工艺文件的导入和Die尺寸的设置。GUI 操作同步显示对应的脚本命令行,可通过界面Script按钮导出文本。

图 2

创建Die Design流程

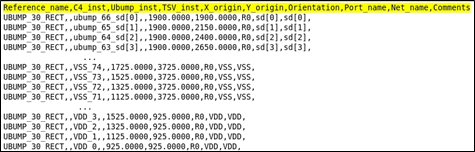

2)读取I/O物理信息。工程师可以读取已有的DEF、MDXF、CSV文件,也可以采用3DIC Compiler创建Bump/TSV。其中,CSV文件中提供Bump实例名称、Bump坐标以及互连的端口和网络,如图3所示。在读取CSV数据之后,Bump的物理和逻辑信息,包括P/G的net和port等都可以在Die design中完成创建。

图 3

CSV文件格式

2. basedie/interposer Design创建

basedie/interposer design Library的创建流程参考topdie/socdie Die。完成Library的创建以后,下一步是网表的导入。对于初始网表,工程师根据不同的设计需求,可以采用2种网表格式:

1)空白网表:网表中不包含端口或逻辑连接,所有Die-to-Die以及Die-to-Package的互联关系都是在系统顶层指定的。工具通过分析连接关系自动追溯创建basedie/interposer的网表:插入interposer/basedie到package的端口、Die到package feedthrough信号通路、D2D连接。

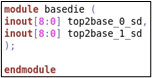

2)包含部分或者全部互连关系的网表:例如连接package的端口,如图4所示。

图 4

basedie design定义部分互连关系的网表示例

3. 3DIC系统顶层网表的定义

3DIC Compiler采用虚拟系统顶层定义进行系统设计实现和管理,其中包含多芯片系统的所有实例和互连,本身并不会产生用于生产制造的实际GDS。它的网表是一个层次化网表,对D2D互连线、Die到package feedthrough互连端口等进行完整定义。

1)basedie/interposer design初始网表为空时,系统顶层网表中D2D、D2Package feedthrough互连端口定义如图5所示:

图 5

top-level design网表示例

2)basedie/interposer design初始网表定义了package的端口时,系统顶层网表中D2D、D2Package feedthrough互连端口定义如图6所示:

图 6

top-level design网表示例

注意:当网表中含有D2D、D2Package bus总线互连的定义时,需要注意bit的定义顺序。比如本案例中,需要满足topdie port sd[8:0]与basedie port top2base_0_sd[8:0]同样比特的互连时,必须满足design创建bus port/net按照同样的顺序:

创建topdie design读取CSV文件时read_design_io需要加上option -create_bus_high_to_low,实现bus net或port按照从高比特到低比特的顺序创建;

basedie design网表bus net 按照从高比特到低比特的顺序定义;

top-level design网表bus net 按照从高比特到低比特的顺序定义;

当然,工程师也可以采用design中创建bus port/net都按照从低比特到高比特的顺序。

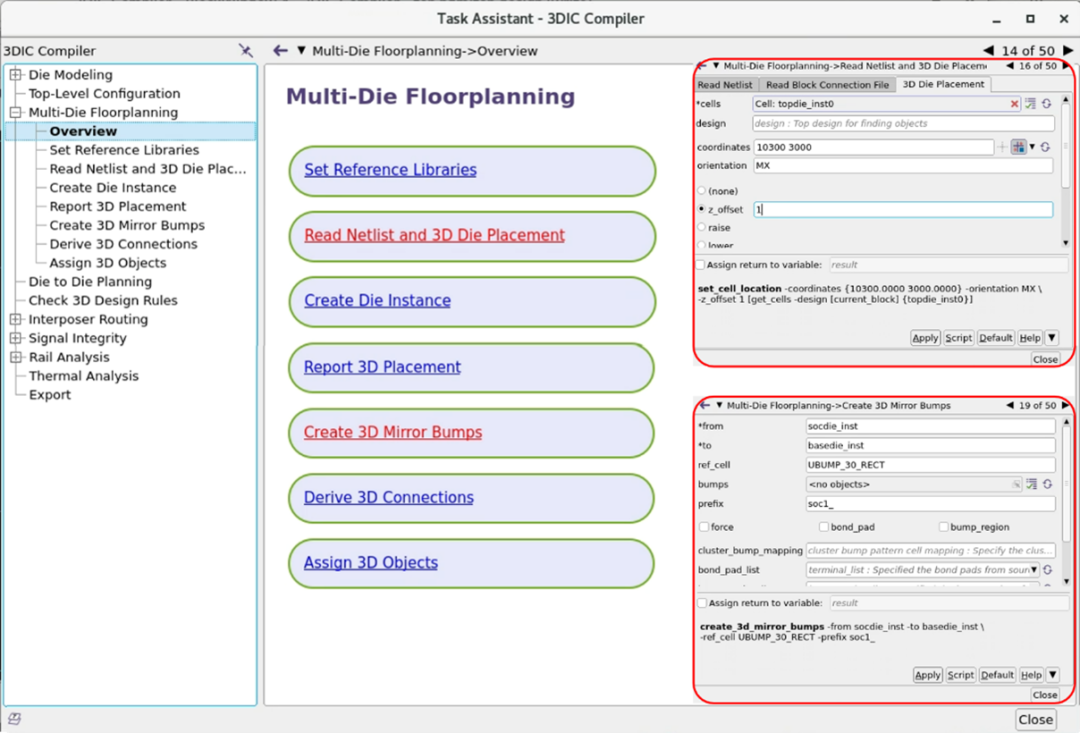

4.3DIC系统布局规划

Top-level design Library的创建流程参考topdie/socdie Die。在Task Assistant中选择Multi-Die Floorplanning,依次选择所需操作,例如:网表的读入、3D Die布局、Bump镜像、Net assign等操作,如图7所示,实现3DIC系统布局规划。

图 7

Multi-Die Floorplan流程

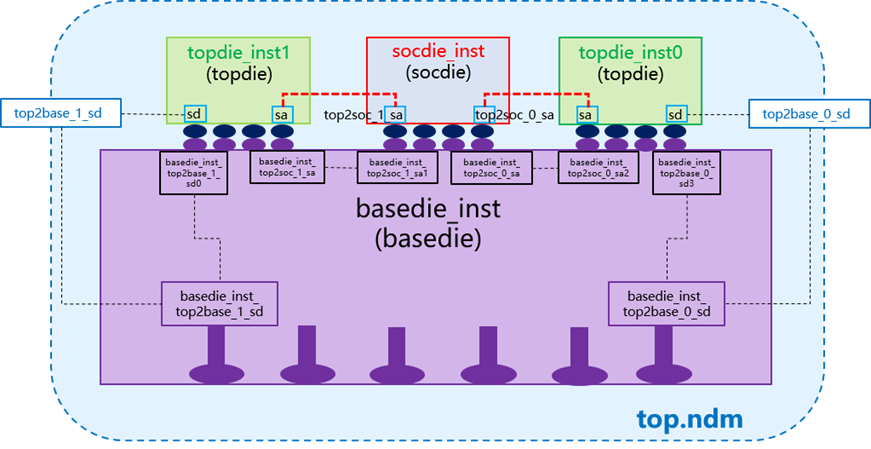

其中需要注意的是,当通过镜像的方式自动完成basedie Bumps的创建和对准后,要以assign net的方式自动追溯D2D、D2Package的各种逻辑互连关系,实现basedie的netlist创建。在这个过程中,

1)当basedie/interposer design初始网表为空时:工具依据C4 Bumps和ubumps之间的曼哈顿距离来选择C4Bumps,更严格地说,工具综合计算所有Net长度,找到设计中所有Net的曼哈顿距离的最小总和来完成D2Package逻辑互连关系的创建,实现basedie的netlist创建。如图8所示。

图 8

Mirror Bump和assign net 的原理图

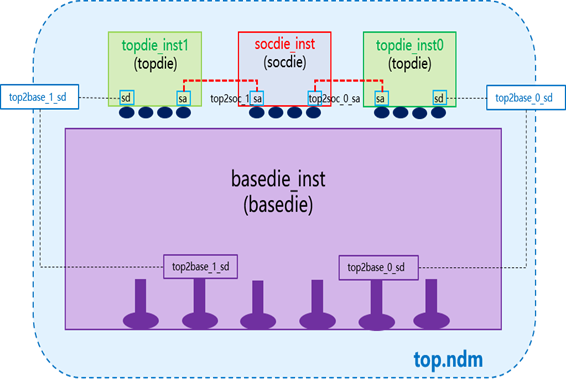

2)当basedie/interposer design初始网表定义了package的端口时:工具自动追溯D2D、D2Package的逻辑互连关系,实现basedie的netlist创建,如图9所示。

图 9

Mirror Bump和assign net 的原理图

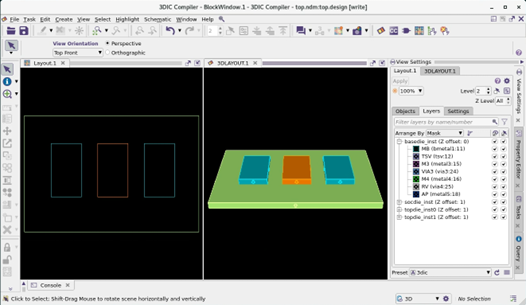

完成以上操作以后,就可以完整实现系统级的可视化管理,如图10所示,基于系统级顶层结构,可进行系统级的各类仿真、分析、验证工作。

图 10

系统顶层的2D和3D视图

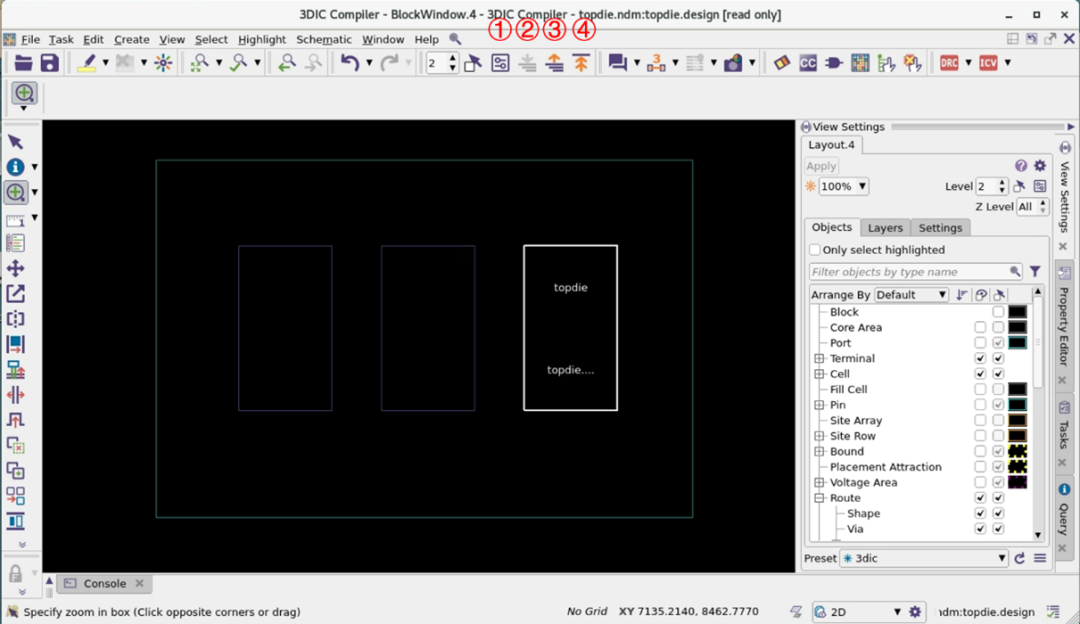

5.在顶层设计的背景下编辑Die Design

3DIC Compiler的就地编辑(Edit In Place, EIP)功能允许工程师在3D系统顶层设计的背景下编辑选定的芯片,而无需在另一个窗口中打开该Die Design。EIP菜单栏提供了以下选项:

①层次结构

设置视图层次,扩展cell类型,改变显示方式,以及设置打开多个或关闭多个层次;

②下推

向下推到一个选定的block;

③弹出

弹回上一层;

④弹到顶部

弹到最上面的一层。

当工程师使用EIP编辑一个较低层别的Die Design时,通过点击EIP菜单栏上的弹出图标,当前的block会变成所选Die Design的block。在编辑过程中,被选中的会被高亮显示,而其他的Die Design都会变暗,如图11所示。使用'f'键放大到当前选中的block,工程师就可以执行编辑操作。另外,请注意,被选中的Die Design保留了顶层设计中的方向和旋转角度。

图 11

就地编辑Die Design

总结

本文介绍了如何使用3DIC Compiler便捷高效地实现3DIC系统顶层的创建管理,从Die原型创建开始,进行Multi-Die Floorplan规划,basedie或interposer 以及系统顶层网表定义,基于系统顶层实现basedie/interposer Bumps自动创建和对准,以及自动追溯D2D、D2Package的各种互连关系建立逻辑互连,最终实现3DIC系统顶层的创建管理。其中,可以特别关注“就地编辑”功能,它能极大地帮助工程师提升多芯片系统设计的效率。

审核编辑:刘清

-

EDA技术

+关注

关注

12文章

173浏览量

38231 -

HPC

+关注

关注

0文章

342浏览量

24820 -

GUI

+关注

关注

3文章

693浏览量

42833 -

DEF

+关注

关注

0文章

13浏览量

6565 -

GDS

+关注

关注

0文章

28浏览量

6630

原文标题:【应用案例】如何使用3DIC Compiler实现“3DIC系统顶层的创建管理”?

文章出处:【微信号:Xpeedic,微信公众号:Xpeedic】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何使用EDA中的3DIC Compiler实现3DIC系统顶层的创建管理

如何使用EDA中的3DIC Compiler实现3DIC系统顶层的创建管理

评论