声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

新思科技

+关注

关注

5文章

925浏览量

52640

原文标题:谁说3DIC系统设计难?最佳PPAC目标轻松实现

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

研华边缘AI系统MIC-ATL3S荣获CEC 2025年度最佳产品奖

研华国产自主边缘AI系统MIC-ATL3S,在CEC2025年度最佳产品评选中荣获“CEC 2025年度最佳产品奖”。另一款研华大模型部署服务器SKY-602E

Socionext推出3D芯片堆叠与5.5D封装技术

Socionext Inc.(以下简称“Socionext”)宣布,其3DIC设计现已支持面向消费电子、人工智能(AI)和高性能计算(HPC)数据中心等多种应用。通过结合涵盖Chiplet、2.5D

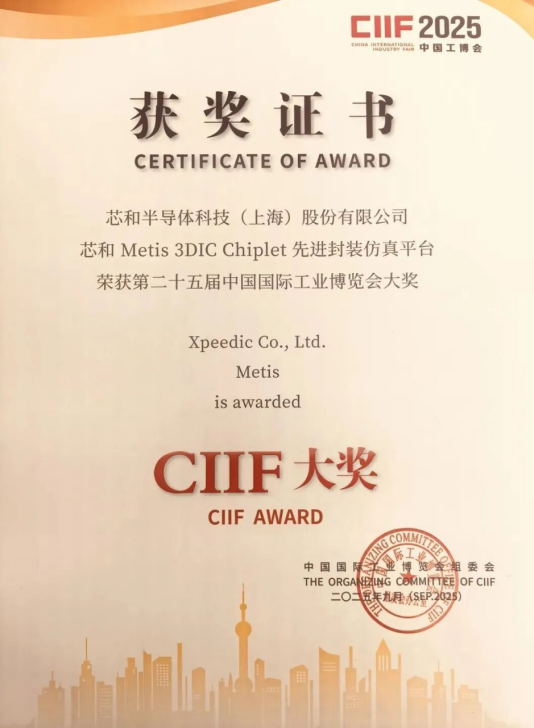

创造历史,芯和半导体成为首家获得工博会CIIF大奖的国产EDA

作为国内集成系统设计EDA专家,芯和半导体科技(上海)股份有限公司凭借其自主研发的3DIC Chiplet先进封装仿真平台Metis,从五百多家参选企业中脱颖而出,斩获第二十五届中国国际工业博览会CIIF大奖,这也是该奖项历史上首次出现国产EDA的身影。

台积电日月光主导,3DIC先进封装联盟正式成立

9月9日,半导体行业迎来重磅消息,3DIC 先进封装制造联盟(3DIC Advanced Manufacturing Alliance,简称 3DIC AMA)正式宣告成立,该联盟由行业巨头台积电

芯动科技与知存科技达成深度合作

随着3D堆叠方案凭借低功耗、高带宽特性,有望成为下一代移动端高端热门技术。芯动科技瞄准3DIC市场,与全球领先的存算一体芯片企业知存科技达成深度合作,正式量产面向Face2Face键合(F2F)系列高速接口IP解决方案。

3DIC 测试革新:AI 驱动的 ModelOps 如何重构半导体制造效率?

(PDFSolutions)推出的ModelOps系统完整版(第一阶段),正是为破解这一困局而生,把AI模型从“实验室”快速推向“量产线”,通过端到端平台实现从训练到

宏集HMI-4G套装,轻松搞定“数据上云+异地远程运维”

工业现场设备分散、环境复杂、网络难部署?宏集 HMI-4G 套装一站搞定!轻松打破数据孤岛,实现数据上云与远程运维。文末附有真实客户案例,欢迎查阅参考。

芯行纪机器学习优化工具AmazeME-Place简介

布局(Placement)是芯片后端设计中最需要全局视角的步骤,它前置约束所有后续环节,直接决定了PPAC(Performance、Power、Area、Congestion)各项指标趋势和设计目标实现的可行性。

椭偏仪与DIC系统联用测量半导体超薄图案化SAM薄膜厚度与折射率

超薄膜的表征技术对确定半导体薄膜材料(如金属、金属氧化物、有机薄膜)的最佳性能至关重要。本研究提出将微分干涉相衬DIC系统与椭偏仪联用表征超薄图案化自组装单分子膜(SAM):通过DIC

行芯科技亮相第三届芯粒开发者大会

在刚刚于无锡圆满落幕的第三届芯粒开发者大会——这场汇聚全球顶尖芯片企业、科研机构及产业链专家的盛会上,行芯科技作为国内Signoff领域的领军企业,受邀发表了主题演讲《面向3DIC的Signoff挑战与行芯创新性策略》,为行业破解3DIC Signoff难题提供了全新路径

适用于先进3D IC封装完整的裸片到系统热管理解决方案

摘要半导体行业向复杂的2.5D和3DIC封装快速发展,带来了极严峻的热管理挑战,这需要从裸片层级到系统层级分析的复杂解决方案。西门子通过一套集成工具和方法来应对这些多方面的挑战,这些工具和方法结合了

行芯科技亮相2025世界半导体博览会

此前,2025年6月20日-22日,全球半导体行业盛会——世界半导体博览会在南京国际博览中心盛大开幕。行芯科技受邀参与EDA/IP核产业发展高峰论坛,面对摩尔定律破局关键的3DIC技术,作为“守门员

行芯科技揭示先进工艺3DIC Signoff破局之道

在当下3DIC技术作为提升芯片性能和集成度的重要路径,正面临着诸多挑战,尤其是Signoff环节的复杂性问题尤为突出。此前,6月6日至8日,由中国科学院空天信息创新研究院主办的“第四届电子与信息前沿

深视智能高速相机结合DIC技术,解锁复合材料力学行为密码

(DIC),设计出一套精准的序列影像运动目标跟踪方案[1]。借助高速相机捕捉复合材料断裂瞬间的序列影像,并将其输入DIC软件进行深度分析,精准获取目标点的像素坐标,实

将2.5D/3DIC物理验证提升到更高水平

(InFO) 封装这样的 3D 扇出封装方法,则更侧重于手机等大规模消费应用。此外,所有主流设计公司、晶圆代工厂和封测代工厂 (OSAT) 都在投资新一代技术——使用硅通孔 (TSV) 和混合键合的真正裸片堆叠。

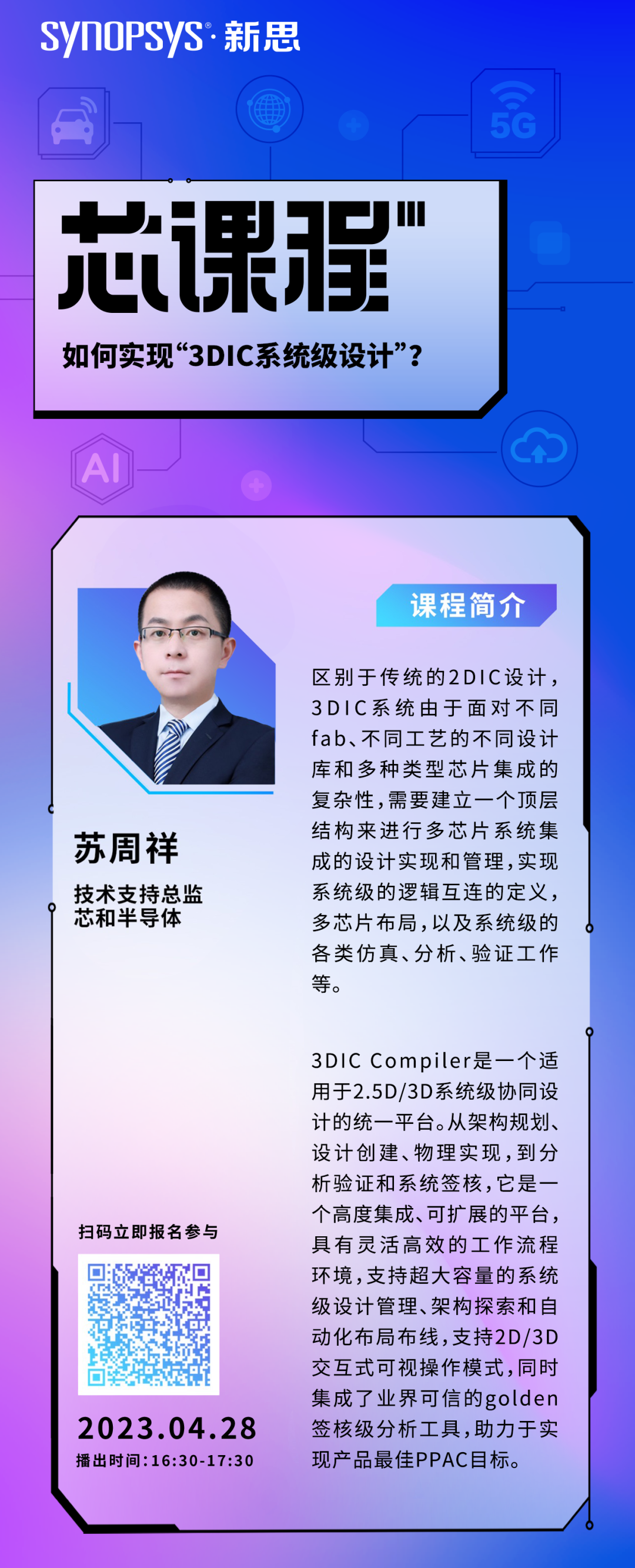

谁说3DIC系统设计难?最佳PPAC目标轻松实现

谁说3DIC系统设计难?最佳PPAC目标轻松实现

评论