简介

3DIC Compiler具有强大的Bump Planning功能。它可在系统设计初期阶段没有bump library cells的情况下,通过定义pseudo bump region patterns、创建bump regions以及填充pseudo bumps、创建Bumps的连接关系、为不同net的Bumps着色等操作,快速实现bump原型创建以及复杂bump规划设计。

本视频将展示在没有bump library cells的情况下,3DIC Compiler 如何在GUI界面使用“pseudo” bumps 快速实现Bump Planning,流程包括:

定义bump region patterns

创建bump regions以及填充pseudo bumps

快速assign nets到对应的Bumps

为不同net的Bumps着色

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

3DIC

+关注

关注

3文章

92浏览量

20167 -

芯和半导体

+关注

关注

0文章

126浏览量

32253

原文标题:【芯和设计诀窍视频】如何使用3DIC Compiler实现Bump Planning

文章出处:【微信号:Xpeedic,微信公众号:Xpeedic】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

01. 如何在 Allegro 中快速区别不同网络?| 芯巧Allegro PCB 设计小诀窍

Allegro PCB设计小诀窍系列--如何在Allegro中快速区别不同网络背景介绍:Allegro PCB设计工具可以通过高亮操作将选中的网络点亮,但是当我们的布线非常密集时,是不太好去进行

发表于 04-03 15:51

行芯科技邀您共赴IIC 2026国际集成电路展览会暨研讨会

企业,行芯科技荣幸受邀参与此次盛会,将于3月31日发表题为《Signoff全栈解决方案,赋能3DIC Chiplet一次流片成功》的主题演讲,分享在后摩尔时代助力Chiplet技术落地的签核一站式解决方案与实践成果,诚邀各位业内

新思科技携手Socionext实现3DIC芯片成功流片

在交付高性能、低功耗芯片的过程中——尤其是用于人工智能(AI)和高性能计算(HPC)应用的 3D Multi-Die 设计——设计和开发的速度至关重要。

2.3DIC集成技术简介

在2.3DIC集成工艺中,精细金属线宽/线距(L/S)重分布层(RDL)基板(或有机转接板)与积层封装基板或高密度互连(HDI)板采用分开制造的方式,两者完成各自制备后,通过焊点实现互连,并采用底部

晶圆级封装Bump制作中锡膏和助焊剂的应用解析

本文聚焦晶圆级封装 Bump 制作中锡膏与助焊剂的核心应用,以焊料印刷法、植球法为重点展开。印刷法中,锡膏是凸点主体,需依凸点尺寸选 6/7 号超细粉,助焊剂融入其中实现氧化清除与润湿;植球法里锡膏

晶圆级封装(WLP)中Bump凸点工艺:4大实现方式的技术细节与场景适配

在晶圆级封装(WLP)中,Bump 凸点是芯片与基板互连的关键,主流实现方式有电镀法、焊料印刷法、蒸发 / 溅射法、球放置法四类,差异显著。选型需结合凸点密度、成本预算与应用特性,平衡性能与经济性。

Socionext推出3D芯片堆叠与5.5D封装技术

Socionext Inc.(以下简称“Socionext”)宣布,其3DIC设计现已支持面向消费电子、人工智能(AI)和高性能计算(HPC)数据中心等多种应用。通过结合涵盖Chiplet、2.5D

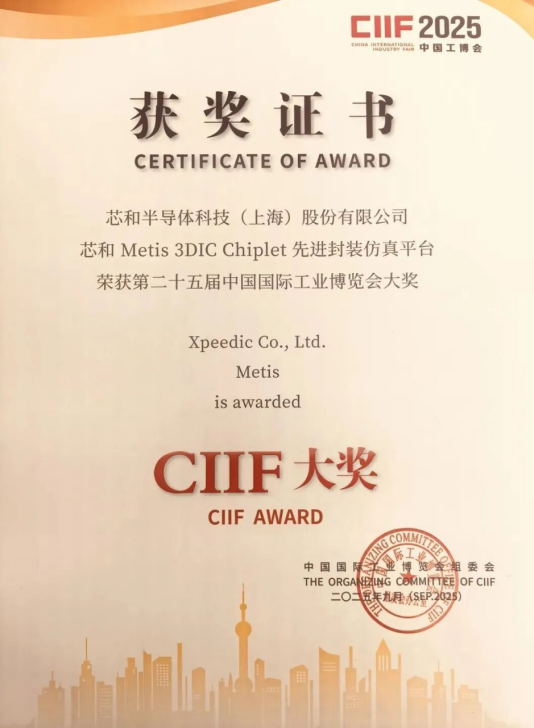

创造历史,芯和半导体成为首家获得工博会CIIF大奖的国产EDA

作为国内集成系统设计EDA专家,芯和半导体科技(上海)股份有限公司凭借其自主研发的3DIC Chiplet先进封装仿真平台Metis,从五百多家参选企业中脱颖而出,斩获第二十五届中国国际工业博览会CIIF大奖,这也是该奖项历史上首次出现国产EDA的身影。

台积电日月光主导,3DIC先进封装联盟正式成立

9月9日,半导体行业迎来重磅消息,3DIC 先进封装制造联盟(3DIC Advanced Manufacturing Alliance,简称 3DIC AMA)正式宣告成立,该联盟由行业巨头台积电

芯动科技与知存科技达成深度合作

随着3D堆叠方案凭借低功耗、高带宽特性,有望成为下一代移动端高端热门技术。芯动科技瞄准3DIC市场,与全球领先的存算一体芯片企业知存科技达成深度合作,正式量产面向Face2Face键合(F2F)系列高速接口IP解决方案。

3DIC 测试革新:AI 驱动的 ModelOps 如何重构半导体制造效率?

(PDFSolutions)推出的ModelOps系统完整版(第一阶段),正是为破解这一困局而生,把AI模型从“实验室”快速推向“量产线”,通过端到端平台实现从训练到

行芯科技亮相第三届芯粒开发者大会

在刚刚于无锡圆满落幕的第三届芯粒开发者大会——这场汇聚全球顶尖芯片企业、科研机构及产业链专家的盛会上,行芯科技作为国内Signoff领域的领军企业,受邀发表了主题演讲《面向3DIC的Signoff挑战与行

行芯科技亮相2025世界半导体博览会

此前,2025年6月20日-22日,全球半导体行业盛会——世界半导体博览会在南京国际博览中心盛大开幕。行芯科技受邀参与EDA/IP核产业发展高峰论坛,面对摩尔定律破局关键的3DIC技术,作为“守门员

行芯科技揭示先进工艺3DIC Signoff破局之道

学术会议”上,行芯科技CEO贺青博士基于最近与Top设计公司合作成功流片的先进工艺3DIC项目经验,发表了题为《面向3DIC的Signoff挑战与行芯科技创新策略》的演讲,为行业带来了

芯和设计诀窍概述 如何使用3DIC Compiler实现Bump Planning

芯和设计诀窍概述 如何使用3DIC Compiler实现Bump Planning

评论