随着领先的芯片制造商继续将 finFET——以及很快的纳米片晶体管——缩小到越来越小的间距,最小的金属线最终将无法使用铜及其liner和barrier金属。接下来会发生什么?什么时候发生?这还有待确定。因为目前看来,有多种选择正在探索中,每一种都有自己的一套权衡。

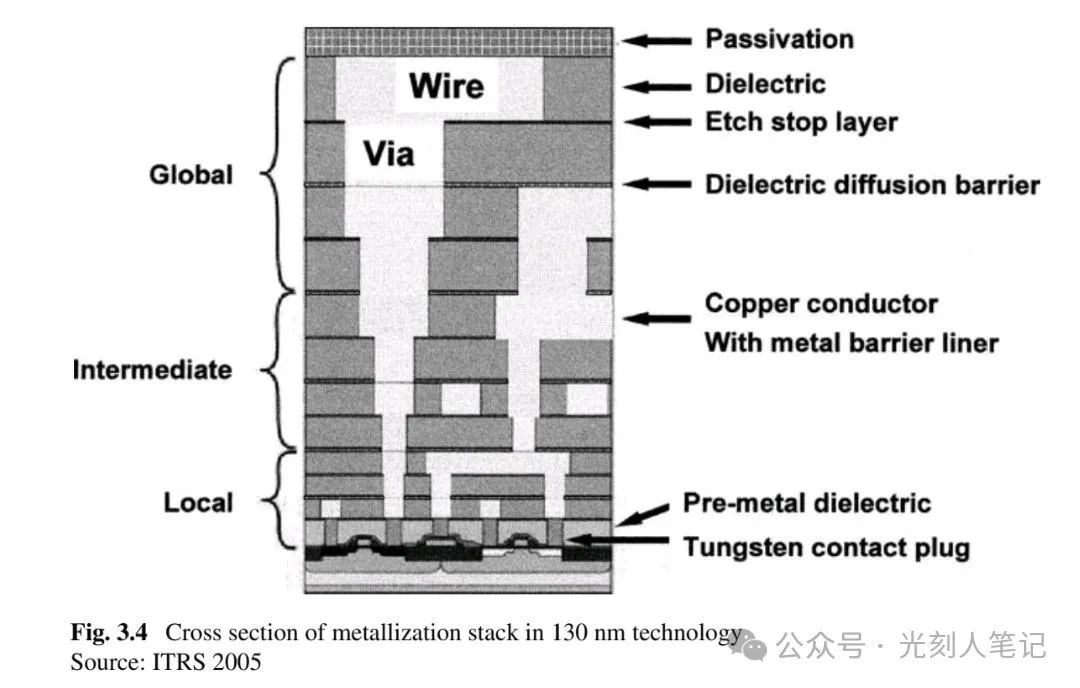

自从 IBM 在 1990 年代向业界介绍采用双镶嵌(dual damascene)处理的铜互连以来,半导体行业一直在利用铜的高导电率、低电阻率和可靠互连的优势。但随着电阻和电容的增加,RC 延迟将继续显著影响器件性能。

尽管可以使用双镶嵌来集成如钌和钼这样的铜替代品,但它们可能更适合金属蚀刻的减法方案(subtractive schemes),自铝互连时代以来,这种方案尚未在逻辑中广泛使用。尽管如此,领先的设备制造商和设备公司正在寻找一些有趣的途径来获取这些最低含量的铜。与此同时,工程师和研究团队正在进一步扩展铜线,这提供了迄今为止更实惠、更有吸引力的路线。

“在过去的 25 年里,双镶嵌一直是并且仍然是互连的基础。但我们看到,由于 RC 延迟的原因,金属图案(metal patterning)可能变得相关,”imec 研究员兼纳米互连项目总监 Zsolt Tokei 说。Imec 的方案称为 semi-damascene,由于向减法工艺的过渡将是颠覆性的,因此可能会被逐步引入。“我们认为一开始它会被用于一层,但后来它会传播到几层。这与自对准过孔相(self-aligned vias)结合,可能还会改变到线的中间。”

同时,如果可能的话,系统性能驱动因素使得将存储设备转移到生产线后端变得有吸引力。如果并且当行业开始引入具有较低热预算的互连工艺时,内存或其他设备集成等事情就变得可行了。但首先,必须解决扩展铜线和引入背面配电方案的直接工程挑战。

铜还能走多远

在 2nm 逻辑节点,铜线和通孔正在通过创造性的方式延伸。一些最有吸引力的选择包括限制barrier和liner对电阻率的影响,方法是使这些薄膜更薄( films thinner)——从化学气相沉积 (CVD) 到原子层沉积 (ALD)——或者消除它们,例如,沿垂直方向过孔和线路之间的路径。

TEL 和 Applied Materials 都提供使用自组装单分子层 (SAM:self-assembled monolayers) 实现选择性沉积的集成工艺。这些使用 CVD 或旋涂薄膜的 SAM 通常有选择地沉积在金属上,而不是电介质上,因此钴或钌liners或 ALD Ta/TaN 等barriers会粘附到所需表面。

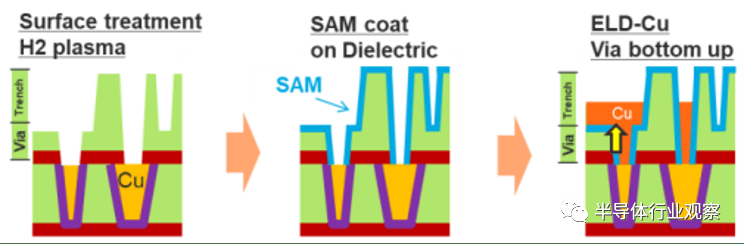

在 IITC 的一次演讲中,Yuki Kikuchi 及其 TEL 企业研发部和 JSR Micro 的同事展示了与使用 JSR 的 SAM 抑制 ALD TaN 相关的电阻和铜体积的改善,甚至取代了铜阻挡层金属。对低 k 电介质 (2.5) 的最佳选择性是通过在通孔底部使用一种 SAM (SAM_B),然后在低 k 上使用另一种材料 (SAM_F) 实现的(见图 1)。该流程能够完全消除通路侧壁(sidewalls)上的钌liner。

图 1:氢气预处理(hydrogen pretreatment)后,自组装单层 (SAM) 在使用化学沉积的预通孔填充过程中充当屏障(barrier)。资料来源:IITC 2022

有趣的是,研究人员测试了一种预通孔填充( pre-via-fill)工艺,在这种工艺中,铜填充下方没有使用阻挡层 (TaN),而是在化学沉积 (ELD) 之后沉积。设备制造商正在进行更广泛的预填充通孔测试,以降低电阻率、确保可靠性并提高铜流的生产率。

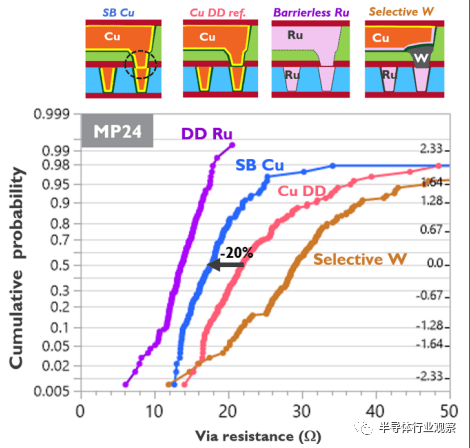

微小的过孔是互连链中最薄弱的环节。Imec 和 Applied Materials 比较了钌、钨和铜通孔,以了解与在 24nm 通孔中使用钨或钌的对比状况,通过消除铜中的底部 Ta 阻挡层可以获得哪些电阻优势(见图 2)。“关键工艺步骤是在对通孔底部的裸露铜进行原位界面( in-situ interface )工程之后,在电介质上选择性 ALD TaN 阻挡层沉积。”imec 互连金属化专家 Marleen van der Veen 说. 该团队确定通过消除障碍实现了 20% 的通孔电阻降低。在较小的尺寸下,减少会更大。

图 2:比较双镶嵌铜参考与选择性阻挡铜、无阻挡双镶嵌钌和混合钨/铜的单通孔电阻显示,消除通孔底部的阻挡层有 20% 的好处。资料来源:IITC 2022

拐点:引入减法蚀刻(subtractive etch)

在 2nm 节点之后的某个时候,该行业可能会从双镶嵌转变为一种减法金属化(subtractive metallization )形式。这代表着巨大的变化,而且不会掉以轻心。

Imec 的减法金属化版本称为半镶嵌,因为它从沟槽的介电蚀刻开始,类似于双镶嵌。“这是非常大的一步,因为它是一个新模块并且存在风险,”imec 的 Tokei 说。“然后,纵横比可以逐渐增加,在某些时候可以加入气隙(air gaps)。” 该工艺使用电介质 CMP 步骤,类似于在浅沟槽隔离 (STI) 步骤执行的电介质 CMP。

Tokei 预计最有可能进行四代钌半镶嵌工艺。之后,二元或三元金属合金可能会发挥作用。“根据电阻率和其他一些因素,我们已经确定了几个很好的候选者,但这是非常早期的研发工作,”他说。“我们有大约六年的时间来真正缩小到最佳候选的范围。”

在半镶嵌中,通孔首先在电介质堆叠中形成图案,然后进行钌沉积,这会溢出特征。然后对该金属层进行掩蔽和蚀刻以形成与通孔正交的线路层。金属图案化后,线路可以填充电介质或用于在局部层形成部分气隙。根据 imec 模拟,该工艺的成本与双镶嵌相当。

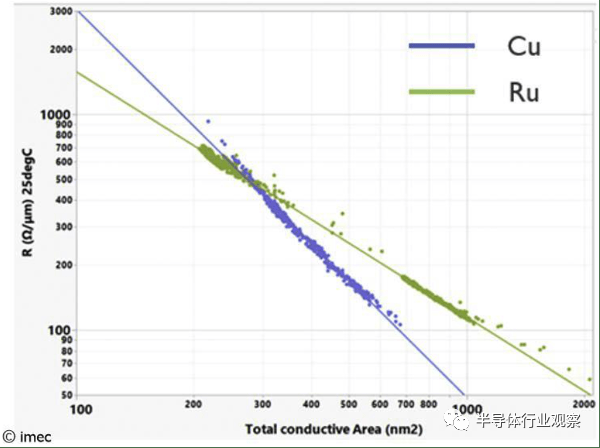

那么铜互连的规模有多远?在与钌的直接比较中,最近的一项研究发现,就电阻率而言,从铜到钌的交叉点刚好低于 300nm2,约为 17 x 17nm(见图 3)。

有多种制造气隙(air gaps)的方法,包括部分间隙填充(gap fill )或使用sacrificial材料。然而,Tokei 指出,在类似尺寸的晶圆上实现一致的气隙深度是一个行业挑战。他强调,气隙的形成不需要额外的掩膜层,而是作为加工的一部分形成。此外,必须特别注意散热,因为空气是劣质导体。

图 3:钌的电阻率在 300nm2 以下低于铜。资料来源:VLSI 2022

过渡到subtractive metallization具有根本优势,包括不会因 CMP 和蚀刻而造成介电损坏,能够采用更高纵横比的线(降低电阻),以及可能更简单的工艺。尽管如此,蚀刻工艺的负担要大得多,尤其是当 CD 向 10nm 金属间距发展时。

Lam Research 和 imec 探讨了与氧基钌蚀刻化学品相关的一些挑战。通常,钌通过溅射(物理气相沉积或 PVD)沉积,然后在 400°C 左右退火以实现最低电阻率。Si3N4/TiN 硬掩模(mandrels)中的间隔图案用于形成紧密尺寸,从中蚀刻 >3 纵横比的钌线。一个关键挑战涉及在硬掩模的侧壁上生长氧化层,这会显着缩小沟槽。实施高级清洁步骤和原位等离子清洁(in-situ plasma cleans)以去除残留物并限制 TiN 底切(undercut)。

对于 Cl 2 /O 2化学中的钼蚀刻,Lam 和 imec 确定主要问题是侧壁钝化不足(insufficient sidewall passivation)和金属氧化。该团队能够通过在部分钼蚀刻后沉积薄氧化物来解决这个问题,他们指出,由于金属的氧化电位,封装可能是必要的。

“根据数据,我们在钌方面取得的进展比在钼方面取得的进展更多,”imec 的 Tokei 说。“钼的一个问题是氧化,这使得它更适合镶嵌类型的方法。这对于中线来说非常有趣,而且它是一种廉价的金属。”

工艺建模在帮助建立设计规则、评估工艺窗口和提高产量方面发挥着关键作用。Lam计算产品副总裁大卫·弗里德 (David Fried) 表示:“虚拟制造是对工艺和工艺流程的逐步行为描述,它与关键设计信息相结合,以创建晶圆中发生的事情的硅精确 3D 模型。”

例如,Lam 的 Coventor 部门的 SEMulator3D 平台被用来评估 imec 的带有工艺助推器的半镶嵌流如何影响金属间距为 14nm 和 16nm(1.5nm 节点)的新掩模组的 RC 性能。性能助推器,包括完全自对准图案、高 AR 金属线和气隙,都经过建模和确认。在其他发现中,模拟器比较了不同的通孔自对准方法,以确定哪种方法在 10 纳米和 7 纳米节点上实现了最宽的覆盖公差。

“因为这些模型必须精确到硅,我们在校准技术上花费了大量时间,”Fried 说。“通过我们的基线流程模型,我们使用机器学习技术对流程模型进行多元非线性优化,从而创建该流程的可视化表示。当它被校准到过程空间中的多个点时,它就可以预测过程窗口的其余部分。”

连接背面电源

背面电源传输 (BPD) 是一种从晶圆背面向晶体管传输电源的创新方式,释放了正面互连以仅传输信号。这缓解了拥堵,领先的芯片制造商将在 2nm 节点上实施它。Lam Research 的高级工程总监 Tom Mountsier 说:“利用晶圆背面进行配电可以有效地增加芯片的功能面积,而不会增加其占地面积。”

“背面电源集成的最大挑战之一是电连接晶圆的正面和背面。这就是 TSV 的用武之地,”Mountsier 说,并指出芯片制造商正在评估不同的集成方案。所有选项都涉及蚀刻和金属填充。

最具挑战性的方案涉及到源极外延的直接背面接触。“通孔将很小,纵横比很高,”他说。“您还需要与外延层进行低电阻接触,就像在正面对源极/漏极接触所做的那样。因此,填充钨或钼可能是可能的选择。由于重大的集成挑战,例如将背面接触与正面外延对齐,以及在降低的温度(400°C 或更低)下在金属和外延之间进行欧姆接触,实施将需要时间。”

Lam 的高级半导体工艺工程师 Assawer Soussou 总结道:“背面电源传输以工艺复杂性为代价实现了技术优势。”

电力输送也已成为企业封装方面的热门话题。“最近,人们对光子学很感兴趣,尤其是联合封装光学器件,”ASE 销售和营销高级副总裁 Yin Chang 说。“这大大增加了数据传输的带宽。许多公司都在通过基板承载多少带宽方面遇到了限制,如果您无法满足这些要求,那么光子学确实是唯一的选择。所以基板真的变成了一个电力传输系统。”

结论

目前,双镶嵌铜的间距已扩展到 20 纳米,但即将彻底改变涉及钌或其他替代金属的减法方案。就电阻率而言,随着功能下降到 17 x 17nm 以下,领先的设备制造商正在接近,钌变得很有吸引力。公司可以在为重大转型做准备的同时,使用barrierless via bottoms 获得额外收益。

审核编辑 :李倩

-

半导体

+关注

关注

339文章

31279浏览量

266769 -

晶体管

+关注

关注

78文章

10443浏览量

148696 -

铜线

+关注

关注

2文章

56浏览量

17491

原文标题:铜互连,还能撑多久?

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Co/TiN界面对钴互连电阻率的影响

UPS应急电源能供电多久?三大关键决定你的续航时间

MACOM公司推出高密度铜互连解决方案

如何正确选用Finisar AOC/DAC提升光互连性能

三防漆多久能干?

从内存接口到PCIe/CXL、以太网及光互连,高速互连芯片市场分析

CMI500/CMI700系列铜厚测试仪的面铜探头、孔铜探头哪家好?

UPS不间断电源一般能供电多长时间?真相可能和你想的不一样!

是德科技亮相448G全球高速铜缆创新技术与供应链大会

TSV工艺中的硅晶圆减薄与铜平坦化技术

立讯技术高速裸线技术如何抢占高速互连赛道

铜对芯片制造中的重要作用

从微米到纳米,铜-铜混合键合重塑3D封装技术格局

一文详解铜互连工艺

铜互连,还能撑多久?

铜互连,还能撑多久?

评论