欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:FPGA需要跑多快?影响FPGA计算性能的几大因素

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22502浏览量

639111

原文标题:FPGA需要跑多快?影响FPGA计算性能的几大因素

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

深入解析IGLOO2 FPGA与SmartFusion2 SoC FPGA:性能、规格与应用考量

深入解析IGLOO2 FPGA与SmartFusion2 SoC FPGA:性能、规格与应用考量 在当今电子设计领域,FPGA(现场可编程门阵列)和SoC

深入解析IGLOO2 FPGA与SmartFusion2 SoC FPGA:性能、特性与应用

深入解析IGLOO2 FPGA与SmartFusion2 SoC FPGA:性能、特性与应用 在当今电子科技飞速发展的时代,现场可编程门阵列(FPGA)和片上系统(SoC)

基于FPGA的DAQ系统|实现高性能数据采集的挑战

的性能和灵活性备受关注。FPGA,就像一块可以根据我们需求“变形”的芯片,可高速并行处理大量数据,实现传统处理器难以达到的低延迟和高性能,使其在需要高吞吐量和精确

Microsemi IGLOO2 FPGA与SmartFusion2 SoC FPGA深度剖析

,我们就来深入探讨一下Microsemi的IGLOO2 FPGA和SmartFusion2 SoC FPGA,看看它们在性能、特性以及应用方面有哪些独特之处。 文件下载

AMD UltraScale架构:高性能FPGA与SoC的技术剖析

AMD UltraScale架构:高性能FPGA与SoC的技术剖析 在当今的电子设计领域,高性能FPGA和MPSoC/RFSoC的需求日益增长。AMD的UltraScale架构凭借其创

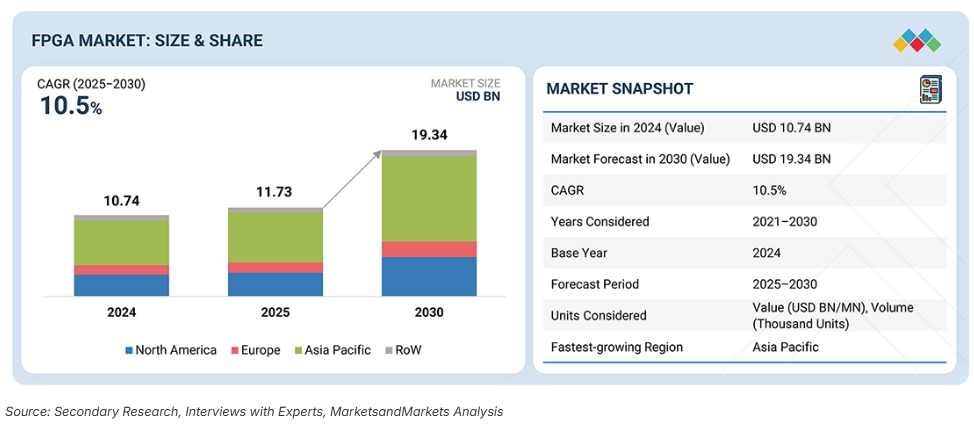

MarketsandMarkets FPGA行业报告,2026~2030 FPGA市场洞察

,Field-Programmable Gate Array)是一种高度灵活、可重构的集成电路。与传统 ASIC 不同,FPGA 制造完成后仍可以在终端重新编程,在 高性能并行计算、实时信号处理、通信加速 等领域具有独特优势。

嵌入式和FPGA的区别

嵌入式系统与FPGA的核心差异:软件定义功能VS硬件可重构。嵌入式适合通用计算,开发门槛低;FPGA凭借并行处理实现纳秒级响应,但成本高、开发难。二者融合的SoC器件正成为未来趋势,平衡性能

发表于 11-19 06:55

FPGA测试DDR带宽跑不满的常见原因及分析方法

在 FPGA 中测试 DDR 带宽时,带宽无法跑满是常见问题。下面我将从架构、时序、访问模式、工具限制等多个维度,系统梳理导致 DDR 带宽跑不满的常见原因及分析方法。

Pico2-ICE FPGA开发板的应用示例

FPGA 和 MCU 结合的开发板不多,而 Pico2‑ICE 则把小巧、灵活和易上手完美结合。搭载 RP2350 双核 RISC-V MCU + Lattice iCE40UP5K FPGA,配合官方 SDK,你可以一步步跑通

Altera Agilex™ 3 FPGA和SoC FPGA

Altera Agilex™ 3 FPGA和SoC FPGA Altera/Intel Agilex™ 3 FPGA和SoC FPGA使创新者能够将成本优化的设计提升到更高的

开源的e203rtl 可以在FPGA板子(DDRt)跑50M主频吗?

开源的e203rtl 可以在FPGA板子(DDRt)跑50M主频吗?

跑25M时,可以通过spi打印出来数数据,但是跑50M主频时候,看似下载进去了,什么也没打印出来,有遇到这个问题的

发表于 07-11 07:58

PLL技术在FPGA中的动态调频与展频功能应用

随着现代电子系统的不断发展,时钟管理成为影响系统性能、稳定性和电磁兼容性(EMI)的关键因素之一。在FPGA设计中,PLL因其高精度、灵活性和可编程性而得到广泛应用,本文将深入探讨PLL技术在

智多晶FPGA设计工具HqFpga接入DeepSeek大模型

在 AI 赋能工程设计的时代浪潮中,智多晶率先迈出关键一步——智多晶正式宣布旗下 FPGA 设计工具 HqFpga 接入 DeepSeek 大模型,并推出 FPGA 设计专属 AI 助手——晶小助!这是

FPGA需要跑多快?影响FPGA计算性能的几大因素

FPGA需要跑多快?影响FPGA计算性能的几大因素

评论