典型的SOC由多个接口组成,这些接口可以访问设计中的存储器。当我们验证这样的设计时,我们需要确保各种接口访问的内存不重叠,从而导致数据完整性损失。

在使用涉及多个接口的基于 System Verilog 的验证环境中进行验证时,我们需要对激励提供简洁的约束,以确保这些访问不会重叠并导致数据完整性丢失。

验证工程师通常不得不花费大量时间来调试应用的约束,这种形式的约束导致激励约束不足,这是一条非常危险的路径。

随着基于 UVM 的单例内存管理器的引入,随着 UVM 提供的内存管理类的可用性,此任务变得更加易于实现。但是,这些新的验证组件仍然不是专门为开发涉及多个主站的环境而设计的。我们在这里开发的“简易内存管理器”最大限度地利用了现有的UVM方法,并且还提供了多个主服务器之间更轻松的内存访问。

什么是 UVM 内存管理器?

关于uvm_mem_mam类的可用资源非常稀缺,因此如果读者对其功能没有太多了解,这是可以理解的。在继续讨论内存管理器提供的功能之前,我们想简要介绍一下默认 UVM 内存管理器的功能。

在 UVM 中,有四个类与内存管理相关联。它们在下面提到 -

uvm_mem_mam_cfg– 它允许我们选择要由管理器管理的字节数以及开始和结束偏移量。

uvm_mem_mgr– 它由希望分配内存的静态/动态实体启动。

uvm_mem_alloc_policy– 它还可用于控制管理器的开始和结束偏移量,并根据我们的要求约束这些变量。

uvm_mem_region– 这些表示内存管理器要分配的区域。这些区域包含开始偏移量和管理器要分配的字节数。

现在我们已经简要了解了默认内存管理器的操作以及与 UVM 中的内存管理关联的类,让我们看看我们在内存管理器中的这个现有功能上添加了什么。

支持的功能

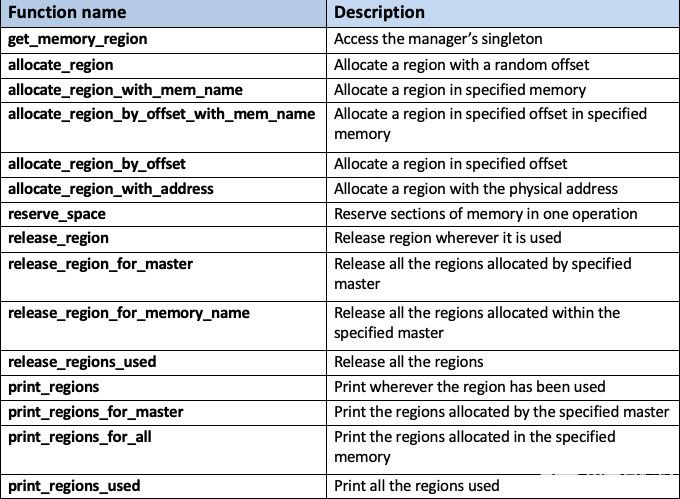

“简易内存管理器”支持以下一组功能,可以在各种项目中重用:

整个内存分为内存、主内存和分配的区域,支持这三个维度上的区域分配和释放。

将记忆划分为虚拟区域。

区域的运行时分配和释放。

多个主节点的非重叠分配。

通过提供要分配的区域的物理地址和字节数来分配区域。

可以保留内存块,以便任何主节点都无法访问它。

提供有关已分配区域的详细信息的调试机制。

根据.xls文件中的输入创建记忆。

顶部寄存器块和管理器可通过脚本进行配置。

即插即用,因此可以直接在任何现有的UVM环境中使用。

建筑

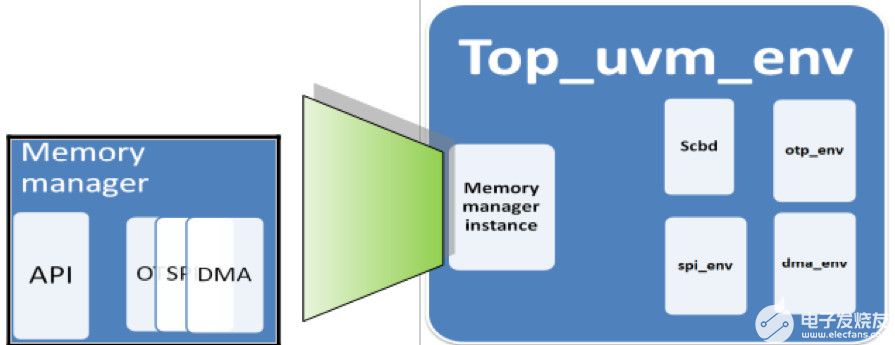

本节描述了内存管理器的结构以及将介绍“简易内存管理器”的环境。管理器由顶部uvm_reg_block 组成,其中包含单个存储器(例如 – Flash、JTAG、SRAM 等)。单个存储器是根据.xls文件中提供的数据创建的。各个内存类配置可根据项目要求完全定制。以类似的方式,我们可以通过脚本的命令行选项配置顶部内存。管理器是单例,因此不会有数据重复。

图1使用简易内存管理器的环境

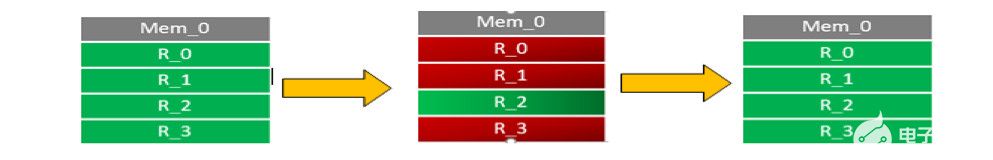

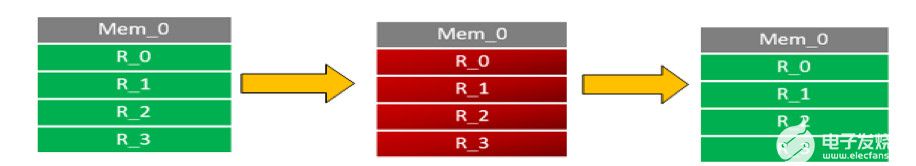

图2使用 Easy 内存管理器分配和释放内存区域

表1管理器内的方法列表

在这里,我们展示了如何在多主场景中使用“简易内存管理器”的场景。存储器由两个主站访问,一个是SPI主机,另一个是以太网主机,它们正在执行自己的测试序列。在该示例中,您可以观察到主节点在访问内存时提供的唯一编号如何使用户更易于控制测试用例中的区域处理。此外,用户不需要知道RAL模型中内存的结构。他可以简单地提供实际地址,经理足够聪明,可以根据地址保留区域。

图3预留/释放区域时主节点与管理器的交互

最初,整个内存范围都可用,SPI主站请求两个区域,以便它可以在这些区域上启动其序列。

同样,以太网主站也请求了三个区域。以太网主站和SPI主站区域将通过主站编号进行区分,主站编号在分配时由主站作为参数传递。

SPI 主站已完成其序列,并通过在调用释放函数时指定其唯一主站编号来释放它分配的两个区域。

以太网主站现在希望访问先前分配给SPI主站的区域。因此,它将通过指定物理地址来请求这些区域。

以太网序列已完成,它将释放它请求的区域。

整合步骤

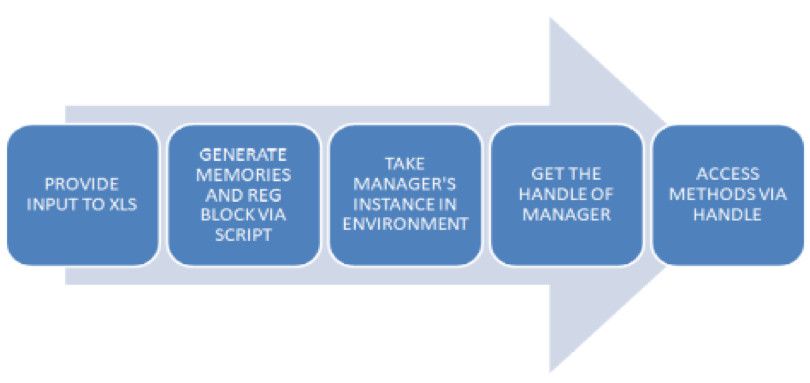

图4 集成步骤

向XLS提供输入–以适当的格式将数据写入.xls文件以创建单个内存。

通过脚本生成内存和reg_block – 使用适当的命令行选项运行脚本。如果未提供命令行选项,则使用默认选项。

在环境中获取经理的实例 –内存和管理器将根据.xls文件和命令行选项中提供的数据创建。在要访问管理器的组件中创建管理器的对象实例。

获取管理器的句柄 – 管理器的实例需要获取管理器的句柄,因为它是单例。管理器由返回单一实例句柄的方法组成。

通过句柄访问方法可以使用管理器的句柄访问管理器的方法。

“简易内存管理器”本质上是通用的,可用于任何现有的基于UVM的验证环境。管理器包易于配置,可以扩展到任何特定于项目的环境中,而无需对内部代码进行任何更改。

在eInfochips,我们已经在系统,子系统和IP级环境中使用了这种内存管理器,并取得了预期的结果。我们已经使用QuestaSim和NCSim模拟器验证了此组件。

审核编辑:郭婷

-

以太网

+关注

关注

41文章

6183浏览量

181540 -

存储器

+关注

关注

39文章

7756浏览量

172179 -

soc

+关注

关注

40文章

4623浏览量

230164

发布评论请先 登录

C++ 11 14 17 20内存管理-指针、智能指针和内存池基础与提升

MAX1917:DDR内存电源管理的理想选择

MAX17000A:DDR2和DDR3内存电源管理的理想之选

探秘DS2731:缓存内存电池备份管理IC的卓越性能与应用

rk基于linux/android内存管理

为什么单片机中很少使用malloc,而PC程序频繁使用呢?

NVMe高速传输之摆脱XDMA设计24: UVM 验证包设计

NVMe高速传输之摆脱XDMA设计24: UVM 验证包设计

实时监控与诊断,让EtherCAT网络管理更轻松!

在UVM中更轻松地进行内存管理

在UVM中更轻松地进行内存管理

评论