台积电是全球排名第一的半导体代工企业,他们的开放式创新平台 (OIP) 活动很受欢迎,参加人数也很多,因为所提供的工艺技术和 IP 对许多半导体设计领域都非常有吸引力。台积电技术路线图显示了到 2025 年的 FinFET 和 Nanosheet 计划的时间表。

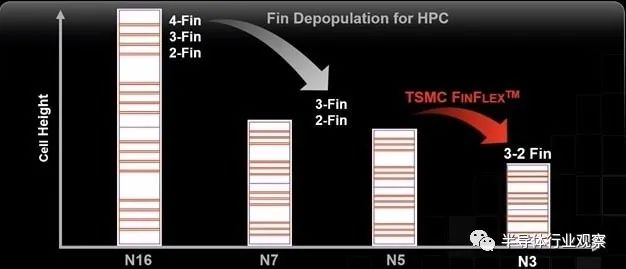

从 N3 开始,出现了一种名为FinFlex的新产品,它使用设计技术协同优化 (DTCO),有望为节能和高性能等细分市场改进功率、性能和面积 (PPA)。借助 FinFlex 方法,设计人员可以根据其设计目标从三种晶体管配置中进行选择:

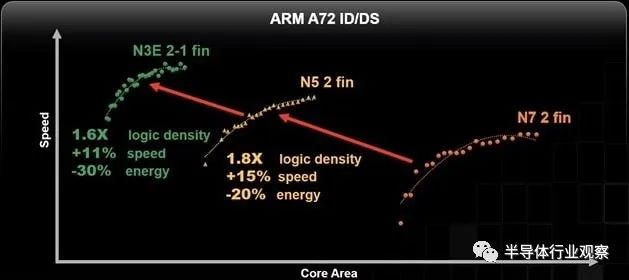

3-2 fin blocks,用于高性能

2-2 fin,高效性能

2-1 fin,功率最低,密度最佳

工艺节点 N16 到 N3 中使用的fin选择的历史如下所示:

EDA 供应商 Synopsys、Cadence、Siemens EDA 和 ANSYS 已经更新了他们的工具以支持 FinFlex,并且在单个 SoC 中,您甚至可以混合使用fin block选项。沿着时序关键路径,您可以使用高fin单元,而非关键路径单元可以是低fin。作为进程缩放优势的示例,Lu 展示了一个 ARM Cortex-A72 CPU,在 N7 中实现,具有 2 个fin,N5 具有 2 个fin,最后是 N3E 具有 2-1 个fin:

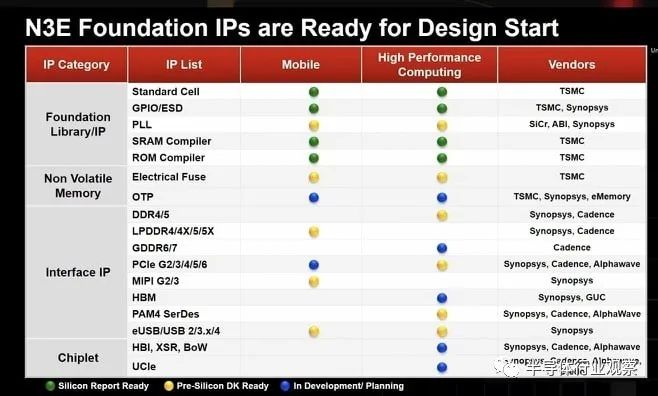

N3E 的 IP 单元来自多家供应商:TSMC、Synopsys、Silicon Creations、Analog Bits、eMemory、Cadence、Alphawave、GUC、Credo。IP 准备状态分为三种状态:硅报告准备就绪、硅前设计套件准备就绪和开发中。

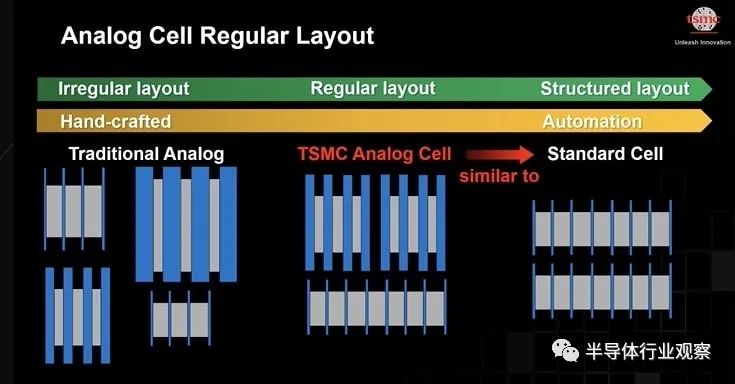

在 TSMC,他们的模拟 IP 使用结构化程度更高的规则布局,这会产生更高的产量,并让 EDA 工具自动化模拟流程以提高生产力。TSMC 模拟单元具有均匀的多晶硅和氧化物密度,有助于提高良率。他们的模拟迁移流程、自动晶体管大小调整和匹配驱动的布局布线支持使用 Cadence 和 Synopsys 工具实现设计流程自动化。

模拟单元可以通过以下步骤进行移植:原理图移植、电路优化、自动布局和自动布线。例如,使用他们的模拟迁移流程将 VCO 单元从 N4 迁移到 N3E 需要 20 天,而手动方法需要 50 天,快了大约 2.5 倍。

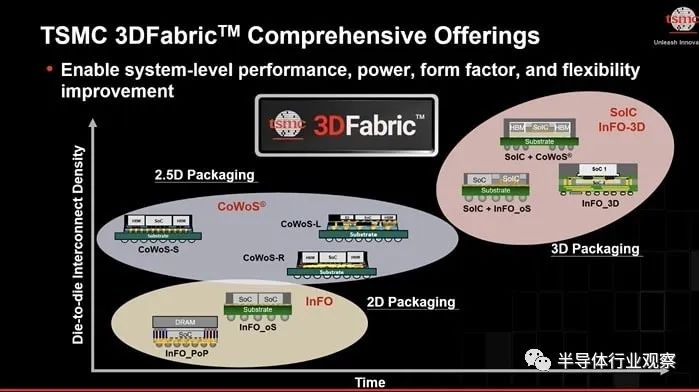

台积电需要考虑三种类型的封装,分别是二维封装(InFO_oS、InFO_PoP)2.5D封装(CoWoS)和3D封装(SoIC和InFO-3D)

3DFabric 中有八种包装选择:

最近使用 SoIC 封装的一个例子是 AMD EPYC 处理器,这是一种数据中心 CPU,它的互连密度比 2D 封装提高了 200 倍,比传统 3D 堆叠提高了 15 倍,CPU 性能提高了 50-80%。

3D IC 设计复杂性通过 3Dblox 解决,这是一种使用通用语言实现 EDA 工具互操作性的方法,涵盖物理架构和逻辑连接。四大 EDA 供应商(Synopsys、Cadence、Siemens、Ansys)通过完成一系列五个测试用例,为 3Dblox 方法准备了工具:CoWoS-S、InFO-3D、SoIC、CoWoS-L 1、CoWoS-L 2。

台积电通过与以下领域的供应商合作创建了 3DFabric 联盟:IP、EDA、设计中心联盟 (DCA)、云、价值链联盟 (VCA)、内存、OSAT、基板、测试。对于内存集成,台积电与美光、三星内存和 SK 海力士合作,以实现 CoWoS 和 HBM 集成。EDA测试厂商包括:Cadence、西门子EDA和Synopsys。IC测试供应商包括:Advantest和Teradyne。

AMD、AWS 和 NVIDIA 等半导体设计公司正在使用 3DFabric 联盟,随着 2D、2.5D 和 3D 封装的使用吸引了更多的产品创意,这个数字只会随着时间的推移而增加。台积电拥有世界一流的DTCO工程团队,国际竞争足以让他们不断创新新业务。数字、模拟和汽车细分市场将受益于台积电在 FinFlex 上宣布的技术路线图选择。3D 芯片设计得到 3DFabric 联盟中聚集的团队合作的支持。

审核编辑:郭婷

-

半导体

+关注

关注

339文章

31236浏览量

266525 -

台积电

+关注

关注

44文章

5810浏览量

177043

原文标题:台积电先进制程和封装的更多细节

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

台积电Q3净利润4523亿元新台币 英伟达或取代苹果成台积电最大客户

今日看点丨台积电助力苹果自研芯片;均胜电子再获150亿元项目定点

台积电日月光主导,3DIC先进封装联盟正式成立

化圆为方,台积电整合推出最先进CoPoS半导体封装

台积电Q2净利润3982.7亿新台币 暴增60% 创历史新高

力旺NeoFuse于台积电N3P制程完成可靠度验证

台积电加大投资布局 2纳米制程研发取得积极进展

台积电先进制程和封装改进功率、性能和面积

台积电先进制程和封装改进功率、性能和面积

评论