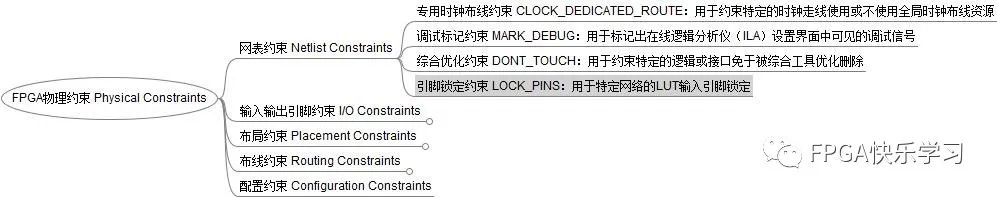

概述

话说网表约束中的CLOCK_DEDICATED_ROUTE、MARK_DEBUG和DONT_TOUCH,在实际工程中常常都可能遇上。MARK_DEBUG和DONT_TOUCH在设计和调试中可能常常要用到,CLOCK_DEDICATED_ROUTE偶尔能够应应急。而这里要介绍的LOCK_PINS,笔者至今没有碰过,估计大家在实践中恐怕也很难有机会或必要用上它。但谁知道呢?存在即是合理,相信Xilinx把这样一个非常底层的约束搬上台面,也一定有它的用场,本着万一哪天能够应应急的想法,我们也来了解一下这个LOCK_PINS的使用吧。

原理探究

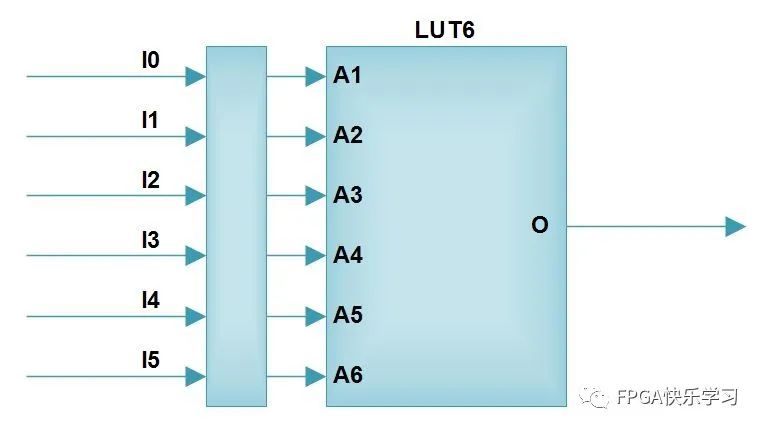

网表约束LOCK_PINS约束的对象是Xilinx FPGA器件中LUT物理输入端口和逻辑输入端口的映射关系。关于LUT结构,大家可以参考Xilinx的ug474文档,该文档详细介绍了Artix-7系列FPGA器件的逻辑资源。当然,文档中对于LUT的结构描述中,只提及输入端口,并没有所谓物理输入端口和逻辑输入端口的概念。笔者认为,ug474所涉及的LUT结构的输入端口,其实是包括逻辑输入端口和物理输入端口的,它们之间的连接也是可以布线算法的需要进行灵活调整的。

如图所示,LUT6中的物理输入端口有A1~A6,逻辑输入端口有I0~I5。在逻辑输入端口和物理输入端口之间,存在着一块布线池(官方没有这方面的介绍,笔者根据自己的理解进行描述,仅供参考)。

也就是说,物理输入端口和逻辑输入端口并不是固定I0-A1、I1-A2……这样规规矩矩的成对连接的,它们的一一对应关系是可以根据布线需要进行调整的。之所以提供这样的配对灵活性,我相信很大程度上是基于最优化外部输入接口(即连接到I0~I5的走线)的布线而设计的。而一旦进行工程的布局布线后,LUT的逻辑输入端口和物理输入端口之间的一一对应关系便会被固定下来。当然了,此时,作为设计者的你,基于某些特定的优化目的,可以通过网表约束LOCK_PINS来锁定某对或某几对逻辑和物理输入端口的映射关系。可以说,LOCK_PINS约束相当底层,对于所谓的特定的优化目的,笔者只在ug903文档中找到“物理输入端口A5和A6是最快的LUT输入端口,所以可以使用LOCK_PINS将时序关键路径约束到该端口上”这样的描述。而笔者在ug474中并没有找到Artix-7的LUT有类似的描述。当然,或许ug903的这个描述是针对其它某个FPGA系列器件的LUT。不管怎样,大家先有个概念,知道有这么回事,将来真遇到类似这么细节的问题时,可以快速在这个方向上做进一步的探索,免去“众里寻他千百度”的力气。

工程实践

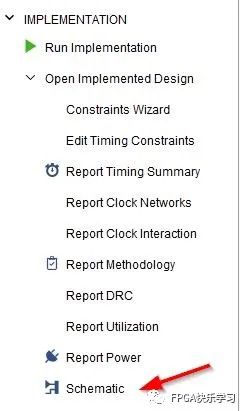

好了,原理说明白了,接着就动手实践一把。以《Verilog边码边学》教程的sim_201工程为例,打开工程后,保证工程已经做过编译,然后点击IMPLEMENTATION->Open Implemented Design->Schematic,打开原理视图。

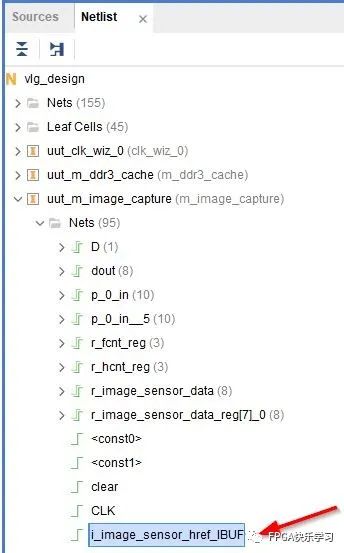

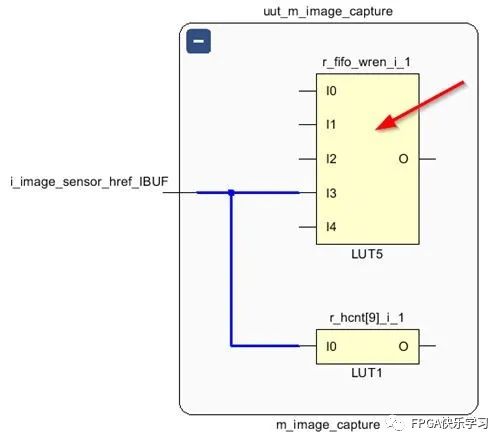

此时,可以在Netlist界面下展开具体的网表,找一个信号进行实践。当然了,实际应用中,需要哪个信号,可能是根据具体的需要而定的,这里我们只是为了实践一下如何使用LOCK_PINS约束,所以就随便找到如图所示的uut_m_image_capture->Nets下的i_image_sensor_href_IBUF这个信号。

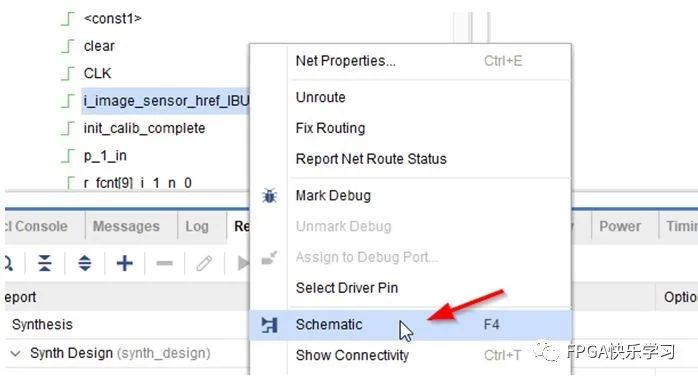

在i_image_sensor_href_IBUF信号上右键单击,在弹出菜单中再单击Schematic选项。

此时可以看到,Schematic(2)定位到了i_image_sensor_href_IBUF信号在原理图中的位置。由于该信号连接的r_fifo_wren_i_1这个LUT有5个输入端口,因此我们可以继续双击r_fifo_wren_i_1这个LUT查看它所有的输入端口。

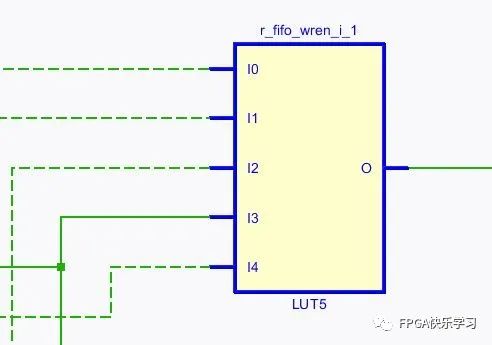

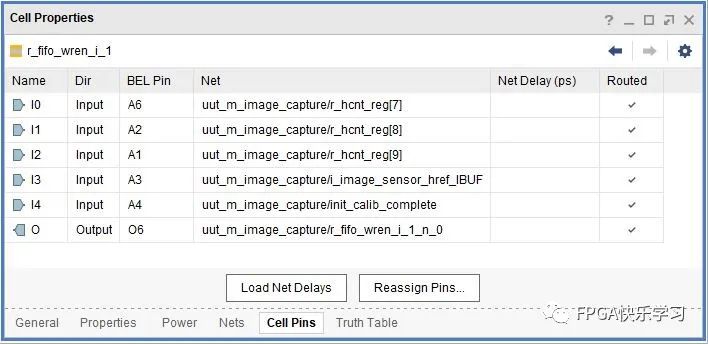

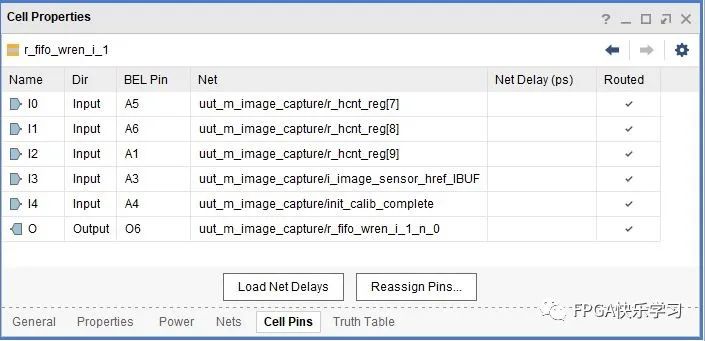

r_fifo_wren_i_1的所有5个输入端口如图所示。

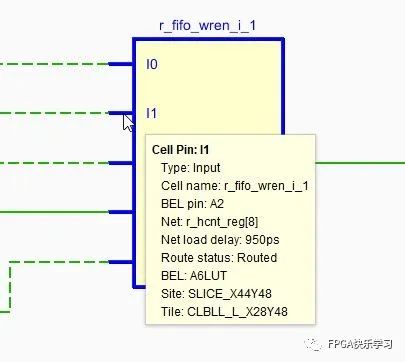

当我们把鼠标停留在LUT的某个逻辑输入端口上,就可以看到该逻辑输入端口的相关信息。如图所示,I1的信息中显示,它所对应的BEL pin,即物理输入端口是A2。这是默认FPGA布局布线的结果。

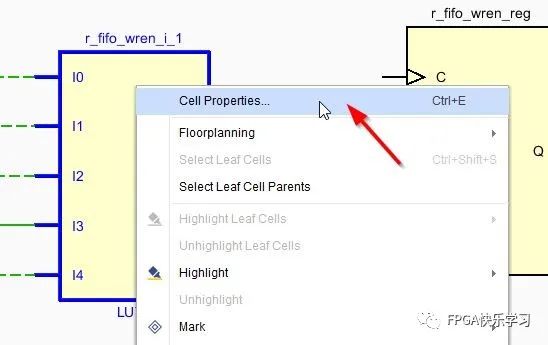

此时可以在r_fifo_wren_i_5这个LUT上右键单击,弹出菜单中再点击Cell Properties…打开它的属性信息进行查看。

在属性的Cell Pins页面中,可以看到Name(即LUT逻辑输入端口)、BELPin(即LUT物理输入端口)以及Net(实际设计中布线信号的网络名称)之间的映射关系。

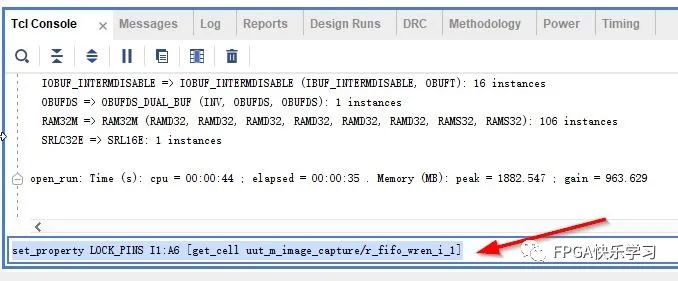

此时,我们可以在Tcl Console中输入以下脚本并回车运行,使用LOCK_PINS约束将I1和A6映射在一起,也就是I1不再和A2连接,A6也不再和I0连接。

set_property LOCK_PINS I1:A6 [get_celluut_m_image_capture/r_fifo_wren_i_1]

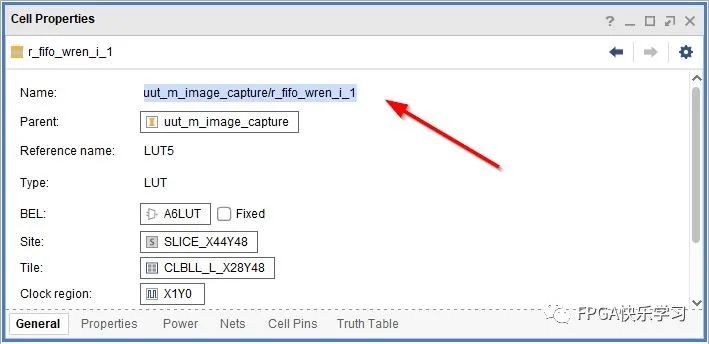

好奇的你或许想知道脚本中get_cell后接的一串路径名称从何而得?如图所示,在属性的General页面中Name一栏,就是目标LUT的名称uut_m_image_capture/r_fifo_wren_i_1。

在约束后,I1一定与A6连接在一起了,至于I0和A2是否会连接在一起,或者会不会因为我们的约束而打乱了其它逻辑输入端口和物理输入端口之间的映射关系,就由Vivado的算法自己决定了。

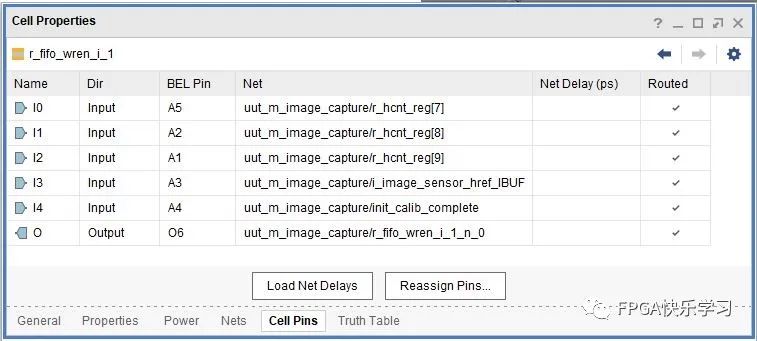

如图所示,对于当前的实例,最终I1与A6连接在一起,而I0则连接到了A5,而不是A2。大家不用觉得奇怪,因为我们只约束了I1和A6,其它逻辑和物理端口之间任何的连接映射关系都是有可能出现的。

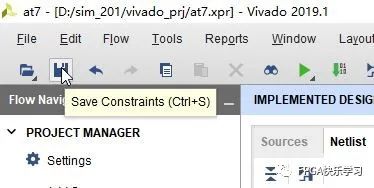

与时序约束一样,网表约束LOCK_PINS虽然是物理约束,但本质上也是约束设计,在Tcl Console中运行后,需要点击Save Constrains保存到.xdc约束脚本中才会最终生效。

如果我们要约束多对LUT逻辑和物理端口的映射关系,则可以运行类似如下的脚本。

set example_lut[get_cells uut_m_image_capture/r_fifo_wren_i_1]

set_property LOCK_PINS {I0:A5 I1:A2} $example_lut

get_property LOCK_PINS $example_lut

如图所示,以上脚本将I0和A5、I1和A2分别映射连接在一起了。

审核编辑:汤梓红

-

FPGA

+关注

关注

1664文章

22504浏览量

639305 -

端口

+关注

关注

4文章

1110浏览量

34051 -

约束

+关注

关注

0文章

83浏览量

13209 -

网表

+关注

关注

0文章

15浏览量

7967

原文标题:物理约束实践:网表约束LOCK_PINS

文章出处:【微信号:FPGA快乐学习,微信公众号:FPGA快乐学习】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

时序约束之时序例外约束

物理约束之布局约束

Adam Taylor玩转MicroZed系列74:物理约束

FPGA时序约束案例:伪路径约束介绍

FPGA案例之衍生时钟约束

物理约束实践:网表约束LOCK_PINS

物理约束实践:网表约束LOCK_PINS

评论