据麦姆斯咨询报道,高性能时钟器件供应商Pearl Semiconductor近日发布了首款真正意义上的单芯片参考时钟平台。这项被称为SingleDie的技术突破,将MEMS表面声波(SAW)谐振器嵌入同一芯片上更大的CMOS集成电路中,实现了一种极低噪声的片上参考时钟平台,适用于汽车和工业等各种恶劣环境中的一系列应用。

Pearl Semiconductor开发的SingleDie技术是其与SilTerra(马来西亚一家纯代工服务公司)多年合作的成果。Pearl Semiconductor通过利用SilTerra的氮化铝(AlN)压电SAW MEMS技术(该技术可在CMOS上提供高性能集成),在其CMOS芯片上构建MEMS谐振器。SilTerra拥有符合汽车IATF16949:2016标准的生产设施。

Pearl Semiconductor基于SilTerra的CMOS技术构建了一种可编程和环境补偿的硅参考时钟开发平台,可实现低于400 fs的抖动性能;频率高达1 GHz;高抗冲击和抗振性能;工作温度高达125℃,稳定性优于15 ppm。

SilTerra首席商务办公室(CBO)高级副总裁Arjun Kumar Kantimahanti表示:“Pearl Semiconductor的新方案带来了一种非常强大的单芯片技术,定位于汽车和工业半导体时钟解决方案不断增长的需求。展望未来,通过利用SilTerra的MEMS技术,我们相信Pearl能够提供极具成本竞争力的高性能解决方案,为指定市场提供更优质的服务。”

Pearl Semiconductor首席执行官Ayman Ahmed表示:“这代表了时钟解决方案新时代的开始,参考时钟可以集成到同一芯片中,以实现更高的性能和更低的成本。与SilTerra合作为开发并优化这项独特的技术提供了宝贵的机遇。Pearl的SingleDie技术有望实现变革,构建全球首款实现高集成度和安全性的时钟芯粒(chiplet)。”

2004年,Ayman Ahmed作为创始人之一创立了Si-Ware Systems公司,然后发起了时钟业务部,并于2020年拆分出来成立了Pearl Semiconductor。

这一突破为时钟解决方案市场带来了第一款真正的单芯片技术。传统上,参考时钟采用物理分离的谐振器构建,需要两个芯片或两个组件,使供应链变得更复杂,并限制了封装的选择空间。

利用Pearl Semiconductor的SingleDie技术,其MEMS SAW谐振器通过CMOS器件顶部的额外掩模层构建,占位面积更小,确保零热延迟,并降低了材料成本。

目前,该技术已经在行业标准的陶瓷封装中得到了验证,其未来的路线图上还有更小的塑料封装,将成为全球第一款高性能单芯片可编程参考时钟芯粒(chiplet)。

市场研究显示,芯粒(chiplet)将成为很多应用开发下一代汽车平台和电子产品的标准构建模块。在硬件低成本定制化需求的推动下,到2031年全球芯粒市场预计将以每年41%的速度增长,市场规模预计将增长至472亿美元。

审核编辑:刘清

-

CMOS

+关注

关注

58文章

6233浏览量

243404 -

SAW

+关注

关注

11文章

155浏览量

28589 -

MEMS谐振器

+关注

关注

0文章

8浏览量

7893

原文标题:集成MEMS氮化铝SAW谐振器的片上参考时钟平台诞生

文章出处:【微信号:MEMSensor,微信公众号:MEMS】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

CAT5115:32抽头数字可编程电位器解析

CDCE18005:高性能可编程时钟缓冲器的深度剖析

深入解析 CDCE949-Q1:可编程 4-PLL VCXO 时钟合成器

CDCEL824可编程2 - PLL时钟合成器:设计与应用指南

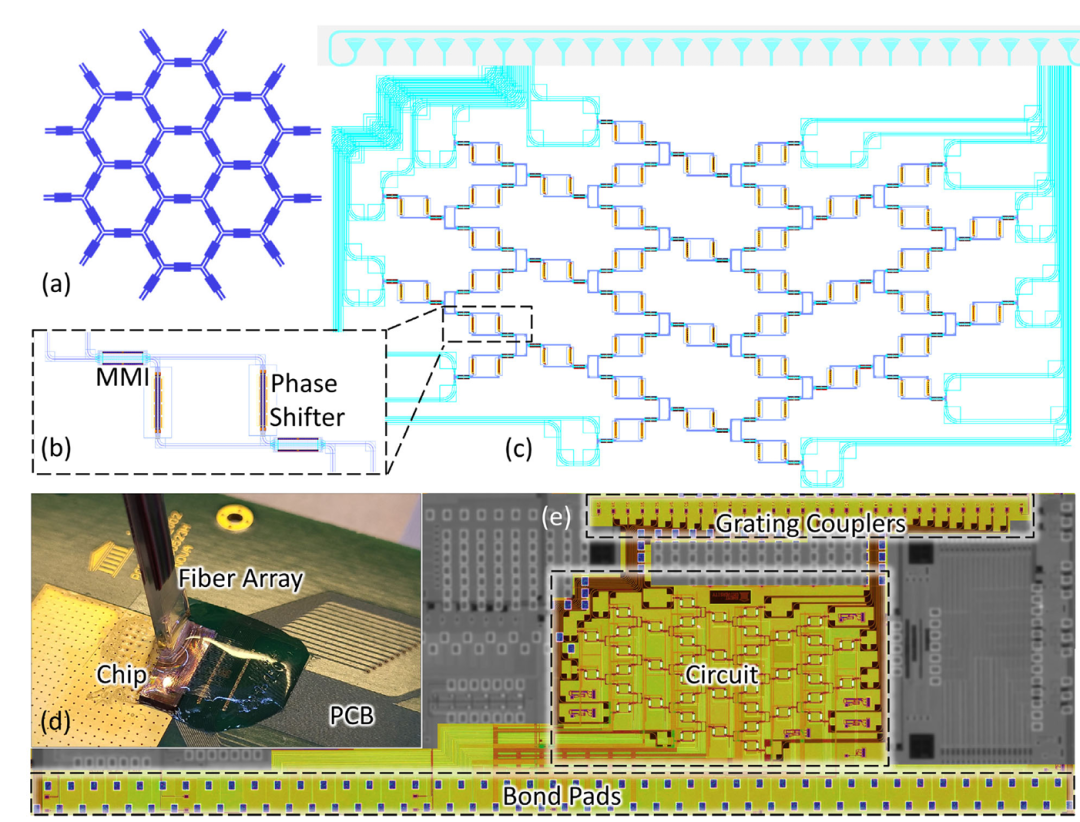

基于六边形波导网格架构实现可编程光子技术

思尔芯邀您共聚 FPT 2025,赋能可编程技术新未来

CDCE925 可编程 2-PLL VCXO 时钟合成器技术手册

CDCE913 可编程1PLL VCXO时钟合成器技术手册

CDCE937 可编程 3-PLL VCXO 时钟合成器技术手册

CDCE18005可编程时钟缓冲器技术文档摘要

CDCEL913-Q1 汽车目录可编程 1-PLL VCXO 时钟合成器技术手册

CDCE937-Q1/CDCEL937-Q1 可编程时钟合成器技术文档总结

CDCE913-Q1和CDCEL913-Q1可编程时钟合成器技术文档总结

CDCEL824 可编程双PLL时钟合成器技术文档总结

基于CMOS技术构建一种可编程和环境补偿的硅参考时钟开发平台

基于CMOS技术构建一种可编程和环境补偿的硅参考时钟开发平台

评论