随着行业对尽可能减少和消除浪费的重视,系统设计师有责任优化整体电源架构。每个电子设备都有一个供电网络 (PDN),通常包括但不限于线缆、母线排、连接器、电路板铜箔电源层、 AC - DC 和 DC - DC 转换器及稳压器。该网络中的每个组件都会影响设计功能的好坏,因为它将遇到线路、负载和环境的变化。

过去,电源架构一直在产品开发的后期阶段确定,这时候空间和选项已经受限。将架构设计安排在该流程早期阶段的更积极主动的方法,有助于创建更稳健的系统,可在开发过程中适应不断变化的设计规格。

电源设计人员经常关注转换,以便最大限度提高转换效率并最大限度降低功耗。主要驱动因素是热管理,因为转换阶段通常是热负荷的最大来源之一。高功耗需要更复杂、更广泛的散热方法,这都将增加成本和尺寸,特别是恶劣环境下的应用。

耗散功率是输入功率和输出功率之间的差值。一种是通过将电源转换器的额定功率除以其十进制等效效率来确定电源转换器的耗散功率:一个额定功率为 100W、效率为 80% 的转换器,将具有 125W 的输入功率和 25W 的耗散功率。必须以这种方式考虑系统中的每个元件,以确定系统的总损耗,这一点至关重要。提高效率,即使提高一点点,也能显著降低损耗。例如,效率提高 10 个百分点(在本示例中,提高到 90%),可能看起来并不多,但这会将功耗降低一半以上:从 25W 降至 11.1W。

这种效率的提高对供电网络有何影响?除了降低转换器的热影响外,还会减少对输入电源的需求,需要提供的电源更少。此外,这种较低的功耗还意味着:给定输入电压时,电源电流也更低。按照欧姆定律,可将功耗看成电压和电流的乘积,以及电阻和电流平方的乘积(P = VI = I2R)。在供电网络的分析中,电阻经常被忽略。从电源到负载的所有路径都有固定的电阻。它们都与总系统的功耗有关。此外,还必须考虑安全及稳定性组件,这些组件是整体功耗的主要来源,其中包括保险丝、断路器以及用于减少电磁干扰并让电压平稳的滤波器。在所有这些元件中,都有一个压降损失,会降低开关稳压器的稳定性,并在系统内产生其它问题。

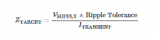

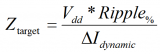

如 CPU、脉冲负载或电机等功率波动较大的终端设备(供电网络供电的设备)将导致转换器输入输出的电压出现显著变化。一般而言,转换器遇到的电源阻抗应该比转换器呈现的最低阻抗小 10 倍。

回到效率为 90% 的 100W 转换器示例中,假设该器件的工作输入范围是 18 至 36V。输入为 18V 时,转换器的输出电流约为 6.2A。因此,转换器的输入阻抗 (R) 为 V/I 或 18/6.2 = 2.9Ω。36V 时,输入电流为一半,因此阻抗是 11.7Ω。在转换器的输入阻抗最低时,根据经验,确保稳定工作的电源阻抗不应该超过 0.29Ω。

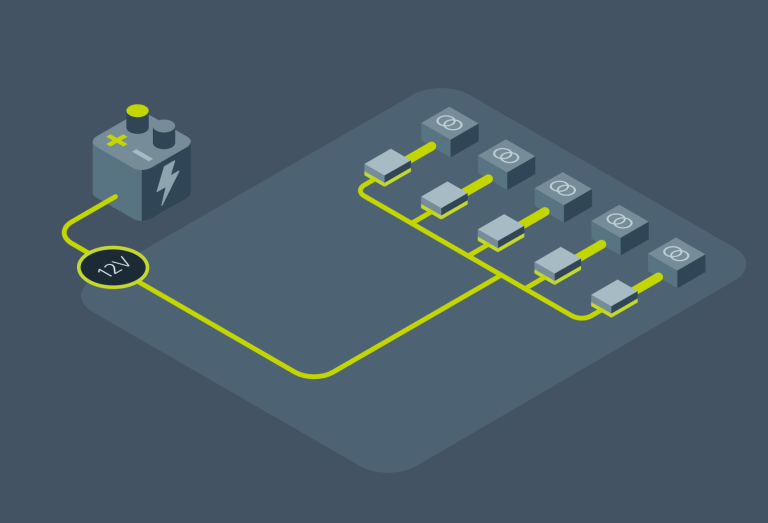

图 1: 一个 12V 低压 PDN 为 5 个独立负载供电。在本示例中,负载为低电压(不足 5VDC),在这些负载和转换器之间流动的电流较大(由粗线迹显示)。

需要注意的是,在设计电源系统时,系统稳定性很重要。这种简单的电阻讨论没有考虑到电阻元件,例如电容和电感,如果理解不好,这些电阻元件可能的确会引起共振及其它问题,这是显而易见的。本文不讨论这些主题。

如何优化与系统功耗息息相关的 PDN?

无论是分析现有的设计,还是从头创建一个新的架构,方法都一样。

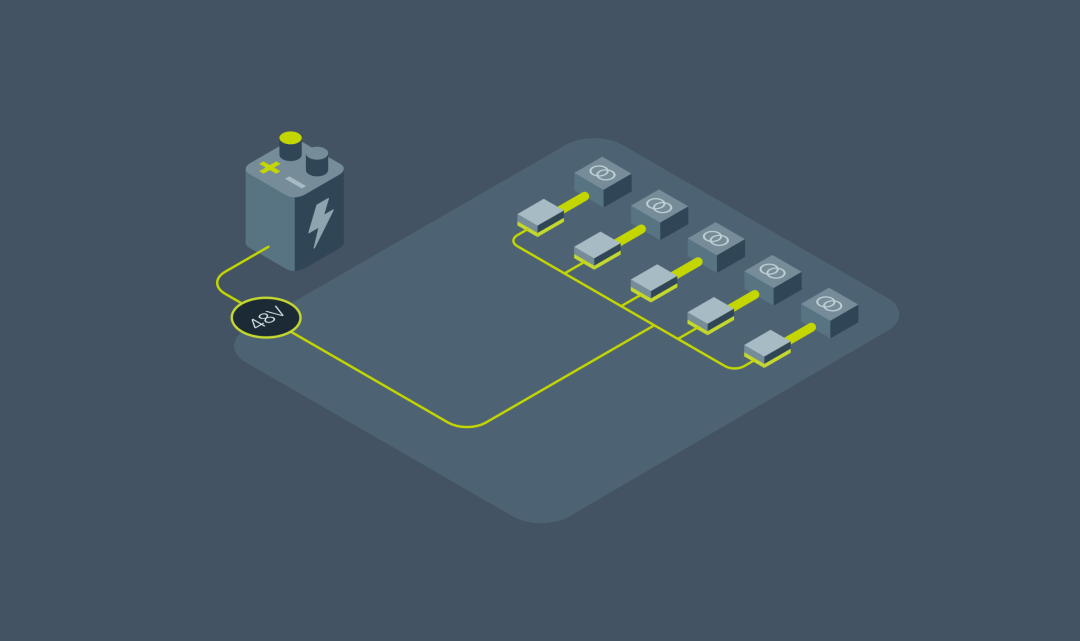

图 2: 改进的 PDN,电源电压从 12VDC 提高到 48VDC。这 5 个独立负载的电流要求与第一个示例所示的一样。由于较高的电源电压,从电池流到转换的电流较低(用细线迹表示)。

首先:尽管听起来可能很明显,但也请使用所提供的最高效转换器。分两部分考虑 PDN:从实际应用负载到第一个转换(包括所有中间转换)的输出,以及从电源到第一个转换的输入。

应用负载将具有预先确定的最小电压要求。现代电子系统的电流需求可能很高,在某些情况下,在不足 1V 的电压下,可能会超过 1000A。为了将这些应用中的损耗降到最低,负载点 (PoL) 转换器一般布置在用电负载附近。

PoL 避免了转换器和负载之间很长的布线距离,这是常规电源的特征,而且提供精确电压电源,满足低电压/大电流的需求。PoL 应该尽可能靠近其供电负载的物理位置,以尽量减少互连电阻。

向输入方向靠近时,PoL 输入电压应尽可能高。考虑一个为 5 个独立负载供电的 12V 低电压 PDN。在本示例中,负载为低电压(不足 5VDC),在这些负载和转换器之间流动的电流较大。

这样的设置可以是传统的计算机电源、车载电源系统,也可以是无人机有效载荷。PoL输入端存在固定的路劲电阻,将带来给定工作功率等级下的特定功耗。如果我们能在相同的功率下将电压提高 4 倍(即 48V),这条线路上流过的电流现在就是之前的四分之一。由于功率方程式中有电流的平方项,因此新功耗会显著减少,电压偏差也会降低。

此外,48V 是良好的配电电压,因为它也在安全超低电压 (SELV) 的限制范围内, IEC 将其定义为具有低触电风险。对于现有应用而言,提高电压需要不同的 PoL。在这里,使用封装尺寸相同器件的模块化方法将是一项轻松的转换,因为转换器将是直接替换件。

示例:系留无人机供电网络

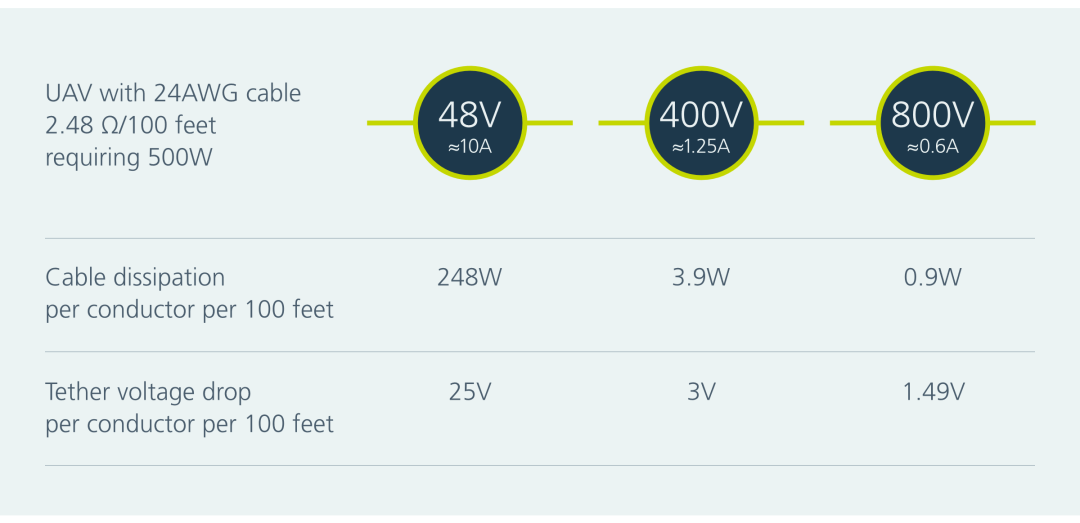

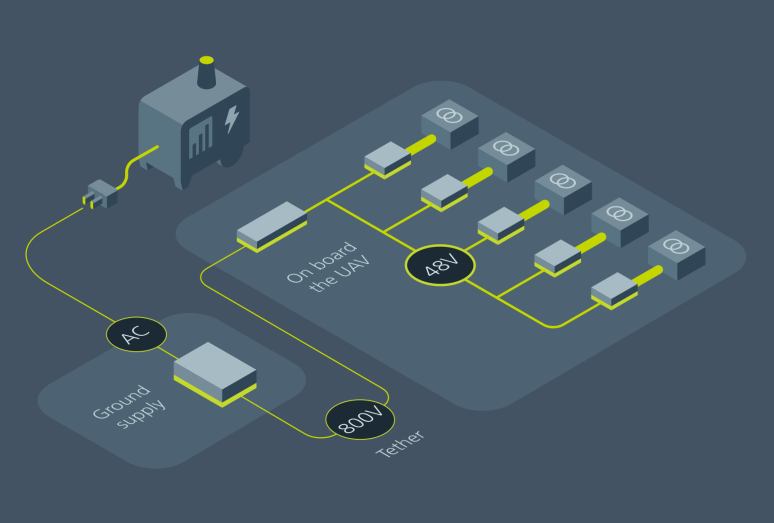

图 3: 上面是针对要求 500W 功率的机载工具,在每个系线导体中的不同电源电压下,比较电流、压降和功耗降低情况。下面是从地面电源至机载工具的优化系留无人机 PDN。系线内使用的 800V 电压可最大限度减少无人机工作造成的重要传输损耗和电压变化。电流明显低于使用较低电源电压的电流,因此转而采用 800V 还有进一步的优势:允许使用更小规格的导体,可能会减少系线风偏和重量。

考虑系留无人机或无人机的一个更为极端的示例,具体来说,电源到第一次转换的影响。系线代表地面电源间的接口。

假设无人机系线长 100 英尺并包含 24A-WG 导线,每根导线的电阻约为 2.5Ω/100 英尺。在 48-V 配电时,该系线的电流约为 10A;100 英尺双向电阻是 5Ω,因此系线的功耗为 500W!显然,该无人机根本无法起飞,因为系线会耗尽所有电源,该飞行器无任何动力。

现在考虑使用更高的输入电压。假设 400V 系统与上述条件相同。

400V 配电时,系线电流会下降至约 1.25A,而且系线功耗仅为大约 8W。将输入增加一倍至 800V,会将系线电流降低至约 0.6A,从而可将系线功耗降低至约 2W。较低的抽电流有助于使用更小规格的系线导体,从而不仅可减少阻力和风偏,同时还可降低无人机对电力的需求。

功耗很重要,但系线末端的稳压也很重要。无人机上的稳压器会有一个定义好的输入电压范围。系线电阻有压降。鉴于 24A-WG 100 英尺的系线以及其 5-Ω 往返电阻,每安培电流有 5V 的压降。此外,减少系线上的压降,也可降低压降与所用电压的比率,从而可进一步改善稳压:如果电压翻倍、电流减半,系线上的压降也会减半,而且系线压降与负载电压的比率则为四分之一。

显然,将地面电源增加至 800V,是优化通过系线传输电力的途径。但无人机必须将这 800V 的电压降压转换为低电压,才能为其电机和电子设备供电。对于 PDN 的这一部分,机载电子设备的 48V 最有意义,原因如前所述。

综上所述,优化 PDN 的路径可以归纳为 6 个步骤:

01

先考虑电源。一旦有了最初的电源需求,就得为模块化电源设计预留空间。模块化方法不仅灵活,而且扩展也很便捷。

02

请注意电流路径中的每个元件。

03

使用允许的最高电压,减少所需的电流。

04

使用最高效的转换元件降低转换损耗。

05

使用最高功率密度的器件,以便接近负载布置。

06

尽量减少互连电阻,这不仅可降低压降,而且还可降低功耗。

审核编辑 :李倩

-

转换器

+关注

关注

27文章

9448浏览量

156963 -

PDN

+关注

关注

0文章

86浏览量

23501 -

电源架构

+关注

关注

0文章

35浏览量

9102

原文标题:优化供电网络的一些经验法则

文章出处:【微信号:Vicor,微信公众号:Vicor】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

从翻转率入手优化FPGA功耗

使用MPS MPQ8785负载点器件实现PDN阻抗容限要求

请问如何优化芯片的功耗管理?

低功耗系统设计核心:VDD_EXT原理与优化策略详解!

NVSwitch芯片周围MLCC阵列的PDN阻抗优化方案

MCU时钟管理对功耗优化方向

为什么cortex-M0+功耗低?

如何优化设备功耗以保障外接备用电源时的数据实时传输?

如何通过优化电能质量在线监测装置的散热系统来降低功耗?

MDD 逻辑IC的功耗管理与优化策略

如何优化与系统功耗息息相关的PDN?

如何优化与系统功耗息息相关的PDN?

评论