在电信设备高频化、高功率需求日益迫切的今天,电源传输网络(PDN)的稳定性直接决定了芯片能否在复杂工况下正常运行。而 “目标阻抗” 作为 PDN 设计的核心基准,更是衡量供电可靠性的关键指标 —— 它能确保芯片即便面临最差瞬态电流,电源轨电压噪声也能控制在可接受范围。

今天就来拆解 PDN 优化的核心逻辑,分享如何用MPQ8785负载点(PoL)器件实现阻抗容限要求,还附实战案例喔!

先搞懂:什么是 PDN 目标阻抗?

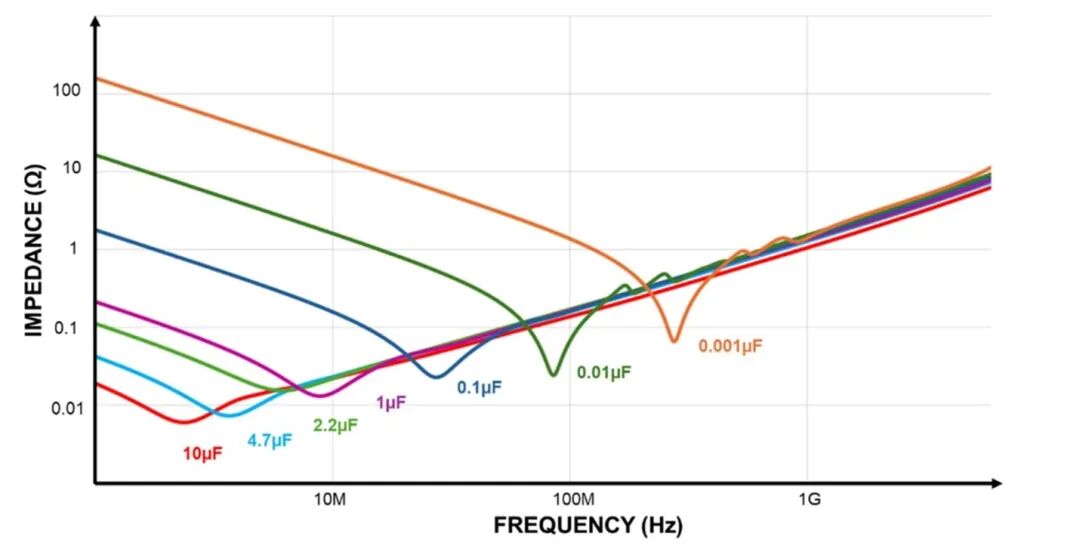

简单说,目标阻抗(Z (TARGET))是电源轨允许的最大阻抗阈值,核心作用是 “压制噪声”。它的计算逻辑很直接:目标阻抗 = 最大允许纹波电压 ÷ 最大预期电流阶跃负载

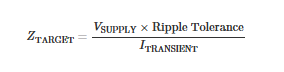

要让全频段阻抗都低于这个阈值,需要两大关键:低频段靠电源调节器支撑,中高频段则依赖去耦电容的精准选型与布局(比如 MLCC 多层陶瓷电容,其阻抗会随频率变化,需针对性匹配)。

图1:MLCC的阻抗频率特性

不同频段对阻抗的要求不同,配电网中每个元件都得在对应频段优化—— 这也是 PDN 设计的核心难点之一。

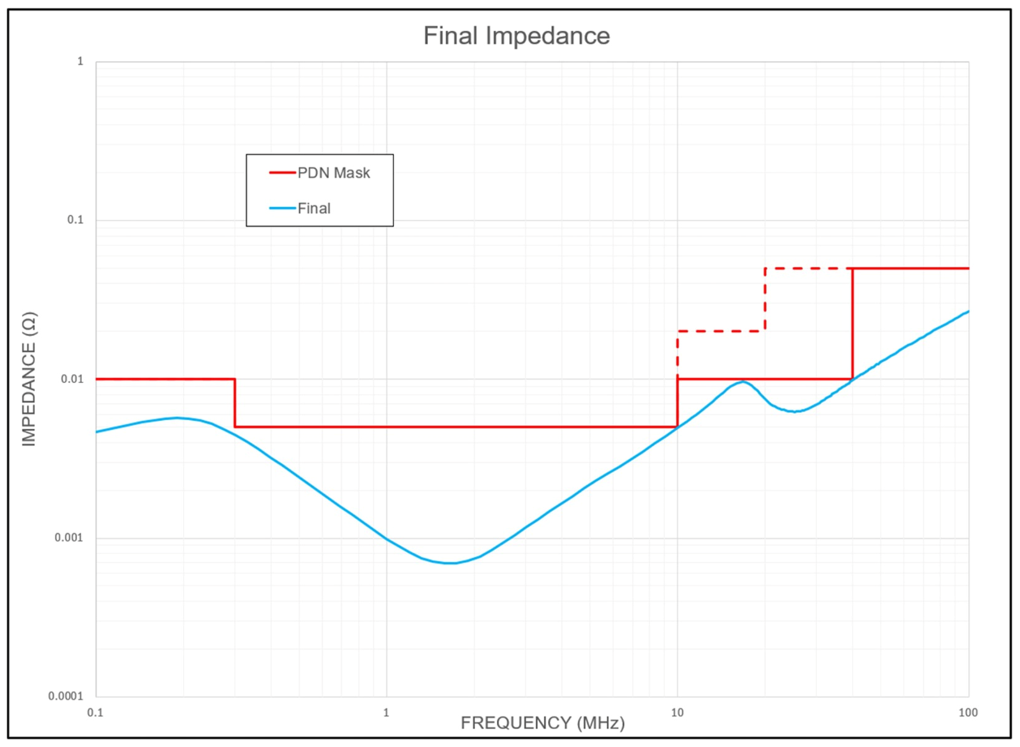

图2:目标阻抗示例

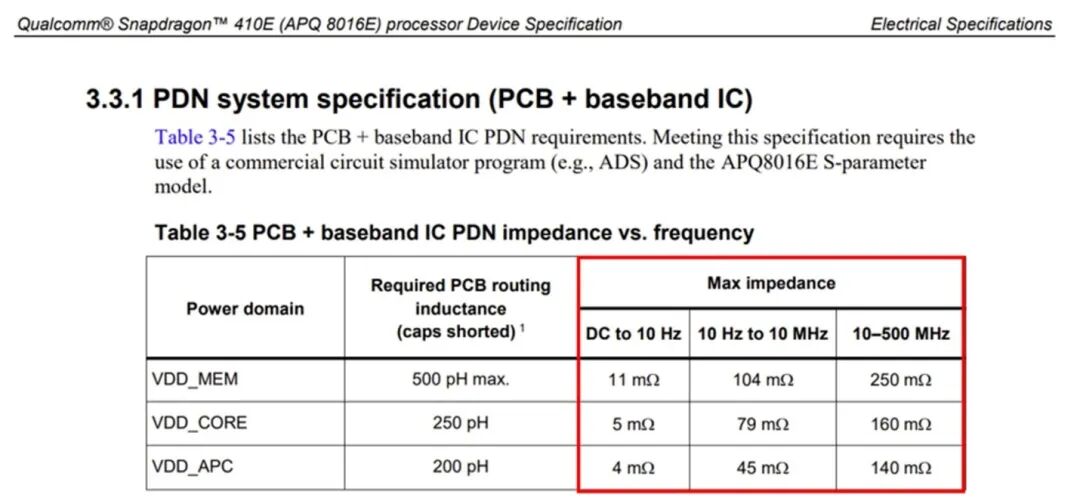

PDN 优化新思路:三级低通滤波器法

理想的 “零阻抗” PDN 不现实,传统堆去耦电容的方式也未必高效。其实可以把 PDN 看作三级低通滤波器,每一级各司其职,针对性降低不同频段阻抗:

图3:将PDN概念化为三级低通滤波器

1封装滤波:电流的 “第一道降噪门”

从 SoC 晶片汲取的电流,会先经过封装与晶片侧电容(DSC)的配合,初步降低电流斜率,相当于给瞬态电流 “减速”,减少噪声传导。

2PCB 层 + MLCC:中高频段的 “核心滤波层”

电流通过 BGA 后,会流经 PCB 电源层并与 MLCC 作用。这里的关键是:电容要选对频率特性 —— SoC 下方的高频电容只对特定频段有效,对低频调节作用甚微,无需盲目堆砌。

3电压调节器(VR)+ 大电容:低频噪声 “稳定器”

最后一级由 VR 和大电容联手,重点压制低频噪声,为电源轨提供基础稳定性,确保整体供电的平稳性。

这种结构化设计,能让每个组件都精准覆盖对应频段,比无序堆电容更高效、更可靠。

实战案例:MPQ8785 评估板如何达标?

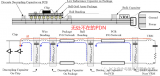

光说理论不够,我们用 MPS 电信专用评估板(搭载高频同步降压变换器MPQ8785)做实测,看看如何通过电容选型与布局,让 PDN 阻抗满足容限要求。

图4:MPS电信评估板

第一步:提取参数,发现问题

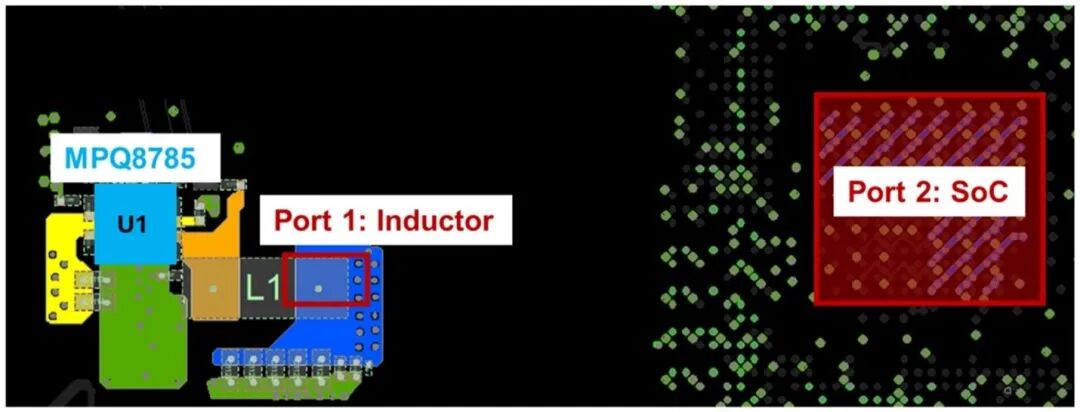

先获取 PCB 寄生参数(含电容的 ESL、ESR 等),选择两个关键端口分析:端口 1 在电感后方,端口 2 连接 SoC BGA。通过实测发现:初始电容配置下,300kHz~600kHz 频段的阻抗超出了规定限值,这是核心优化点。

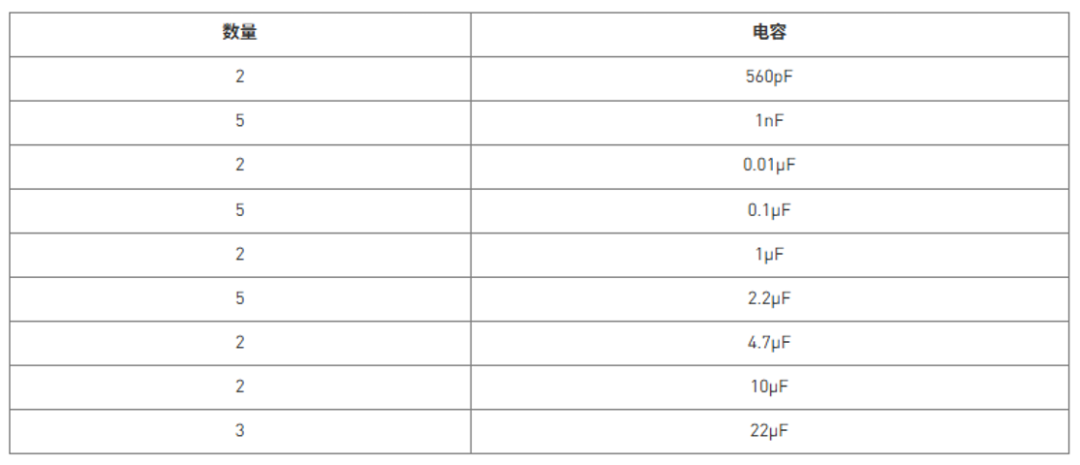

表1:初始电容选型方案

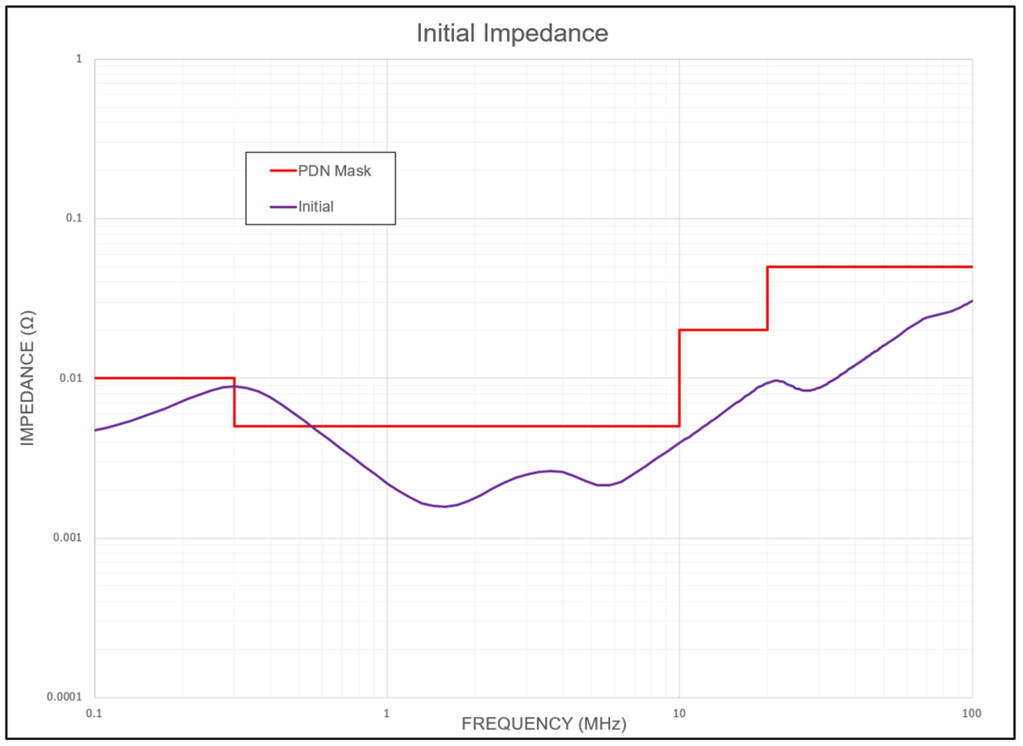

图5:目标阻抗曲线与初始阻抗的对比

第二步:迭代选型,精准优化

高频电容只对特定频段有效,盲目增加没用。我们通过多次仿真,筛选出最佳电容组合(兼顾数量与类型):

针对超标频段,补充特定规格电容,直接拉低阻抗;

10MHz 以上频段有充足裕度,果断省去多余高频电容,既节省板面积,又降低成本。

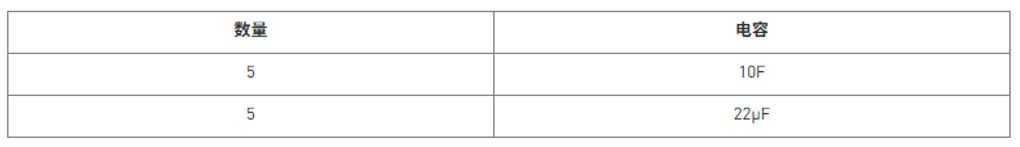

表2:最佳电容选型

图6:电容优化后的最终阻抗

第三步:验证结果,完美达标

优化后的 PDN 阻抗曲线,全频段都符合容限要求!甚至在后续测试中,我们把 10MHz~40MHz 的阻抗容限要求降至 10mΩ,只需额外添加 10 个 0.1µF 电容,就能轻松满足。

图7:电容优化后的阻抗,可降低PDN容限要求

这充分说明:只要选对电容、布对位置,配合MPQ8785的高性能,就能在 “性能、成本、空间” 三者间找到完美平衡。

PDN 优化的核心,不是 “堆更多电容”,而是 “让每个组件在对应频段发挥最大作用”。通过三级低通滤波器法的结构化设计,再加上MPQ8785的高频优势,就能高效满足阻抗容限要求,为电信设备提供稳定、可靠的电力传输。

如果你在 PDN 设计中遇到阻抗超标、电容选型纠结等问题,欢迎在评论区交流!

-

滤波器

+关注

关注

162文章

8470浏览量

186286 -

负载点

+关注

关注

1文章

20浏览量

8634 -

PDN

+关注

关注

0文章

86浏览量

23505

原文标题:PDN 阻抗不达标?用 MPQ8785 这样优化,电信设备供电稳了!

文章出处:【微信号:MPS芯源系统,微信公众号:MPS芯源系统】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

搞定电源完整性,不如先研究PDN!

PCB电源完整性的双面视角,用一篇文章理清时域电源噪声与频域PDN阻抗的关系

PDN设计的目的

基于可分解的多目标进化算法的PDN阻抗的优化

PDN设计

PDN 环路电感对纹波和总阻抗有何影响?

MPS车规级三相门级驱动解决方案——MPQ6533

PDN 元件对阻抗的影响

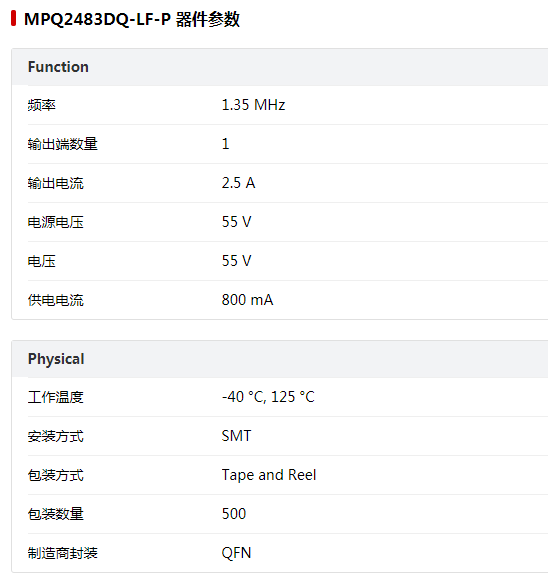

Monolithic Power Systems (MPS)MPQ2483DQ-LF-P PWM LED驱动IC的参数特性 EDA模型和数据手册分享

NVSwitch芯片周围MLCC阵列的PDN阻抗优化方案

使用MPS MPQ8785负载点器件实现PDN阻抗容限要求

使用MPS MPQ8785负载点器件实现PDN阻抗容限要求

评论