内容提要

8nm 射频集成电路流程支持射频集成电路设计过程的所有阶段,包括建模、兼顾电磁影响的 RF 仿真和完整签核验证流程

该流程加速了射频集成电路设计,有助于驱动广泛的 5G 应用

中国上海,2022 年 10 月 17 日 —— 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,Samsung Foundry 已认证 8nm 射频集成电路设计参考流程,以开发 6GHz 以下至毫米波(mmWave)应用的 5G 射频集成电路。该流程采用先进的设计方法,具备独特的功能,有助于提高生产力,提供全面的电气分析并加快设计收敛,帮助客户一次性成功设计出高质量的射频集成电路。新流程将支持 Cadence 和 Samsung Foundry 的共同客户满足全球对 5G 客户端设备日益增长的需求,包括智能手机和通信基础设施设备,如蜂窝基站。

利用该设计流程,客户可以针对使用三星 8nm RF 工艺技术设计的集成电路,快捷地对比电路前仿和识别设计时的电磁效应,并完成版图寄生参数提取的后仿结果。该 8nm 射频集成电路流程是三星最新推出的技术,进一步补充了其广泛的 RF 解决方案产品组合。

Cadence 是业界公认的先进节点 RFIC 设计、版图和验证领域的领导者。Cadence® Virtuoso® RF Solution 基于经过硅验证的仿真引擎,在时域和频域范围提供射频分析。8nm 射频集成电路设计参考流程中支持的 Cadence 产品包括:

Spectre® RF Simulator

Quantus™ Extraction Solution

Pegasus™ Physical Verification System

EMX® Planar 3D solver

有关 Cadence 射频集成电路设计解决方案的更多信息,请访问:www.cadence.com/go/rfic8nm

“在 Samsung Foundry,我们一直努力为客户提供功能丰富的高性能技术和高效的设计流程,”三星电子代工设计技术团队副总裁 Sang-Yoon Kim 说,“我们的技术与 Cadence 射频集成电路工具流程相辅相成,为低功耗、高性能的射频集成电路设计设定了新的标准,助力我们众多的共同客户开发出高质量的射频集成电路。”

“Cadence 始终致力于推动先进节点集成电路设计的创新,在过去十年中,我们一直是工艺技术发展的关键推动者,”Cadence 公司高级副总裁兼定制 IC 与 PCB 事业部总经理 Tom Beckley 表示,“在射频集成电路领域,我们也延续了这种技术创新和领导地位。Cadence 和三星有着共同的客户,他们都在寻找创新的集成电路设计解决方案,以便设计和交付面向 5G 应用的新一代射频集成电路。”

关于 Cadence

Cadence 在计算软件领域拥有超过 30 年的专业经验,是电子系统设计产业的关键领导者。基于公司的智能系统设计战略,Cadence 致力于提供软件、硬件和 IP 产品,助力电子设计从概念成为现实。Cadence 的客户遍布全球,皆为最具创新能力的企业,他们向超大规模计算、5G 通讯、汽车、移动设备、航空、消费电子、工业和医疗等最具活力的应用市场交付从芯片、电路板到完整系统的卓越电子产品。Cadence 已连续八年名列美国财富杂志评选的 100 家最适合工作的公司。

文章转载自:爱集微

-

Cadence

+关注

关注

68文章

1031浏览量

147389 -

射频集成电路

+关注

关注

5文章

29浏览量

17386

发布评论请先 登录

集成电路制造中的前道、中道和后道工艺介绍

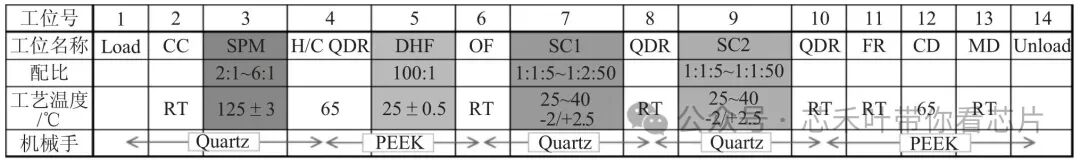

半导体制造中刻蚀工艺技术介绍

奇捷科技邀您共赴ICCAD-Expo 2025

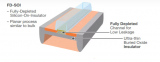

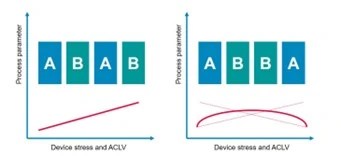

SOI工艺技术介绍

集成电路制造中薄膜刻蚀的概念和工艺流程

PDK在集成电路领域的定义、组成和作用

集成电路传统封装技术的材料与工艺

华大九天Empyrean Liberal工具助力数字集成电路设计

新思科技携手是德科技推出AI驱动的射频设计迁移流程

Cadence携手台积公司,推出经过其A16和N2P工艺技术认证的设计解决方案,推动 AI 和 3D-IC芯片设计发展

通过交互式对称性校验提升集成电路设计流程

Cadence与Samsung Foundry合作认证面向 8nm 工艺技术的射频集成电路设计参考流程

Cadence与Samsung Foundry合作认证面向 8nm 工艺技术的射频集成电路设计参考流程

评论