来源:泛林集团

芯片已经无处不在:从手机和汽车到人工智能的云服务器,所有这些的每一次更新换代都在变得更快速、更智能、更强大。创建更先进的芯片通常涉及缩小晶体管和其他组件并将它们更紧密地封装在一起。然而,随着芯片特征变得更小,现有材料可能无法在所需厚度下实现相同性能,从而可能需要新的材料。

泛林集团发明了一种名为 SPARC 的全新沉积技术,用于制造具有改进电绝缘性能的新型碳化硅薄膜。重要的是,它可以沉积超薄层,并且在高深宽比的结构中保持性能,还不受工艺集成的影响,可以经受进一步处理。SPARC 将泛林无与伦比的等离子技术与化学和工艺工程相结合,实现了先进逻辑和 DRAM 集成设计的进一步发展。

提高逻辑器件性能

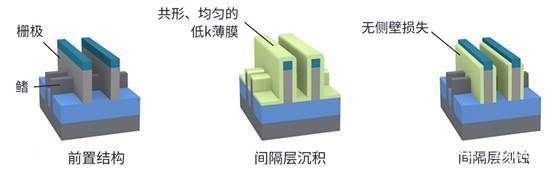

SPARC 的一个关键逻辑应用是 FinFET 间隔层。如下面的流程所示,间隔膜沉积在前置结构的栅极和鳍上。薄膜必须遵循现有结构的精确轮廓,并保持厚度一致(结构均匀性)。它还必须对下面的层具有出色的附着力,且没有针孔或其他缺陷。此外,除了在栅极侧壁的所需位置外,它还必须易于从其他任何地方移除。

薄膜本身就有要求。随着晶体管按比例缩小,栅极模块中的电容耦合会增加,从而降低整体晶体管的性能。SPARC 碳化物薄膜是电绝缘性能更佳的新型材料的绝佳例子,即所谓的“低k薄膜”,用于最大限度地减少这种耦合。现有的低k薄膜通常很脆弱,无法承受后续步骤中使用的强烈的化学物质,因而会导致整体芯片性能不佳。

泛林的 SPARC 技术可提供均匀、坚固的低k薄膜,其厚度和特征内部的成分都是均匀的。SPARC 薄膜被轻柔地沉积,没有直接的等离子体对下面的敏感器件造成损坏,它通过使用由具有远程等离子体和新型前驱体的独特反应器产生的自由基来实现。与直接等离子体增强原子层沉积 (ALD) 薄膜不同,它可以轻松调整薄膜成分,以更好地预防损坏,优化干法或湿法刻蚀的选择性。得到的薄膜很薄、无针孔,并且可以在芯片制造过程的其余环节保持正确的硅碳 (Si-C) 键合结构,从而保持其介电性能和坚固。

随着全包围栅极 (GAA) 架构的出现,泛林 SPARC 技术的价值变得愈加明显。新的内部间隔层应用需要一种材料来降低器件的寄生电容——即降低器件之间的干扰。该薄膜还必须在硅锗沟道释放过程中作为外延处理的源极/漏极的保护层。SPARC 沉积的薄膜为该应用带来了关键特性,包括低k值,均匀性,高图形负载,均匀厚度,对硅基、氧化物、碳类型材料的出色刻蚀选择性,以及器件中的极低泄漏。

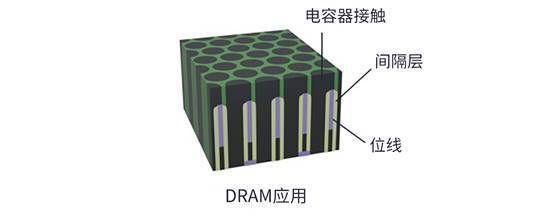

同样有利于 DRAM 架构

随着器件的微缩,工程师们不断努力减少位线和电容器触点之间的电容,以保持良好的信号/噪声进行位感应。位线深宽比的增加也使传统的沉积方法难以成功。位线电容的一个重要组成部分是位线和存储节点触点 (SNC) 之间的耦合,随着单位面积封装越来越多的器件以降低 DRAM 成本和增加密度,该耦合正在增加。为了减少这种耦合,自1x nm 技术节点以来,SPARC 沉积的低k间隔材料至关重要。

理想的低k薄膜

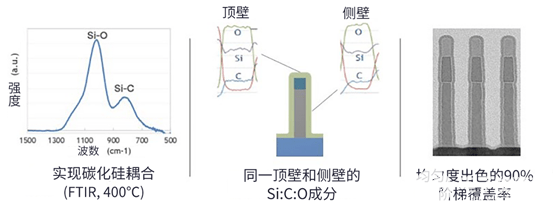

使用 SPARC 或单个前驱体活化自由基腔室技术制造的碳化硅氧化物 (SiCO) 薄膜具备密度大、坚固耐用、介电常数低 ~ 3.5-4.9、泄漏率低、厚度和成分共形性极佳等特点。在 250°C 至 600°C 的广泛温度范围内,碳完全交联,末端甲基极少甚至没有,与其他薄膜(如SiOC、SiOCN 或 SiCN)相比,该薄膜具有热稳定性和化学稳定性。

在 SPARC SiCO 系列中,远程等离子体、独特的前驱体和工艺空间可实现广泛的成分调整。此外,这些 SPARC SiCO 薄膜在稀氢氟酸和热磷酸等典型湿法化学物质中的 WER(湿法刻蚀速率)为零,因此还提供近乎无限的湿法刻蚀选择性。这些薄膜也是连续的且无针孔的,厚度低于普通替代的一半。

由于这些特性,SPARC SiCO 薄膜在某些间隔物应用中实现厚度最小化,是个很有吸引力的选择。鉴于其对高深宽比堆栈材料的显著湿法选择性或等离子体损伤预防,这些薄膜能够形成气隙,减少电容耦合,并保护高深宽比堆栈中容易氧化或损坏的工艺元件。SPARC 技术已被领先技术节点的所有主要逻辑/代工厂和 DRAM 制造商采用。随着集成度和性能扩展挑战的提升以及深宽比的提高,下一个节点应用程序空间预计将增加。

审核编辑 黄昊宇

-

DRAM

+关注

关注

41文章

2401浏览量

189549 -

SPARC

+关注

关注

0文章

16浏览量

10184

发布评论请先 登录

端侧AI“堆叠DRAM”技术,这些国内厂商发力!

从“不可能三角”到原子级沉积:安德科铭李建恒解读先进制程下薄膜材料的突围之路

应用材料AMAT/APPLIED MATERIALS Producer® XP Precision® CVD系列二手薄膜沉积CVD设备拆机/整机|现场验机评测

DRAM芯片选型,DRAM工作原理

什么是DRAM存储芯片

创新的高带宽DRAM解决方案

铠侠公布3D DRAM 技术

华邦电子推出先进 16nm 制程 8Gb DDR4 DRAM 专为工业与嵌入式应用而生

DRAM和SRAM、SDRAM相比有什么特点?

半导体外延和薄膜沉积有什么不同

DRAM代际交替中的技术赋能:德明利新一代高性能内存方案

详解原子层沉积薄膜制备技术

SPARC:用于先进逻辑和 DRAM 的全新沉积技术

SPARC:用于先进逻辑和 DRAM 的全新沉积技术

评论