文章来源:十二芯座

原文作者:MicroX

本文介绍了DRAM的结构和读取原理。

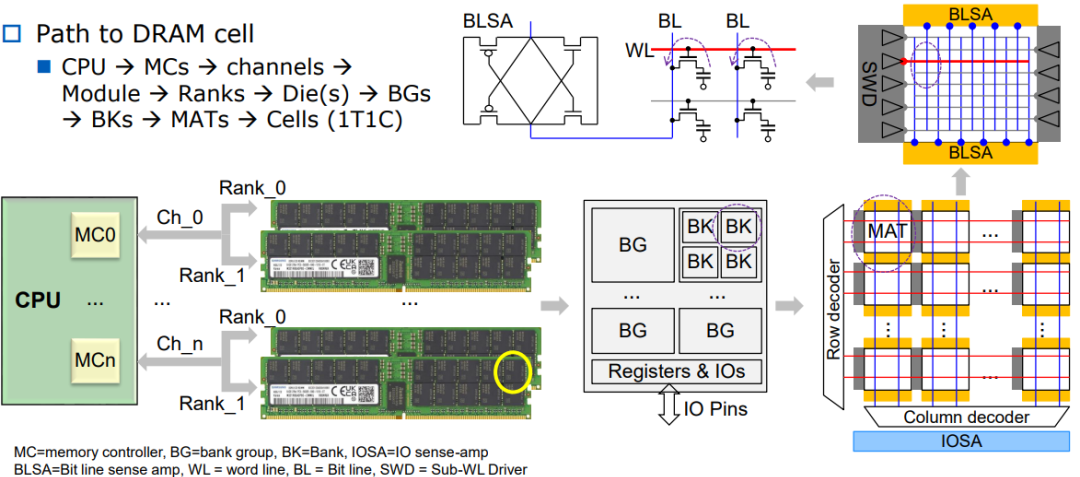

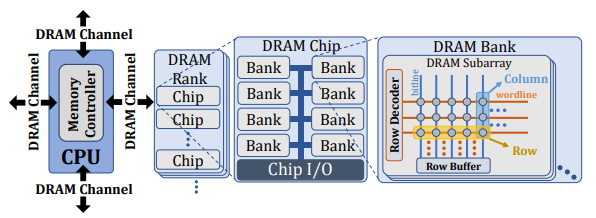

DRAM 组织结构

DRAM 被组织成层次化的阵列,总共由数十亿个 DRAM 单元组成,每个单元存储一位数据。

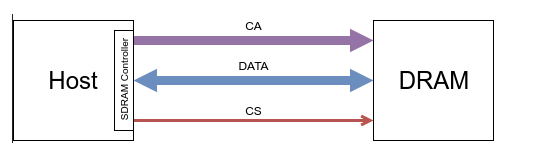

在现代系统中,CPU 芯片实现了一组内存控制器,每个内存控制器通过一个独立的 I/O 总线与一个 DRAM 通道对接,以执行读写及维护操作(eg.,refresh, RowHammer protection, memory scrubbing)。

该 I/O 总线与系统中的其他通道是独立的。一个 DRAM 通道可以承载一个或多个 DRAM 模块,每个模块由一个或多个 DRAM 层级(rank)组成。一个层级由多个 DRAM 芯片构成,这些芯片同步工作,同一通道内的不同层级分时共享该通道的 I/O 总线。

Fig1. 展示了现代 DRAM 系统的典型组织结构

一个 DRAM 芯片由多个 DRAM 存储体(bank)组成,这些存储体共享一个将它们连接到芯片 I/O 电路的内置总线。在一个 DRAM 存储体内,DRAM 单元被组织成多个(例如 128 个)密集的二维 DRAM 单元阵列,称为子阵列,以及用于操作子阵列内数据的相应外围电路。

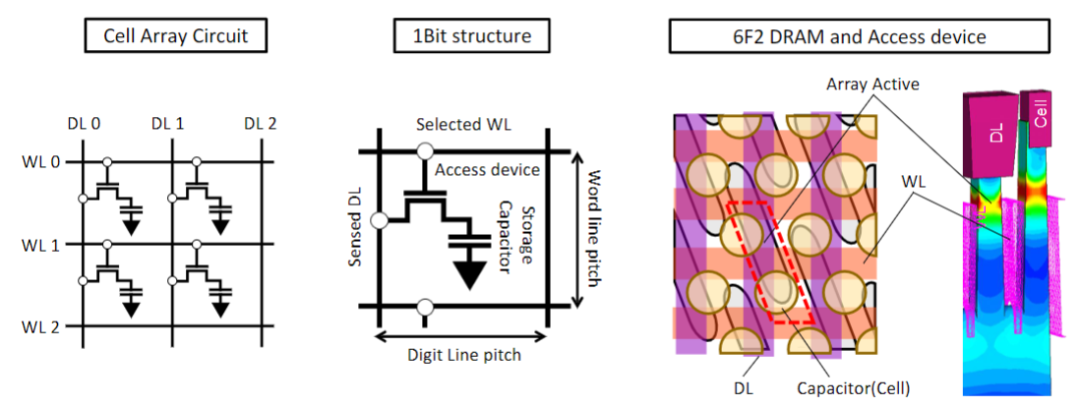

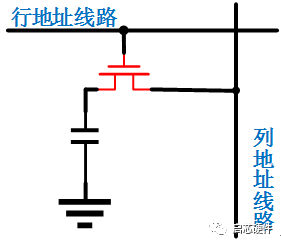

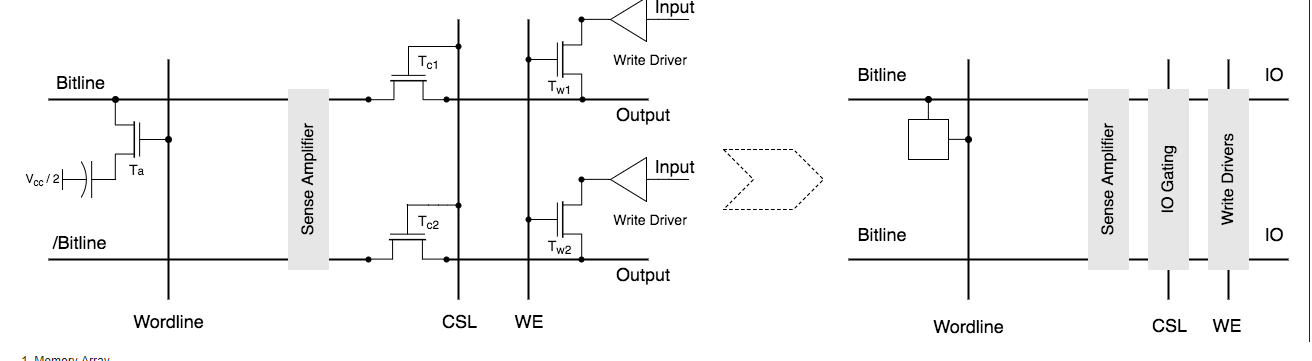

Fig2. 6F DRAM structure

子阵列内的单元行(即 DRAM 行)共享一条导线(即字线),该导线由行解码器驱动,以打开(即选中)待读取或写入的单元行。

子阵列内的单元列(即 DRAM 列)共享一条导线(即位线),该导线在行缓冲器(由感测放大器组成)的帮助下用于读写单元。

这种 DRAM 单元的层次化布局使得可以使用唯一的通道、层级、存储体、行和列地址来访问和更新 DRAM 系统中的任何数据。

DRAM Operation

内存控制器通过 I/O 总线发送一系列命令来与 DRAM 交互。

用于访问 DRAM 有四个主要命令:ACT、WR、RD 和 PRE。

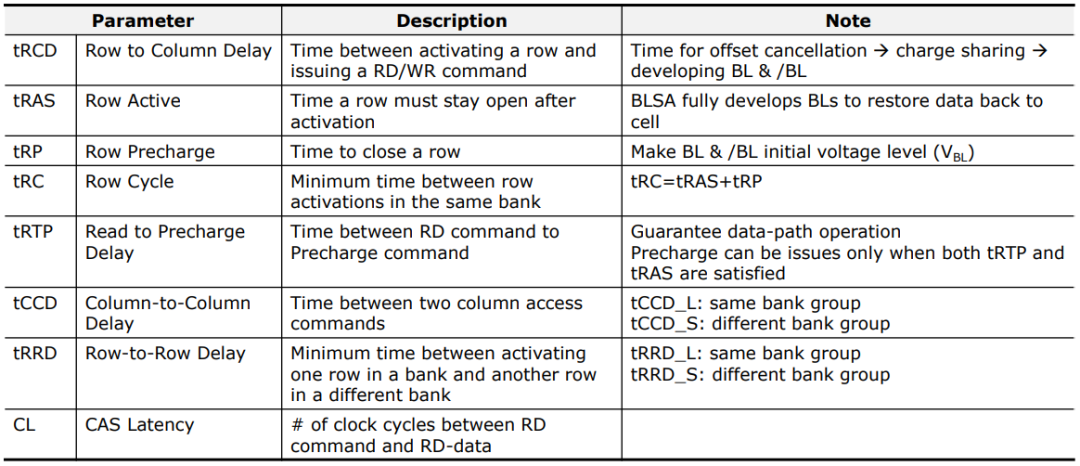

DRAM 命令调度受到一组时序参数的严格规范,这些参数确保在某个命令发出后经过足够的时间,以便 DRAM 能正确提供或保留数据。DRAM 命令和时序参数由 DRAM 标准定义,它们构成了内存控制器与 DRAM 芯片之间接口的一部分。

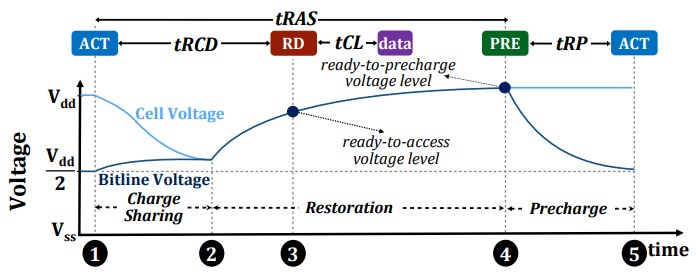

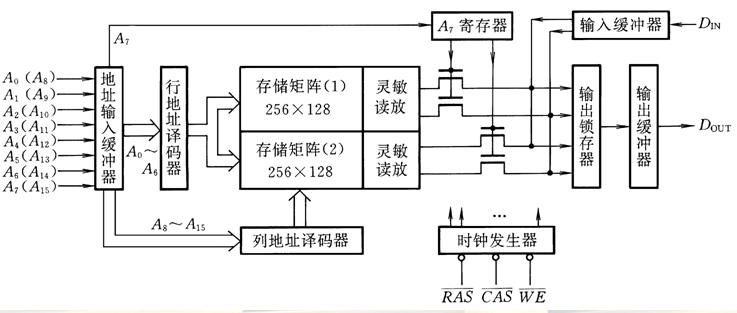

Fig3. Commands, timing parameters, and cell/bitline voltages during a DRAM read operation.

Fig3说明了执行一次 DRAM 读操作时,所发出的命令、其管辖的时序参数以及它们对单元和位线电压的影响。内存控制器在调度每个 DRAM 命令时强制执行相关的时序参数。除了 DRAM 访问命令外,内存控制器还会周期性地发出刷新(REF)命令,以防止因单元电容随时间泄漏电荷而导致的数据丢失。

激活命令-ACT

ACT 命令通过将单元电容中包含的数据传输到行缓冲器来激活(打开)一个 DRAM 行。ACT 延迟受 tRCD 时序参数约束,该参数确保自 ACT 命令发出后有足够的时间让数据在行缓冲器中稳定下来(以便可以通过发出 RD 命令来读取)。

ACT 包含两个主要步骤:

1) 电容-位线电荷共享

2) 电荷恢复。

电荷共享从启用字线开始(Fig3中的1),这使得单元电容能够与位线共享电荷,从而扰动预充电后的位线电压。一旦单元和位线电压由于电荷共享而达到均衡,电荷恢复开始(2)。在电荷恢复期间,感测放大器被启用,首先检测位线电压的偏移,然后根据偏移方向将位线恢复到完全的 Vss 或 Vdd 电压。一旦位线恢复到可访问的电压水平(3),就可以向该存储体发出其他 DRAM 命令(例如,RD、WR)。

读取命令-RD

在行激活之后,内存控制器通过发出 RD 命令从打开的行中读取数据。RD 命令包含一个列地址,该地址指示要读取的打开行的部分。当 DRAM 芯片收到 RD 命令时,它首先将打开行的请求部分加载到全局行缓冲器中。

数据进入全局行缓冲器后,DRAM 芯片通过数据总线将数据发送给内存控制器。RD 命令受时序参数 tCL 约束,在此时间之后数据会出现在数据总线上。

写入命令-WR

WR 命令(Fig3中未显示)修改打开的 DRAM 行中的数据。WR 的操作类似于 ACT,因为这两个命令都需要等待足够的时间,让感测放大器恢复 DRAM 单元中的数据。类似于感测放大器在 ACT 的第二步(即电荷恢复)期间恢复单元电容的方式,对于 WR,感测放大器则用 WR 命令提供的新数据值来恢复电容器。WR 的恢复延迟受 tWR 时序参数约束。对于 ACT 和 WR 命令,恢复延迟都源于感测放大器驱动位线以补充 DRAM 单元电容的电荷。

预充电命令-PRE

PRE 用于关闭一个打开的 DRAM 行,并为 DRAM 存储体激活另一行做准备。内存控制器可以在至少经过 tRAS 时序参数规定的时间间隔后,向同一存储体发出跟随在 ACT 之后的 PRE 命令。

tRAS 确保有足够的时间将激活行的 DRAM 单元完全恢复到可预充电的电压水平(Fig3中的4)。

PRE 的延迟受 tRP 时序参数约束,该参数允许足够的时间将位线电压设置回参考电压水平(例如,Vdd/2)。在tRP之后(Fi3中的5),内存控制器可以向同一存储体发出 ACT 命令以打开新的一行。

刷新命令-REF

DRAM 单元无法永久存储其数据,因为单元电容会随时间泄漏电荷。

DRAM 单元的保持时间定义为数据存入单元后仍能被正确读出的时间长度。

为了确保数据完整性,必须定期刷新 DRAM 单元。为了实现所有 DRAM 单元的定期刷新,内存控制器周期性地发出刷新(REF)命令,以确保每个 DRAM 单元在一个固定的刷新窗口期内(通常在实现 DDR4 标准的芯片中为 32 ms 或 64 ms)被刷新一次。DRAM 芯片在收到单个 REF 命令时刷新若干行(例如 16 行),完成此操作需要 tRFC 时间。

-

控制器

+关注

关注

114文章

17860浏览量

195016 -

DRAM

+关注

关注

41文章

2401浏览量

189539 -

cpu

+关注

关注

68文章

11320浏览量

225832

原文标题:DRAM 历史、挑战及机遇——结构&读取原理

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

不同DRAM Devices 的组织方式及其效果

DRAM的工作原理 DRAM存储数据和读取数据过程说明

基于SRAM和DRAM结构的大容量FIFO的设计与实现

Windows API 程序的组织结构

DRAM 原理 2 :DRAM Memory Organization

DRAM原理 5 :DRAM Devices Organization

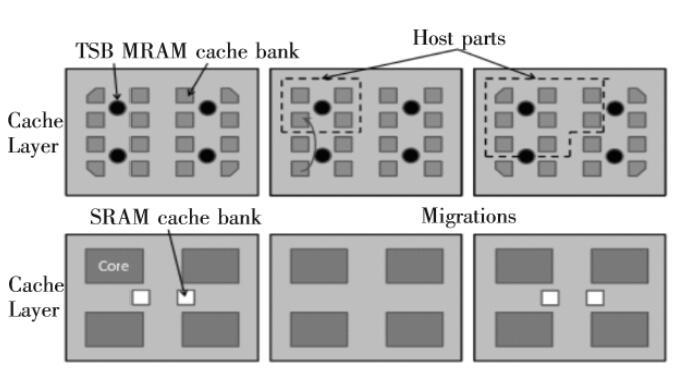

读取优先和SRAM-MRAM混合结构,几个混合结构的管理策略

一文知道DRAM的组织方式

堆叠式DRAM存储节点相关部分的结构分析

DRAM组织结构和读取原理介绍

DRAM组织结构和读取原理介绍

评论