在设计高速高密度PCB时,串扰(crosstalk interference)确实是要特别注意的,因为它对时序(timing)与信号完整性(signal integrity)有很大的影响。以下提供几个注意的地方:

控制走线特性阻抗的连续与匹配。

走线间距的大小,一般常看到的间距为两倍线宽。可以透过仿真来知道走线间距对时序及信号完整性的影响,找出可容忍的最小间距。不同芯片信号的结果可能不同。

选择适当的端接方式。

避免上下相邻两层的走线方向相同,甚至有走线正好上下重叠在一起,因为这种串扰比同层相邻走线的情形还大。

利用盲埋孔(blind/buried via)来增加走线面积,但是PCB板的制作成本会增加。在实际执行时确实很难达到完全平行与等长,不过还是要尽量做到。

除此以外,可以预留差分端接和共模端接,以缓和对时序与信号完整性的影响。

考虑电路板尺寸和电流

大多数从事电子设计的人都知道,就像沿着河道走的河流,流动的电子也可能会遇到咽喉点和瓶颈;这一点被直接应用在车用保险丝(automotive fuse)的设计中。透过控制走线的厚度和形状(U型弯曲、V型弯曲、S形等),保险丝可以经过校准,在电流超载时熔断于咽喉点。

问题是,设计工程师偶尔会在他们的PCB设计中遭遇类似的电气咽喉点;举例来说:在用两个陡峭45度也可以的地方,使用90度弯角;当弯曲度大于90度时,采用之字形状。充 其量那些导线只会让讯号传播速度变慢;最糟糕的情况是它们会像汽车保险丝一样在电阻点熔断。

避开裂片风险

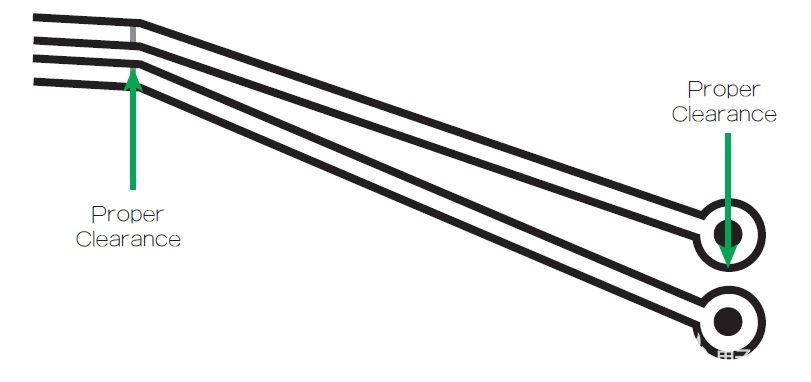

裂片(sliver)是一种制造上的失误,可透过适当的电路板设计获得最佳管理(如图1);为了理解裂片问题,我们需要复习一下化学蚀刻工艺。化学蚀刻是为了分解不需要的铜,但如果要蚀刻的部分特别长、薄、呈片状,那些形状有时候会在完全被分解之前整块剥离;这种裂片会飘浮在化学溶液中,有可能随机落在另一片电路板上。

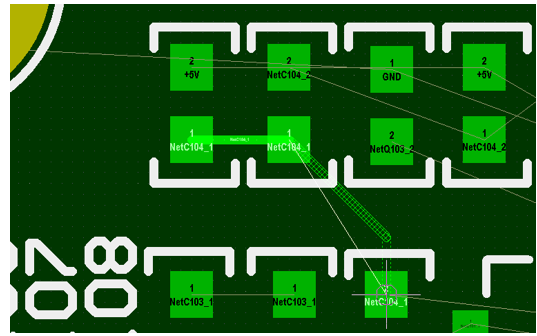

图1 在这个案例中,走线之间的窄屏蔽对电路基板来说是安全的。

同样有可能发生的风险是,裂片仍留在原来那片电路板上;如果裂片够窄,酸液池可能会腐蚀掉下方足够多的铜,使裂片部分剥离。于是裂片像旗子一样黏着电路板四处飘,最后还是免不了落到那片板子上导致其他走线短路。

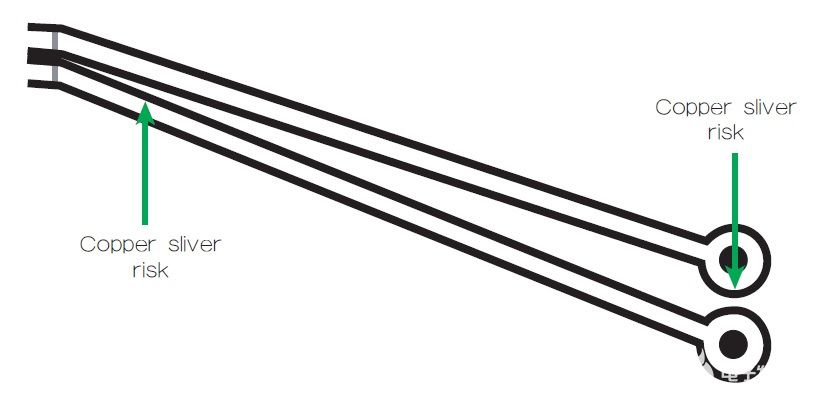

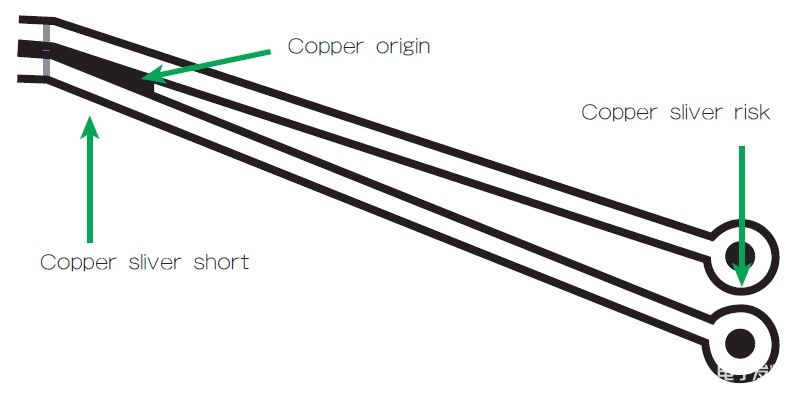

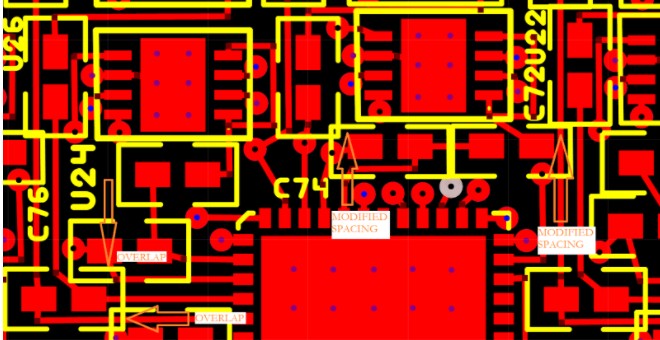

那么该去哪里寻找潜在的裂片?又如何避免裂片产生呢?在进行PCB布线时,最好避免留下非常窄的铜线区域(如图2);这种区域通常是走线与焊垫间隙出现交叉、平面被填满的情况造成(图3)。将铜线的最小宽度设置为大于制造商允许的最小值,你的设计应该就不会有这方面的问题。标准的最小蚀刻宽度是0.006英吋。

图2 一个非常狭窄的裂片风险区域,例如图中这个原始设计档内的案例,在制造时可能不受控制地剥离,导致短路和良率问题。

图3 在这个案例中,化学蚀刻会改变狭窄裂片填充的形状/尺寸;裂片剥离时会产生意料不到的碎屑或漂浮物。

关注DRC

自动布线器的设置通常是针对设计功能,而设计规则检查器(Design Rule Checker,DRC)一般是用来撷取制造商的设计约束;虽然设置过程同样繁琐,跟自动布线器比起来要好得多。大多数设计团队最终都会建立一整套设计规则,目的是标准化裸板制作成本、最大化良率,并让组装、检查和测试尽可能一致。

审核编辑:汤梓红

-

pcb

+关注

关注

4415文章

23955浏览量

426007 -

电路板

+关注

关注

140文章

5344浏览量

108949 -

串扰

+关注

关注

4文章

196浏览量

27872

发布评论请先 登录

PCB布线常见面试题,你都会吗?(4)

在高速(>100MHz)高密度PCB设计中的技巧?

PCB布局及原理图交互式抓取

高速高密度PCB设计的关键技术问题是什么?

高速高密度PCB设计中电容器的选择

Altium Designer入门教程之印刷电路板的布线设计详细资料说明

PCB设计中管理高密度通孔的需求设计

浅谈高密度PCB设计中的元件放置

高速(>100MHz)高密度PCB设计技巧分享

BELLING(贝岭)BL9110-330BPFB:高效稳定的电源稳压解决方案

奥士康荣获两项国际专利授权

立隆VES100M系列高可靠性小型化10μF贴片铝电解电容器选型资料

高密度PCB设计中的技巧

高密度PCB设计中的技巧

评论