中国北京,2022年4月21日——全球公认的卓越的模拟/混合信号晶圆代工厂X-FAB Silicon Foundries(“X-FAB”)今日宣布,扩展其SubstrateXtractor工具应用范围,让用户可以借助这一工具检查不想要的衬底耦合效应。作为全球首家为BCD-on-SOI工艺提供此类分析功能的代工厂,X-FAB将这一最初面向XH018和XP018 180nmBulk CMOS工艺开发的工具,新增了其对XT018 180nm BCD-on-SOI工艺的支持,作为BulkCMOS工艺外的一项补充。通过使用新的SubstrateXtractor升级版本,可以加速SOI相关的产品开发,避免多次迭代。

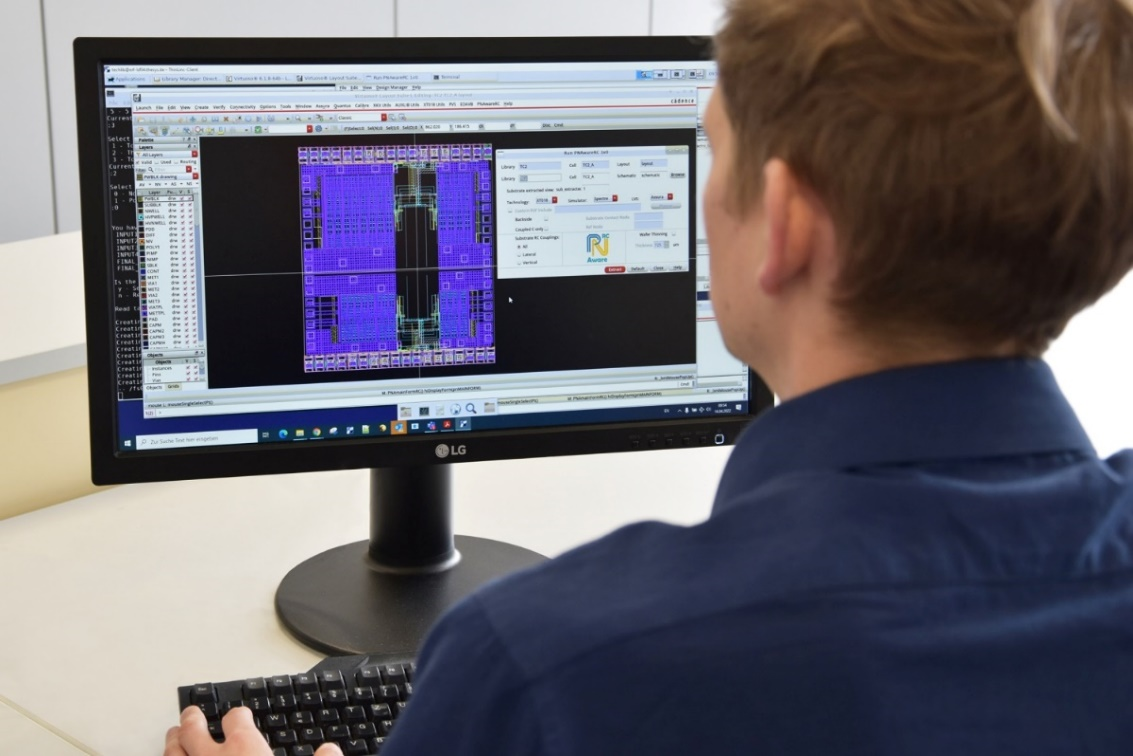

图为X-FAB工程师正在使用衬底耦合分析工具

最初的SubstrateXtractor由X-FAB与EDA合作伙伴PN Solutions(基于其广泛使用的PNAware产品)合作开发,于2019年发布。利用这一工具,客户能够解决半导体衬底内有源和无源元件间相互作用所造成的耦合问题(无论这些元件作为电路本身的一部分,还是以寄生方式存在)---其所带来的显著优势使客户的项目能够更迅速地进入市场。PN Solutions的PNAwareRC工具支持SOI工艺,由此进一步增强了平台的功能并扩大了其吸引力。

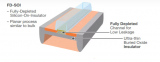

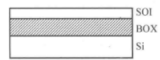

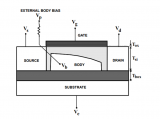

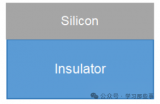

X-FAB的XT018工艺BOX/DTI功能可以将芯片上的组成功能模块相互隔离,适用于需要与数字模块去耦合的敏感模拟模块,或必须与高压驱动电路隔离的低噪声放大器。此工艺也使得多通道的设计实现更加容易,因为XT018中的电路被有效地放置在其自身独立的衬底中,从而减少了串扰。

在基于SOI的集成电路中,利用SubstrateXtractor实现衬底耦合分析的能力对于客户来说极具价值。虽然SOI工艺中的有源部分可以通过BOX和DTI完全介电隔离,有源部分被隔离之后就如同各自孤立一般,但无源R和C耦合仍然可能存在。得益于这一升级版新工具,可以为DTI和BOX产生的横向和纵向耦合路径提取无源RC网络,并经由对无源耦合网络的仿真,评估它们对集成电路的影响。此类新增的版图后抽取寄生的关键应用,包括工业及汽车系统中使用的大电流和高电压器件等。

“消除衬底耦合是一项具有挑战性的任务。通过支持对我们XT018 BCD-on-SOI工艺相关的寄生元素的提取,客户将能够模拟电路模块的耦合,并识别对性能不利的干扰因素。”X-FAB设计支持总监Lars Bergmann表示,“在涉及非常大的干扰电压或在个位数GHz范围内的高频情况下,这一功能扩展将极具意义。”

缩略语:

BOX 埋入式氧化物

BCD Bipolar CMOS DMOS

DTI 深槽隔离

EDA 电子设计自动化

RC 电阻-电容

SOI 绝缘体上硅

-

芯片

+关注

关注

462文章

53534浏览量

458979 -

X-FAB

+关注

关注

1文章

17浏览量

9450 -

FD-SOI工艺

+关注

关注

0文章

2浏览量

1295

发布评论请先 登录

SOI工艺技术介绍

芯原亮相第十届上海FD-SOI论坛

一文详解SOI异质结衬底

一文详解BSIM-SOI模型

IQM 宣布 Resonance 量子云平台重大升级,推出全新软件开发工具包

电动汽车时代,BCD工艺成为关键

碳化硅衬底厚度测量探头温漂与材料各向异性的耦合影响研究

创飞芯90nm BCD工艺OTP IP模块规模量产

氮化镓衬底的环吸方案相比其他吸附方案,对于测量氮化镓衬底 BOW/WARP 的影响

Design House与Fab的关系

半导体FAB中常见的五种CVD工艺

碳化硅衬底修边处理后,碳化硅衬底TTV变化管控

一文看懂SOI的重要性

X-FAB宣布升级其衬底耦合分析工具,将BCD-on-SOI工艺纳入其中

X-FAB宣布升级其衬底耦合分析工具,将BCD-on-SOI工艺纳入其中

评论