文章来源:SPICE模型

原文作者:若明

本文介绍了SOI工艺中器件模型提取技术。

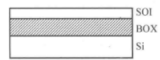

随着半导体工艺进入纳米尺度,传统体硅(Bulk CMOS)技术面临寄生电容大、闩锁效应等瓶颈。SOI技术凭借埋氧层(BOX)的物理隔离优势,成为航空航天、5G通信等领域的核心技术。本篇介绍一下业界SOI工艺模型BSIM-SOI模型。

SOI工艺特点

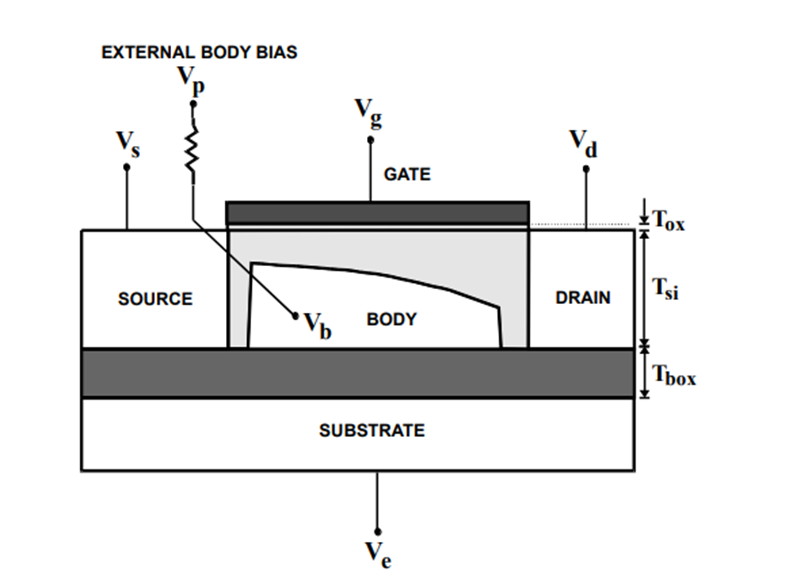

与Bulk MOSFET器件相比,在SOI MOSFET的沟道下方有一层厚度为Tbox的埋藏氧化物。

1. SOI器件结构对比(PD-SOI, FD-SOI)

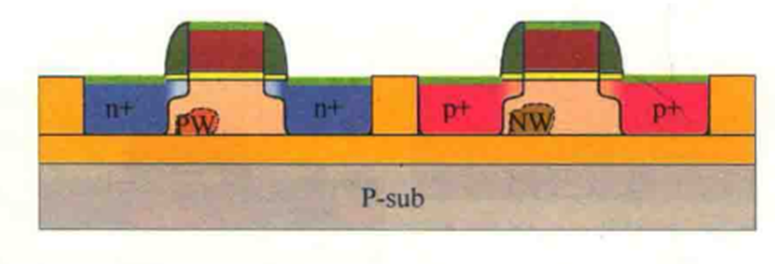

如下图所示,当顶层硅薄膜厚度大于等于1000Å,当器件工作在饱和区时,它的耗尽层小于顶层硅薄膜厚度,所以它是部分耗尽(PD-SOI)。PD-SOI MOS 器件体区接地,则其设计和工作原理与体硅接近,大部分体硅器件模型参数可通用。PD-SOI MOS 器件体区不接地,那么过量空穴积累在体区,出现浮体效应对器件性能产生不良的影响。

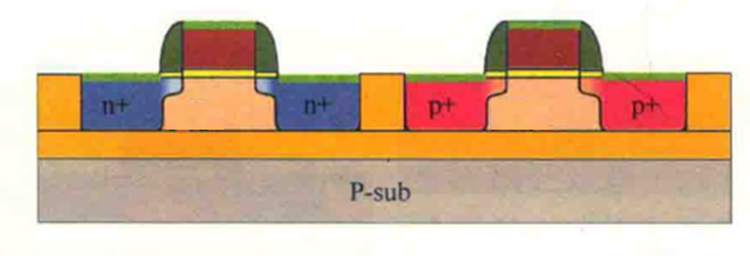

如下图所示,当顶层硅薄膜的厚度小于等于500 Å,当器件工作在饱和区时,它的耗尽层大于顶层硅薄膜厚度,所以它是全耗尽(FD-SOI)。FD-SOI MOS 器件降低了沟道区电场,从而降低了热载流子效应和短沟道效应,晶体管的驱动能力增强,常被应用在纳米级工艺。

2. SOI技术优势

寄生电容小:SOI 器件中结与衬底的寄生电容是隐埋绝缘体电容,寄生电容小。

无闩锁效应:SOI 器件中由于没有到衬底的导电通路,闩锁效应的纵向通路被切断。

低功耗:SOI 器件中泄漏电流很小,因此静态功耗很小;由于小的寄生电容,因此动态功耗也大大减小。

集成密度高:SOI 电路采用全介质隔离,器件最小间隔仅仅取决于光刻和刻蚀技术的限制,集成密度明显提高。

适于小尺寸器件:SOI 器件的短沟道效应较小,更适合小尺寸器件。

3. PD-SOI遇到的挑战与应对方案

1) 挑战

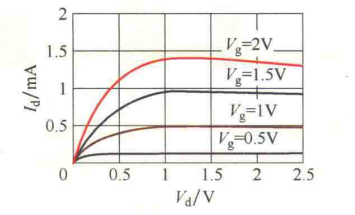

a.翘曲效应

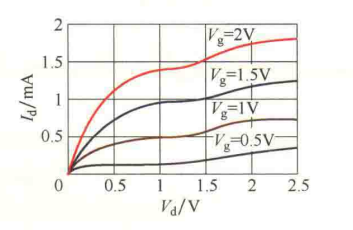

当漏电压高于某值时,PD-SOI器件的输出特性曲线出现上翘现象。体浮空区的电位升高致体浮空区的势垒高度减低,随着漏电压得增加,漏电流不再饱和,而是迅速增加,出现翘曲现象。通过体接触可以抑制翘曲效应。

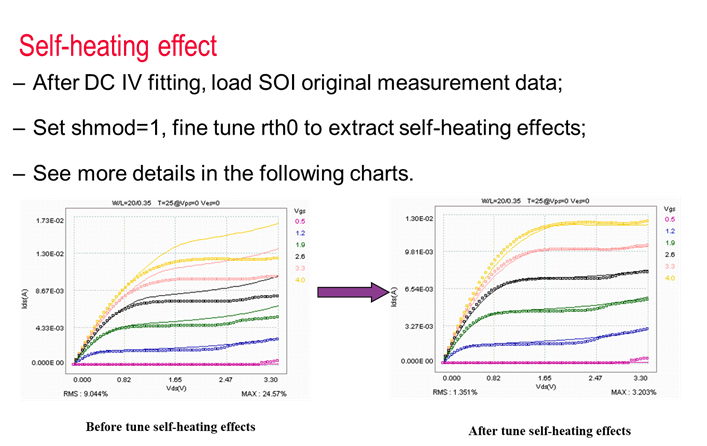

b.自热效应

由于BOX不但提供了电学隔离,同时也造成了热隔离。随着SOI器件硅薄膜的温度急剧升高,晶格散射加强,导致电子载流子迁移率下降,输出特性曲线表现为在漏电压较大时,出现漏电流随着电压增大而降低的负电导效应。

2) 应对方案

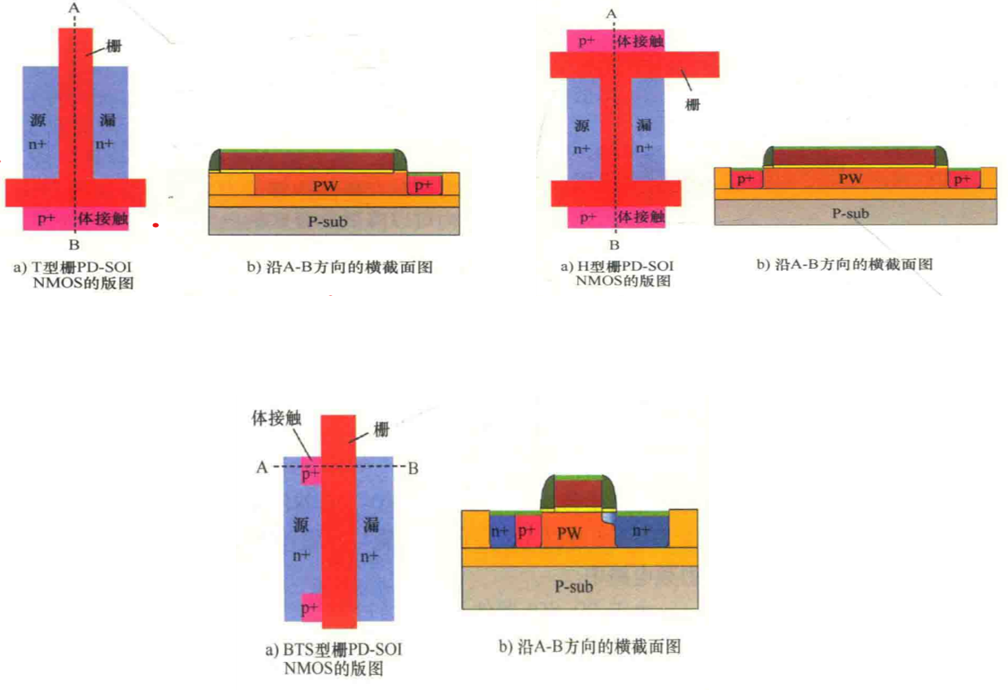

由于PD-SOI器件中存在阱体区,会产生翘曲效应、寄生双极晶体管效应、栅感应漏极漏电流和自加热效应等浮体效应。为了抑制浮体效应,通常把体接到一个固定的电位上,从而控制体电势的变化,这种方法称为体接触。常用的体接触有三种类型:T 型栅、H 型栅和BTS (Body-Tied-to-Source,源极和体区相连)型栅。

“图片部分来自温得通著作的《集成电路制造工艺与工程应用》,书中图文并茂,非常详细的介绍了各自主流工艺,非常适合想要了解工艺的同仁。”

BSIM-SOI模型介绍

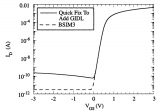

BSIM-SOI (Silicon-on-Insulator)是用于SOI (Silicon-on-Insulator)电路设计的SPICE紧凑型模型,可用于模拟部分耗尽(PD)和完全耗尽(FD)器件。BSIM-SOI共享BSIM3和BSIM4的许多特性和基本方程,于2001年12月被Si2 Compact Model Coalition (CMC)选定为标准SOI MOSFET型号。

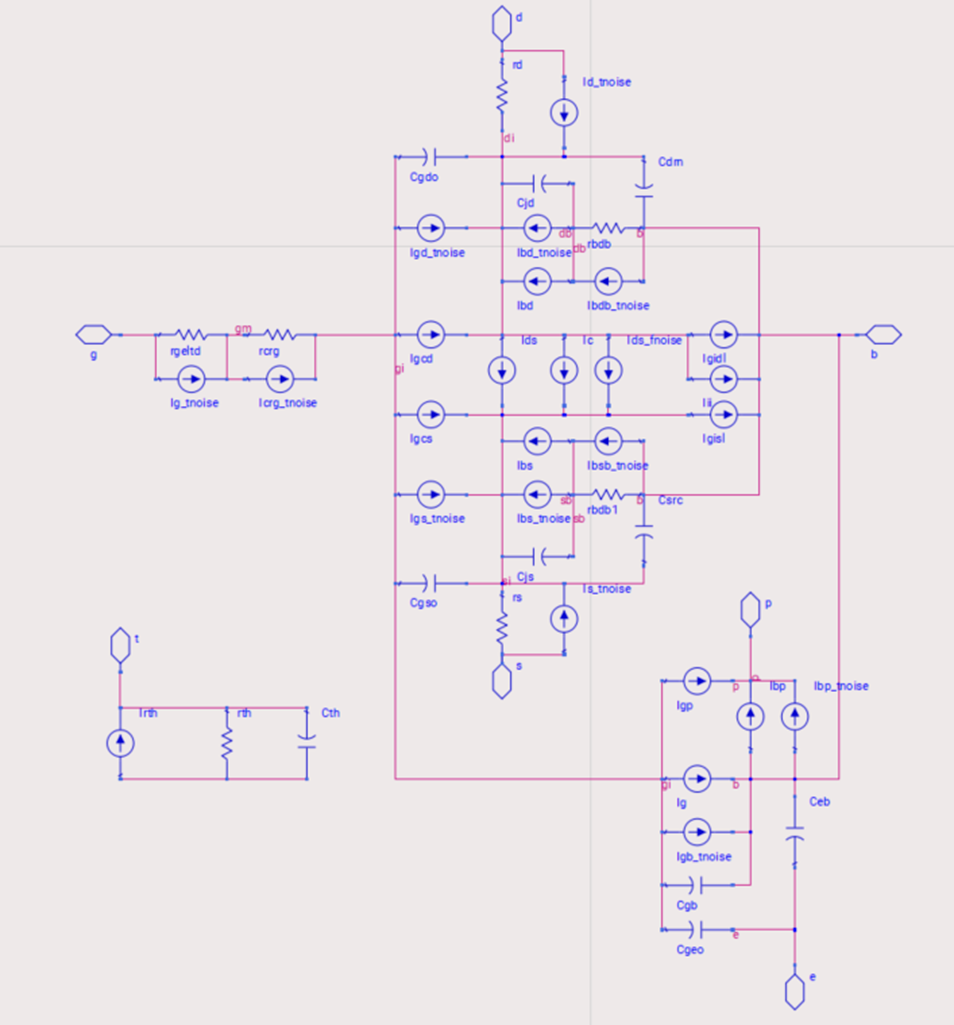

1. 等效电路

在浮体结构电路仿真中有四个外部电极:栅极(Vg),漏极(Vd),源极(Vs)、衬底电极(Ve)和体电位(Vb)。如果有体接触时,还有一个外部的体接触电极(Vp)。

2. 核心公式

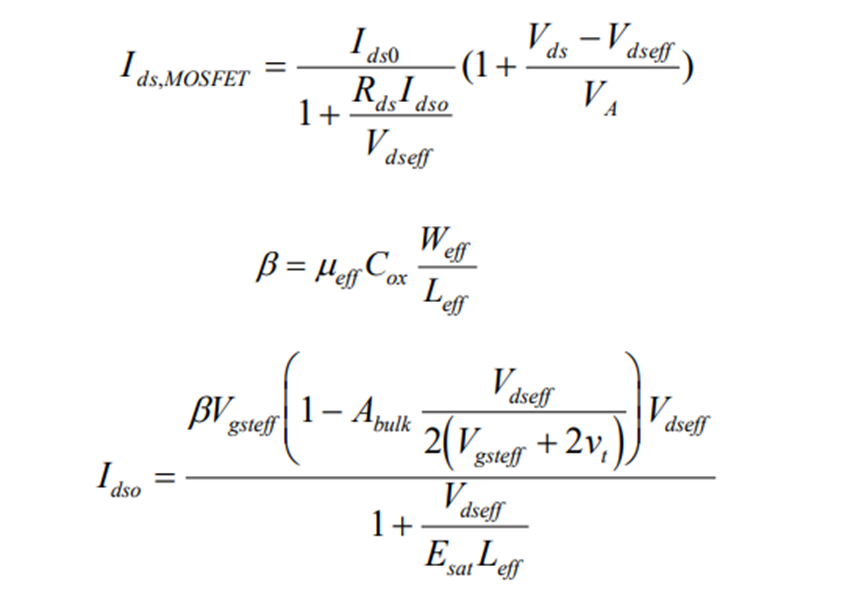

1) MOSFET I-V模型(改进自BSIM3/BSIM4)

基本公式继承自BSIM3/BSIM4,但是对Vth和Abulk做了修正。

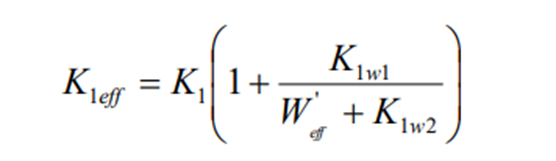

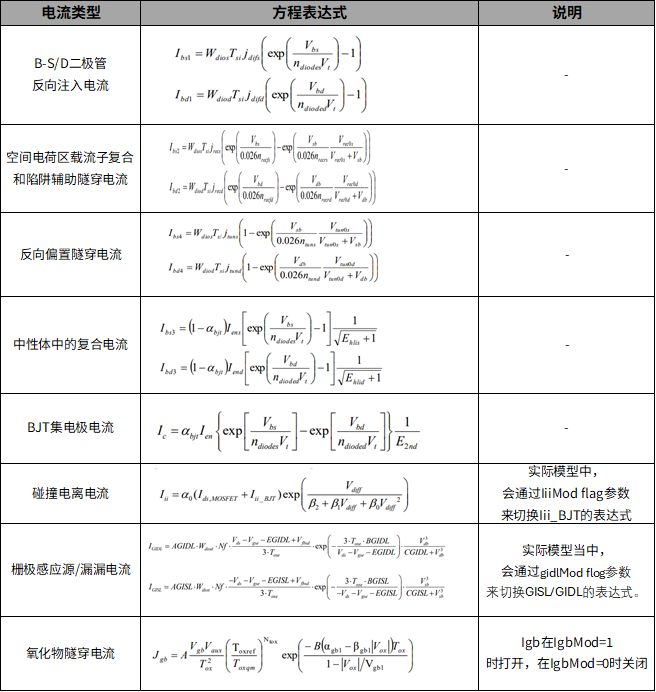

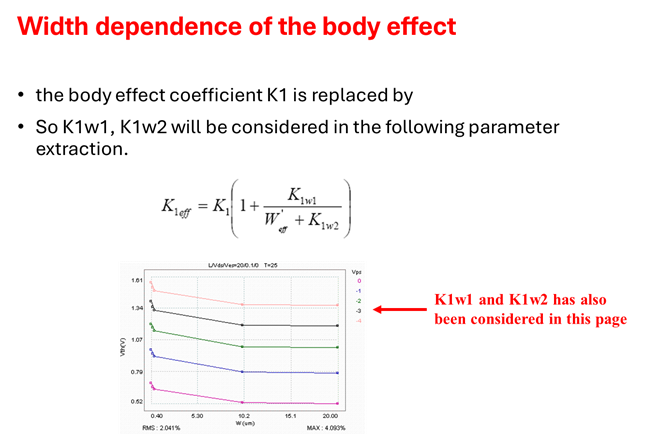

BSIM3/BSIM4阈值电压K1被K1eff修正:

Abulk被修正:

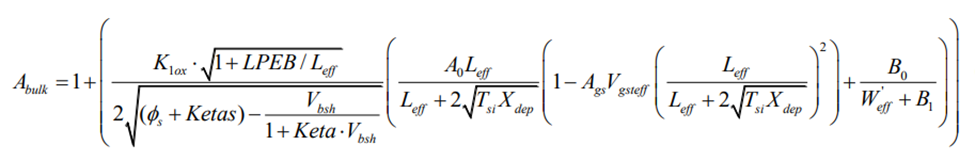

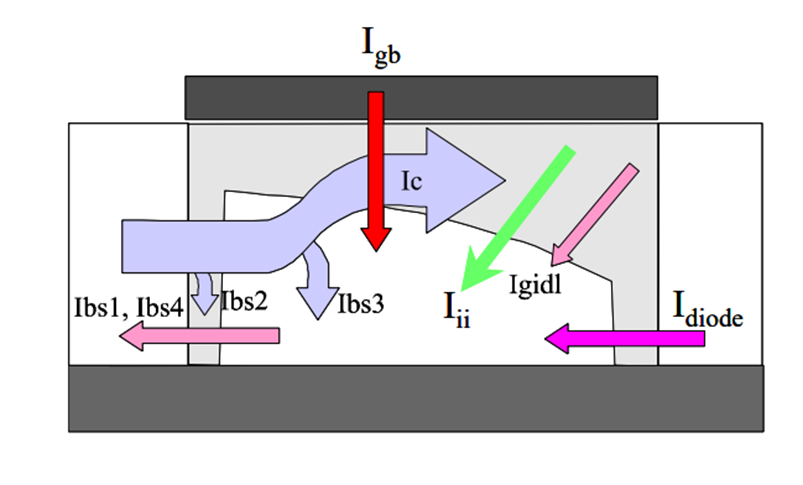

2) Body电流模型

我将这些Body电流公式整理为如下表格所示的8个分量。

3) 自热模型

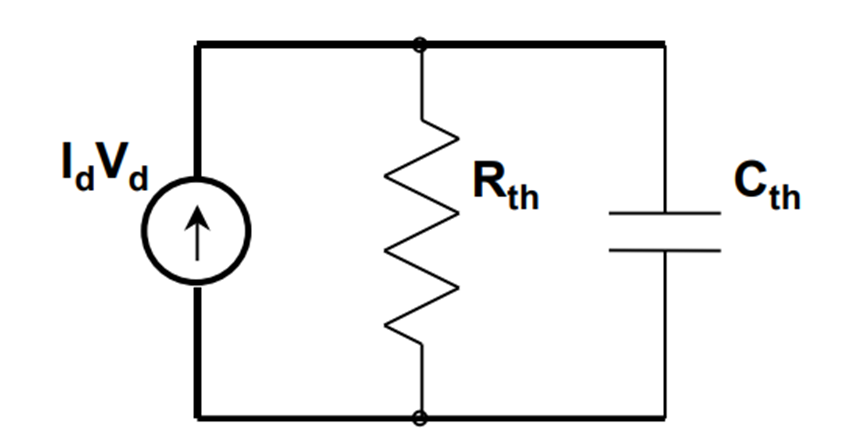

通过辅助的RC电路来对其进行建模。如果shMod=1,且Rth非零,则SPICE模拟中将创建热节点(T)。

BSIM-SOI模型参数提取

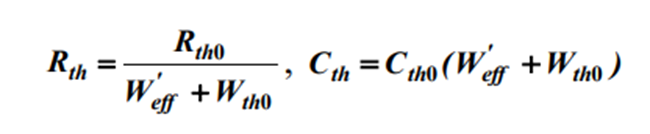

1. 测试数据

2. 检查数据及数据转换

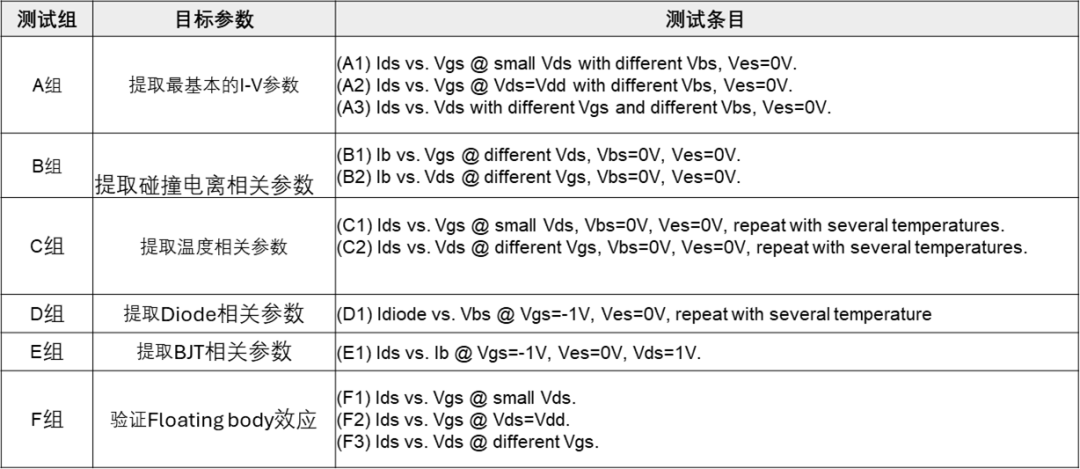

定义一些关键的targets,来辅助检查数据和W, L, T的趋势是否合理。因为原始建模数据中的温度依赖性与电压依赖性交织在一起,Self-heating效应需要大量的迭代计算,可能会损害模型质量。所以需要将Self-heating效应先从数据中移除,先来提取没有Self-heating效应的模型参数。数据处理可借助MBP软件来完成。

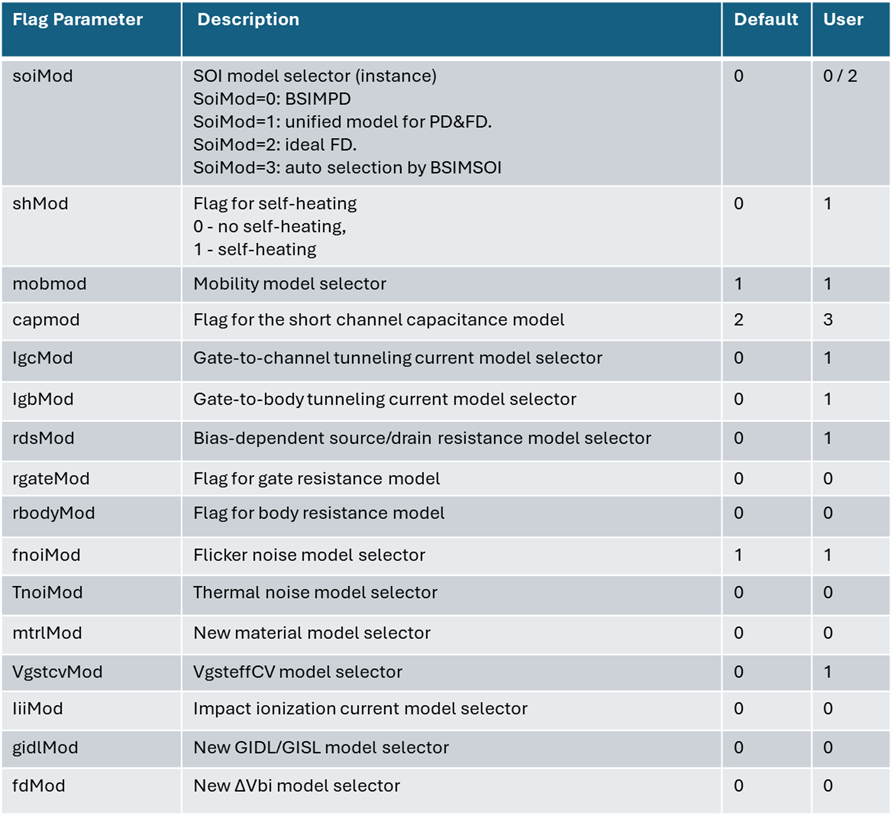

3. Flag 参数设置

根据器件特性数据分析并选择适当的模型Flag 参数。比如,打开或者关闭栅到沟道的隧穿电流等。

4. Process参数设置

关键的process 参数包括: Tox, Tbox, Tsi, Xj, Rsh, Nch, XL, XW. 应该从工艺获得。

5. 参数提取

SOI IV/CV模型参数很多是继承自BSIM3/BSIM4,所以他们的提取类似,这里不再过多介绍。需要注意的是在SOI情况下,由于S/D正好在绝缘子的顶部,不需要提取面积二极管参数。

6. SOI 特殊效应参数提取

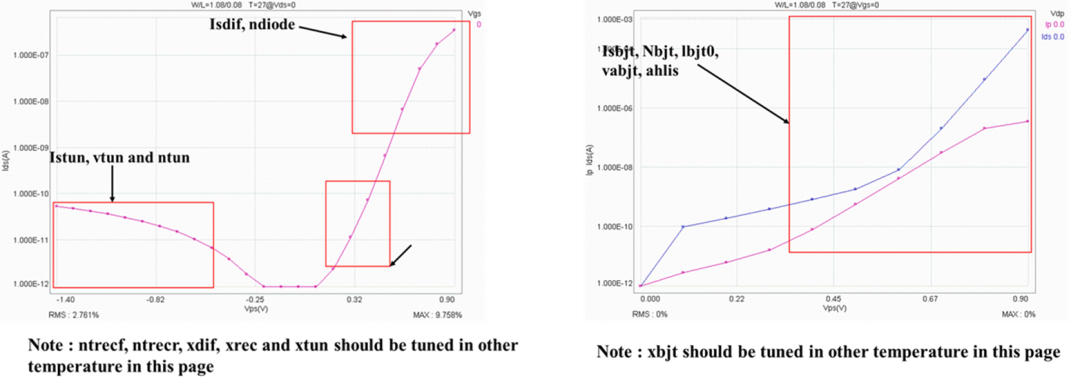

1) 寄生的Diode/bjt电流效应

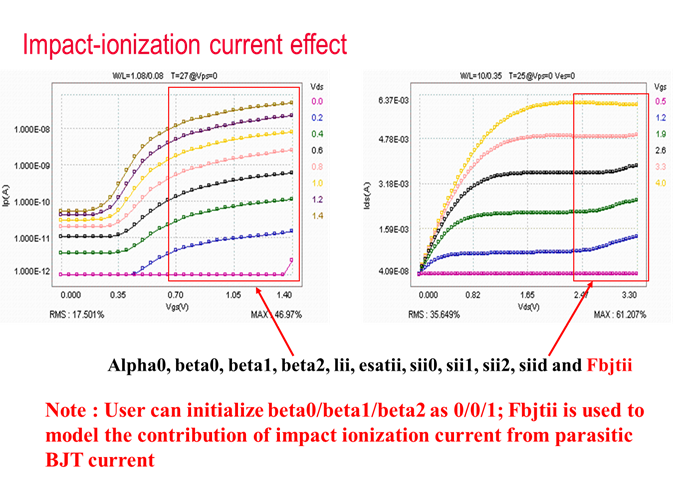

2) 碰撞电离电流效应

3) 体效应

4) 自热效应

-

工艺

+关注

关注

4文章

708浏览量

30111 -

SPICE

+关注

关注

6文章

198浏览量

44303 -

模型

+关注

关注

1文章

3648浏览量

51710

原文标题:SPICE模型系列之BSIM-SOI

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

一文详解SOI异质结衬底

一文详解BSIM-SOI模型

一文详解BSIM-SOI模型

评论