MOSFET的失效机理

本文的关键要点

・SOA是“Safety Operation Area”的缩写,意为“安全工作区”。

・需要在SOA范围内使用MOSFET等产品。

・有五个SOA的制约要素,不满足其中任何一个要素的要求都有可能会造成失效。

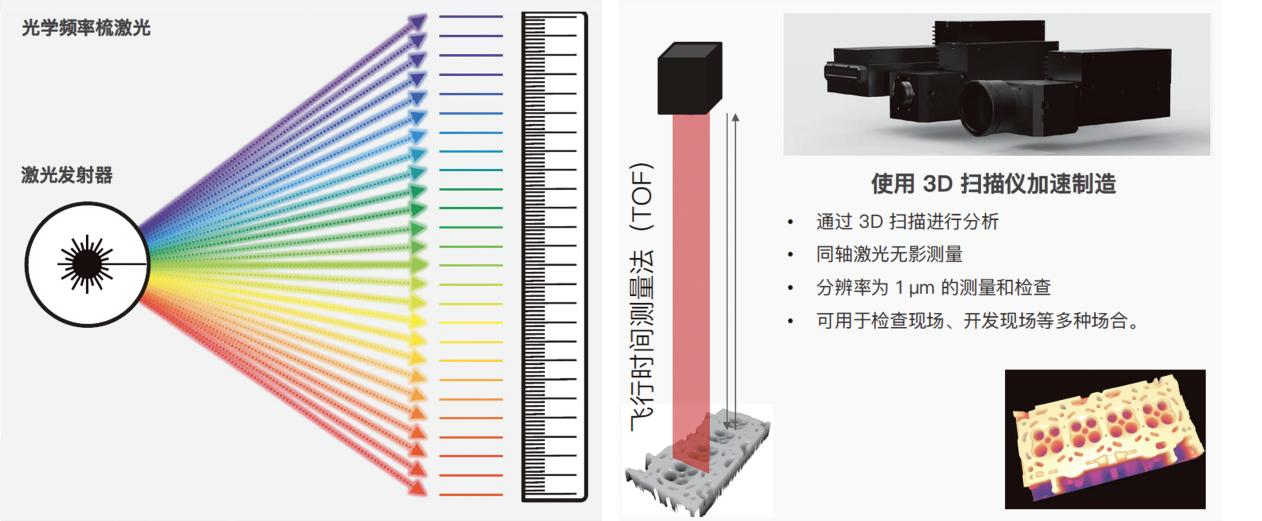

什么是SOA(Safety Operation Area)?

SOA是“Safety Operation Area”的缩写,意为“安全工作区”。要想安全使用MOSFET,就需要在SOA范围内使用MOSFET,超过这个范围就有可能造成损坏。在SOA范围之外工作时造成的损坏称为“SOA失效”。例如,SJ MOSFET(Super Junction MOSFET)R6024KNX的SOA如下所示:

SJ MOSFET R6024KNX的SOA

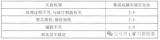

SOA由纵轴上的漏极电流ID和横轴上的漏源电压VDS来表示。也就是说,VDS、ID及它们的乘积(功率损耗PD)、以及二次击穿区决定了MOSFET的安全工作范围。另外,施加功率的脉冲宽度PW也是决定SOA的重要因素。SOA划分为图中所示的(1)~(5)个区域。

SOA的区域划分、限制以及与失效之间的关系

下面介绍一下图中的区域(1)~(5)。

区域(1):漏极电流ID受MOSFET的导通电阻RDS(ON)限制的区域

是指即使施加的VDS小于绝对最大额定值,ID也会受到RDS(ON)限制的区域。根据欧姆定律I=V/R,ID只能流到红线位置。

※图中的区域是VGS=10V时的示例

区域(2):由施加脉冲时漏极电流的绝对最大额定值IDP决定的区域

(2)的绿线是规格书中规定的IDP的绝对最大额定值。当然,绝对最大额定值是绝对不能超过的,因此当IDP超过该值时是无法使用的。如果在超过该值的范围(电流值)使用,由于超出了保证的工作范围,因此可能会造成损坏。

区域(3):热限制区域

这是由MOSFET的容许损耗PD决定的区域。受施加功率的脉冲宽度PW和瞬态热阻的限制。只要在该范围内,Tj通常不会超过绝对最大额定值TjMAX,因此可以安全使用。但是请注意,该线会因环境温度、MOSFET的实际安装条件和散热条件等因素而异。此外,作为开关使用MOSFET时,可能会瞬间被施加高电压和大电流,因此即使在开关的瞬态状态下也必须注意不要超过区域(3)的限制。

区域(4):二次击穿区域

当在施加高电压的状态下流过电流时,元器件内部的局部可能会流过大电流并造成损坏,这称为“二次击穿”。这条线是用来防止造成二次击穿状态的限制线。与区域(3)的热限制区域一样,二次击穿区域也受环境温度等因素的影响。

区域(5):由MOSFET漏源电压的绝对最大额定值VDSS决定的区域

这是规格书中规定的受VDSS限制的区域,如果超过这个区域,就可能发生击穿并造成损坏。需要注意的是,由反激电压和寄生电感引起的电压变化,可能会瞬间超过该限制。

审核编辑:何安

-

SOA

+关注

关注

1文章

319浏览量

29030

原文标题:R课堂 | 什么是SOA(Safety Operation Area)失效

文章出处:【微信号:罗姆半导体集团,微信公众号:罗姆半导体集团】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

电子元器件典型失效模式与机理全解析

IGBT 芯片表面平整度差与 IGBT 的短路失效机理相关性

LED失效的典型机理分析

MOSFET失效原因及对策

电子元器件失效分析与典型案例(全彩版)

IGBT的导热机理详解

如何有效地开展EBSD失效分析

芯片失效机理之闩锁效应

MOSFET的失效机理

MOSFET的失效机理

评论