1.扇出太多引起的时序问题。

信号驱动非常大,扇出很大,需要增加驱动能力,如果单纯考虑驱动能力可以尝试增加buffer来解决驱动能力,但在插入buffer的同时增加了route的延时,容易出现时序报告评分问题。

解决该问题常用方法为进行驱动信号逻辑复制,即对扇出很大的信号产生逻辑进行多次复制,生成多路同频同相的信号去驱动下级逻辑电路。保证了时延同时也增大了驱动能力。但是该方法在使用过程中可以和buffer一起使用,平衡资源利用率和时延,防止资源分配不均或者时序考虑不周。

解决该问题常用方法为进行驱动信号逻辑复制,即对扇出很大的信号产生逻辑进行多次复制,生成多路同频同相的信号去驱动下级逻辑电路。保证了时延同时也增大了驱动能力。但是该方法在使用过程中可以和buffer一起使用,平衡资源利用率和时延,防止资源分配不均或者时序考虑不周。

2.对于时钟频率要求较高导致的上升沿下降沿对不同的寄存器操作的问题。

首先分析该问题产生原因,如果上升沿下降沿都使用,就相当于是电平触发,电平触发比时钟沿触发更容易受到干扰,所以一般不同时对一个时钟的上升沿和下降沿分别对不同的寄存器操作。

1)将时钟通过MMC或者PLL产生180相移产生新的时钟,新的始终的上升沿就是原时钟的下降沿,从而实现都为上升沿触发。

2)使用全局时钟资源中的INV实现对原时钟信号取反,然后新的时钟信号的上升沿就是原时钟的下降沿。

另外对于其他方法要思考,比如对原时钟信号进行倍频实现上升沿下降沿均为上升沿,这个方法直接提升系统时钟速率一倍,如果不是时钟速度太高这个上升沿下降沿问题也不会出现了,故,该方法暂不考虑。还有就是对于时钟的使用一定要使用PLL或者MMC这些专门的时钟内核生成。

另外对于其他方法要思考,比如对原时钟信号进行倍频实现上升沿下降沿均为上升沿,这个方法直接提升系统时钟速率一倍,如果不是时钟速度太高这个上升沿下降沿问题也不会出现了,故,该方法暂不考虑。还有就是对于时钟的使用一定要使用PLL或者MMC这些专门的时钟内核生成。

3.布局太差导致的布线延迟太高问题

布线延迟太高问题一般有两种情况:

1)一种是布线扇出太多导致的问题,另外再对扇出太多补充一点,扇出太多而增加buffer提高驱动能力,而普通I/O信号或片内信号进入BUFG到从BUFG输出,有大约10ns的固定时延,但是BUFG到片内所有单元的延时可以忽略为0ns。这个问题在上篇中已经给出了解决方案,也就是通过逻辑复制的方法解决。

2)就是今天要说的问题,就是本身各种信号扇出并不多,逻辑时间也不是很大,但是布线延迟很大,这种问题就是布局太差的问题。

相应的解决方案有:通过ISE布局工具中调整布局的努力程度(effort level),特别努力程度(extra effort),MPPR选项,实在不行的话就尝试使用Flootplanner相对区域约束重新对设计进行布局规划。

4.就是出现逻辑级数过多情况

也就是逻辑计算时间比较大,这种情况一般不属于时序问题,而属于程序编写问题,尽量不要嵌套IF ELSE语句或者CASE语句嵌套,能用CASE语句尽量不用IF ELSE语句,还有就是在使用IF 语句和CASE语句时注意防止产生不必要的锁存器。

责任编辑:haq

-

FPGA

+关注

关注

1664文章

22504浏览量

639333 -

驱动

+关注

关注

12文章

1992浏览量

88707 -

时钟

+关注

关注

11文章

1999浏览量

135242

原文标题:FPGA时序问题与解决方法

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

工程师高培解读XilinxVivadoFPGA设计进阶与AI自动编程

扇出型晶圆级封装技术介绍

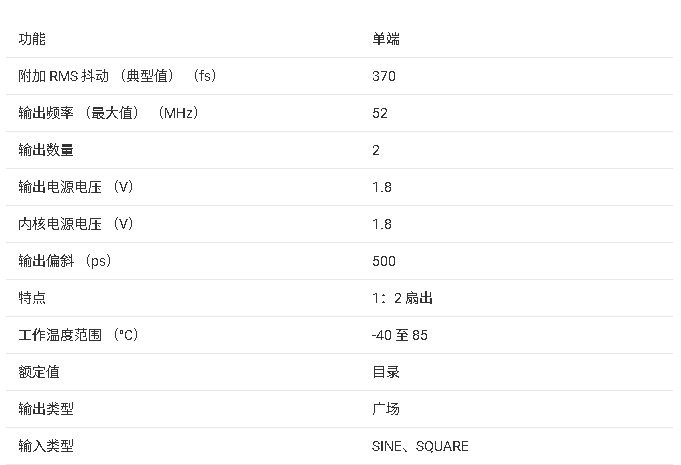

ADCLK944:高速低抖动时钟扇出缓冲器的设计与应用

FPGA时序收敛的痛点与解决之道——从一次高速接口调试谈起

深入解析RC190xx:PCIe Gen5/6高性能扇出缓冲器家族

为什么在FPGA设计中使用MicroBlaze V处理器

数字IC/FPGA设计中的时序优化方法

vivado时序分析相关经验

FPGA测试DDR带宽跑不满的常见原因及分析方法

CDC3RL02 低相位噪声双通道时钟扇出缓冲器总结

高扇出信号线优化技巧(下)

高扇出信号线优化技巧(上)

FPGA扇出太多引起的时序问题

FPGA扇出太多引起的时序问题

评论