(文/程文智)不久前,Microchip发布新闻稿介绍了其新的中等带宽现场可编程门阵列(FPGA)和FPGA系统级芯片(SoC)器件。据其新闻稿介绍,新的FPGA和SoC产品将静态功耗降低了一半,与同类器件相比,具有最小的发热区域,但却并没有损失性能和计算能力。该新产品就是低密度PolarFire FPGA(MPF050T)和PolarFire SoC(MPFS025T)。

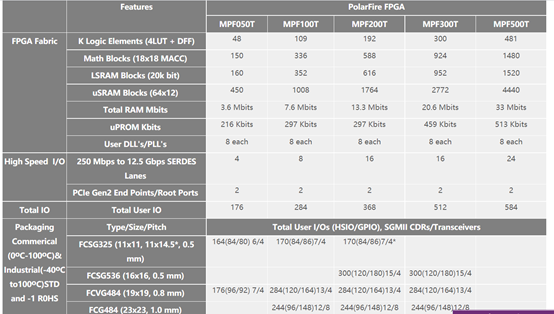

图:PolarFire系列FPGA具体参数(来源:Microchip官网)

具体参数

下面我们来看看这两个新的FPGA产品的具体参数。Microchip的官网有这两款新品的具体参数,比如具有2MB的二级缓存、支持低功耗DDR4(LPDDR4)内存、最高支持12.5Gbps的SerDes,以及支持PCIe接口等等。

此外,新的PolarFire系列FPGA具有更高效的DSP模块;主要用于4K/2K的图像处理,支持MIPI的CSI-2协议;支持图像传感器的接口,比如SLVS-EC;静态功耗做了很大的优化,官方宣称功耗只有竞争对手的十分之一,SerDes功耗也有很大改善;具有比较小的封装尺寸,以及完善的RISC-V生态系统。

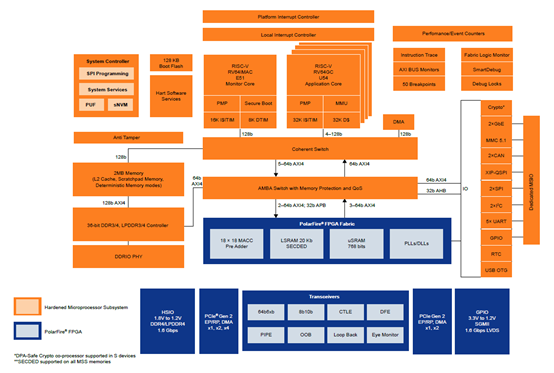

其中PolarFire FPGA SoC还具有硬化的应用级RISC-V架构处理器,且支持五核Linux的处理器子系统,为市场带来了一款创新的免版税、中端嵌入式计算平台。

图:PolarFire FPGA SoC的功能模块框图(来源:Microchip的数据手册)

RISC-V CPU微架构实现是一个简单的五级单发射顺序流水线,不受常用无序机器中存在的Meltdown和Spectre漏洞利用影响。所有的五个CPU内核都与存储器子系统一致,支持在单个多核CPU集群中提供确定性实时系统和Linux的多功能组合。

Microchip的FPGA产品线及特点

其实Microchip的FPGA产品线主要来源于2018年收购的Microsemi。Microsemi的产品囊括高性能耐辐射模拟混合信号集成电路、FPGA、SoC及ASIC、电源管理产品、设置全球时间标准的时序/同步器件及精确时间解决方案、语音处理器件、射频解决方案、分立元件、企业存储和通信解决方案、安全技术和可扩展防篡改产品、以太网解决方案、以太网供电IC及中间跨接方案,以及其他定制设计能力及服务。其中FPGA是其最为重要的产品线。

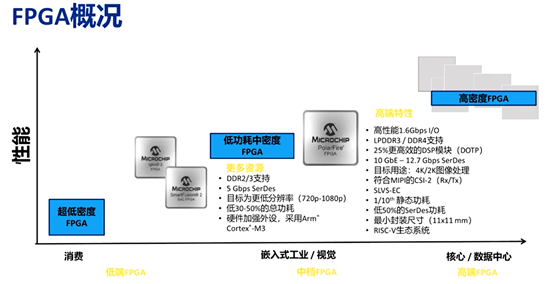

如今Microchip的FPGA产品线主要有三个,即超低密度的FPGA、低功耗中密度FPGA、及高密度FPGA。

图:目前Microchip的产品线概况(来源:Microchip)

据悉,Microchip的FPGA产品主要有四大特色,一是功耗低,官方介绍说,比竞争对手低50%左右;二是久经验证的安全性,因为其产品内置了很多安全和加密的引擎;三是SEU免疫的FPGA配置,SEU指的是单粒子翻转(Single-Event Upsets,SEU),具体来说就是元器件受辐射影响后,引起电位状态的跳变,“0”变成“1”,或者“1”变成“0”,但一般不会造成器件的物理性损伤;四是瞬时及非易失性,上电就马上能工作,不需要配置过程。

应用场景

一般来说,需要高速信号处理,比如雷达信号、图像信号采集、通信信号等实时性要求比较高,需要并行和流水线处理的场合,会需要用FPGA来实现。因为Microchip具有更低的功耗,因此可以用在低功耗智能嵌入式视觉应用和热量受限的汽车、工业自动化、通信、国防和物联网系统中。

关于供货

据介绍,开发者可以借助Microchip的Libero软件工具进行新产品开发,该工具已经支持最新的PolarFire FPGA和FPGA SoC产品,不过新的FPGA产品的批量出货时间到等到2022年第一季度。

-

FPGA

+关注

关注

1664文章

22502浏览量

639065 -

soc

+关注

关注

40文章

4622浏览量

230153 -

嵌入式视觉

+关注

关注

8文章

119浏览量

59994 -

RISC-V

+关注

关注

49文章

2946浏览量

53534

发布评论请先 登录

直击玄铁RISC-V生态大会,看ALINX FPGA+RISC-V解决方案

重磅合作!Quintauris 联手 SiFive,加速 RISC-V 在嵌入式与 AI 领域落地

喜讯|昊芯RISC-V DSP荣获“中国芯”RISC-V生态推广奖

如果将蜂鸟的risc-v移植到其他的fpga中想实现一些外设功能有什么办法?可以不用操作系统直接添加verilog代码吗?

RISC-V 蜂鸟E203中PC指针起始地址设置搭建

瑞芯微RISC-V芯片已量产,性能、功耗平衡更佳

嵌入式系统迎来RISC-V时代:芯片、OS、工具链协同推动应用落地

硬核加速,软硬协同!混合仿真赋能RISC-V芯片敏捷开发

汽车级MCU自主创新按下“加速键”,三大厂商RiSC-V新品集中亮相

2025新思科技RISC-V科技日活动圆满结束

RISC-V 发展态势与红帽系统适配进展

RISC-V赛道的“硬核”突围之路

FPGA新产品:带RISC-V硬核的FPGA系统级芯片来临

FPGA新产品:带RISC-V硬核的FPGA系统级芯片来临

评论