2026年3月24日,由达摩院主办的 RISC-V 行业年度盛会“玄铁RISC-V生态大会”现场人头攒动。在主论坛展区一角,ALINX 最新推出的AXPGL50 开发板吸引了众多参会者的驻足围观。这块搭载玄铁 E901 处理器的 FPGA 开发平台,以精致的核心板+扩展板设计,展示了 RISC-V 架构在嵌入式领域的灵活性与潜力。

RISC-V是什么?为何它能打破X86与Arm的垄断?

如果你是一位关注芯片行业的开发者,近期一定被“RISC-V”和“玄铁C950”这两个词刷屏了。

纵观全球芯片指令集架构,PC 时代的王者是x86,移动时代的霸主是 ARM。它们虽然强大,但都闭源。而RISC-V 开源、精简、模块化,且通用,适用于所有芯片包括 FPGA、ASIC。

过去很长一段时间,业界对 RISC-V 的认知局限于低功耗的嵌入式与物联网领域。但这种情况正在被彻底颠覆。RISC-V 技术已蔓延至传统高性能计算与人工智能领域。大会上,中国工程院院士倪光南表示:“RISC-V 在全球芯片市场的分额已突破 25%,x86 和 Arm 的双寡头格局正在松解。”

正如同 Linux 在操作系统领域的意义——它让芯片设计的门槛大幅降低,创新速度显著提升。

ALINX AXPGL50:玄铁 E901+紫光同创 Logos FPGA

(紫光同创PGL50H+玄铁E902 开发板 AXPGL50)

ALINX 此次展出的 AXPGL50 开发板,正是基于紫光同创 Logos PGL50H FPGA 芯片打造,并搭载了玄铁 E901 处理器。

玄铁 E901追求极致精简,采用的是 RV32E 架构,拥有 2 级流水线设计。在 40nm 制程工艺下,最小配置面积仅 10.7 千门,相较于前代同级核心实现 39% 的面积优化。在能效方面,E901通过深度低功耗优化,单位能效比提升48%,动态功耗减少48%,性能指标达到1.22 DMIPS/MHz和2.88 Coremark/MHz。在极低的功耗预算下,它依然能够提供可靠的控制与计算能力,特别适合对功耗、面积和成本敏感的嵌入式应用。

紫光同创 Logos PGL50H FPGA 芯片,采用 40nm CMOS 工艺和全新 LUT5 结构,集成 RAM、DSP、Serdes、DDR3 等丰富的片上资源和 IO 接口,具备低功耗、低成本特性,为客户提供高性价比的解决方案,是工业控制、图像视频领域应用的理想选择。

AXPGL50采用核心板(P50)+扩展板套件设计,配置了1GB DDR3、16MB QSPI FLASH,搭配 HDMI 输出接口、千兆以太网、USB、摄像头接口、JTAG 调试接口和 40PIN 扩展口。适用于工业控制、安防监控、机器视觉、通信基带处理等应用场景。

用户可直接使用预置的 E901 处理器系统,专注于外设驱动、上层应用开发;高级开发者可利用 FPGA 可编程特性,进行处理器原型验证、专用指令集设计、算法硬件加速等前沿探索。

开放·连接,共创未来

RISC-V 国际基金会首席架构师 Krste Asanovic 曾言:“RISC-V 的成功源于其开放性。” 这种开放连接了全球的开发者,加速创造更美好的科技未来。

正因秉持开放连接的理念,RISC-V 生态正在以前所未有的速度扩张。ALINX AXPGL50 开发板在玄铁 RISC-V 生态大会上的亮相,正是这一浪潮中的一朵浪花——它让每一个开发者都能亲身触摸到 RISC-V 的脉搏,用最灵活的方式,定义属于自己的未来。

如果您对 ALINX 开发板感兴趣,欢迎访问 ALINX 官网 alinx.com 或联系我们021-67676997,获取更多技术资料与应用案例。

-

FPGA

+关注

关注

1663文章

22493浏览量

638947 -

嵌入式

+关注

关注

5209文章

20625浏览量

336758 -

RISC-V

+关注

关注

49文章

2941浏览量

53519

发布评论请先 登录

西门子EDA亮相2026玄铁RISC-V生态大会

RT-Thread 邀您参与“开放・连接”2026玄铁 RISC-V 生态大会,携手共铸 RISC-V“芯”纪元

RISC-V创新中心联合达摩院玄铁发布无剑芯片设计平台定制版

大咖集结·即刻报名 | 2026 玄铁 RISC-V 生态大会主论坛议程正式发布!

Powered by XuanTie,Qwen Inside:阿里通义大模型携手玄铁 RISC-V开启“端侧智能”新纪元

国芯科技入选2025 RISC-V产业发展大会优秀产品和解决方案

喜讯|昊芯RISC-V DSP荣获“中国芯”RISC-V生态推广奖

学以致用 虚位以待|玄铁RV学院课程正式上线,玄铁与PLCT实验室邀您创“芯”未来

出货量超40亿颗!玄铁RiSC-V凭何破局通推AI一体市场,撕开垄断缺口?

大湾区RISC-V生态全景展示:RISC-V生态发展论坛、开发者Workshop和生态应用专区

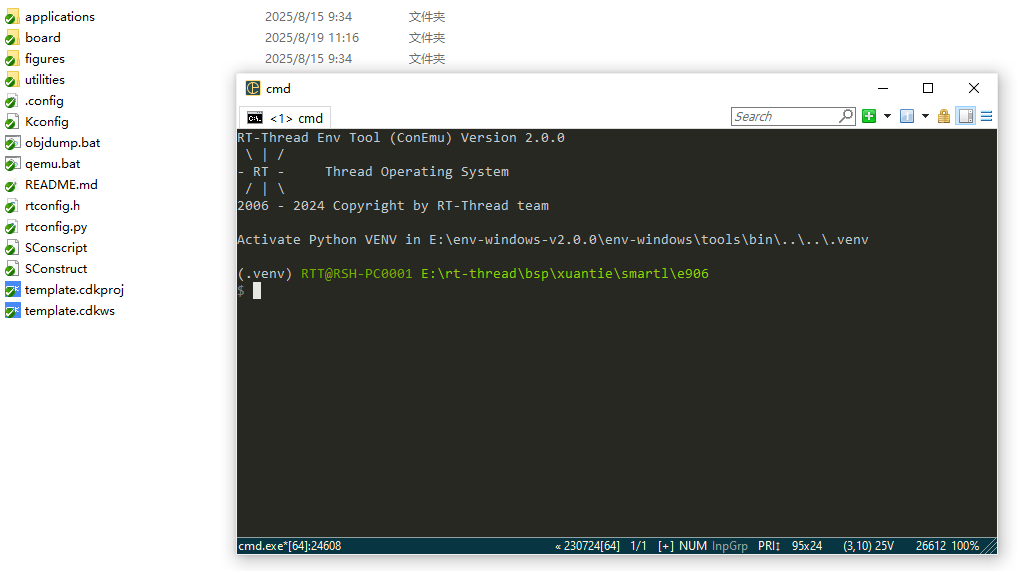

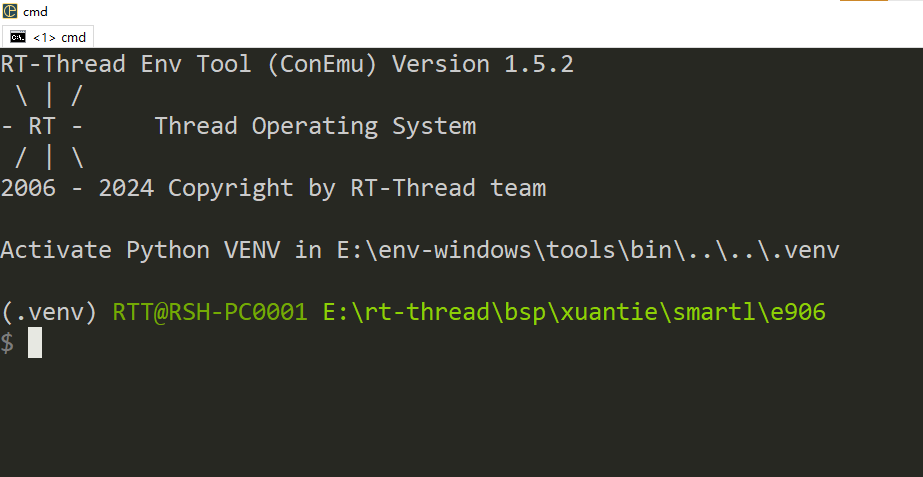

RT-Thread生成玄铁RISC-V BSP的CDK工程开发指南 | 技术集结

RT-Thread携手玄铁,全面展示 RISC-V 生态最新成果,期待莅临!

直击玄铁RISC-V生态大会,看ALINX FPGA+RISC-V解决方案

直击玄铁RISC-V生态大会,看ALINX FPGA+RISC-V解决方案

评论