Q1

现在bga值球客户退回来的,大家都是自己做的,还是交给封装厂或客户做的?

A

少量的样品,可以手动单个球补的。较多的样品,建议用植球工具加钢网的方式植球。或者委案到季丰做。

植球一般是BGA RMA回来,除了登记拍照外,FA步骤的第二步。不然I/V,ATE,都没法复测。如果要solder到system bench上,reball更加需要。(不然打磨平也许ATE也可以用)。

关于植球,有两个建议:一、植球或去除原来的solder ball之前一定要bake,建议bake 8小时125℃。bake,防止pop-corn效应,造成分层。很多本来没有分层(delamination)的,由于热操作造成二次损伤,样品原本的失效模式就容易误判;二、一定要用stencil,刮锡膏加热风枪,详细方法可参考手机维修时的植球,抖音上很多。

Q2

先进封装产品可能由ESD造成的测试Fail?当时送样不规范,未做静电防护。HTST168有1颗VOUT 失效,Precon有3颗失效,1颗IQ ,ISD失效,2颗 VOUT失效。应该做怎样的分析流程?我们这边做了X RAY和SAT,表面观察没发现啥异常。

A

首先失效的样品,要先确定失效样品的颗数和封装类型等,然后测下全pin脚的IV找到失效的管脚,可以再去倒推看下失效pin脚的x-ray 重点看下,也可以直接继续分析die定位问题。TE测试结果看一下,明显short,也可以快速的直接开盖看下是否有烧伤。若是送样不规范,造成样品fail,建议重新做可靠性测试。

Q3

现场回来的电路板,上电后PA没有功率输出,用温枪烘了一下又好了,可能是潮气的原因也可能是焊接原因,如果是潮气的原因怎么查能分析出芯片内部有水?

A

可以先用SAT看看是不是分层,或者用x ray 看看有没有虚焊。但是,SAT是不能验证潮气,因为超声波是能穿过水的,但超声波不能穿过空气,只能看分层,不能看有没有水。

检查湿气的方法:可以找个洗净,烘干的透明玻璃杯子,一定要有密封的玻璃盖子。把芯片放进去,高温下看看玻璃壁上有没有水汽。或者用军工上检查水汽的检漏仪,看看有没有水汽。或者你的电路板在120度环境下烘烤,如果烘烤前是坏的,烘烤后是好的,说明里面有水。因为120度,锡不会融化,锡要260度才可能融化。

如果是水汽引起的,是否想出办法从测试厂,拦截出这部分芯片,从封装厂或者晶圆厂找到原因。毕竟这种芯片多了,引起客诉挺严重。

Q4

热风枪的温度是400度,烘了几秒钟后好了。如果是水汽的话,400度芯片会不会爆掉?X-ray +红墨水是破坏性的么?

A

一般不会的,芯片本身分层严重的,有可能会加剧分层,个人感觉是SMT的焊接温度不够虚焊导致的。如果担心芯片有问题,可以用SAT、X-ray看看芯片有没有分层。

X-ray不是破坏性的,红墨水是破坏性的。

Q5

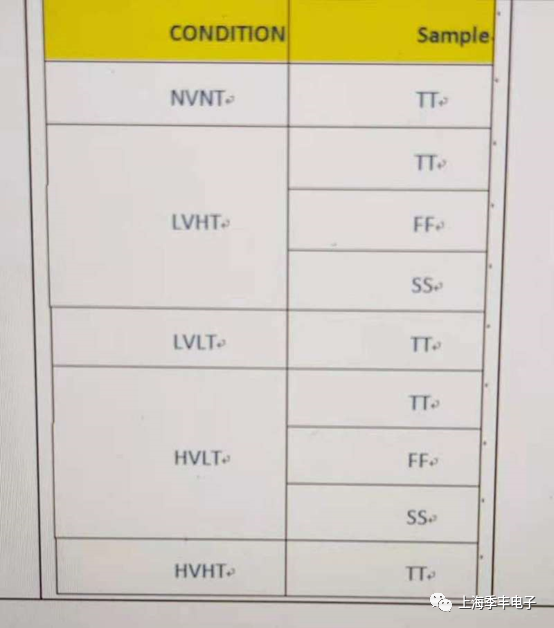

解释一下这个测试的参数都是什么含义吗?

A

condition看起来是电压温度条件,LVHT=low voltage high temperature。sample列应该是说的芯片对应corner。

Q6

CP或FT是否有专门针对芯片接口的功能测试pattern呢?比如验证芯片里的一个I2C接口或SGMII接口等。

A

对于ATE测试接口,这与芯片相关。I2C这种数字总线,可以通过pattern都寄存器来判断。sgmii这种差分总线一般是通过prbs来判断。也可以通过接口配置芯片,控制内部寄存器,读取寄存器,来验证接口。同时还可以测试芯片在不同配置下的各种功能和性能,就有覆盖率了。

Q7

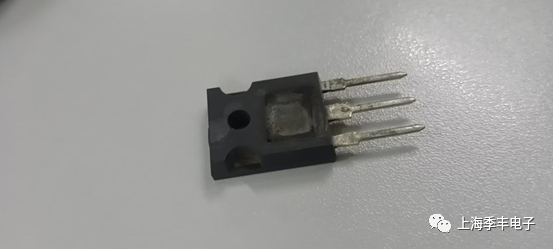

这种样品怎么开封?一直用laser看到wire bonding ,然后再用酸?用什么酸好?

A

laser 太浅了,需要继续腐蚀。本身塑封体很厚,所以需要尽可能的靠近die表面的,至少需要source的那根打线漏出来,再配合酸腐就可以了。像这种封装的芯片die 是一般是低于2焊点的。

可以用x-ray 看下,Al不清楚的情况下侧面去拍下,具体打线位置有个了解,用发烟硝酸来腐蚀。laser打到Al线脖颈处才停,再去滴酸。或者找季丰开封,即省事又有保证。

Q8

有谁知道在裸芯片上激光打标用什么设备?有型号推荐吗?

A

Si上要用绿色激光打标机。设备:大族、德龙激光。

Q9

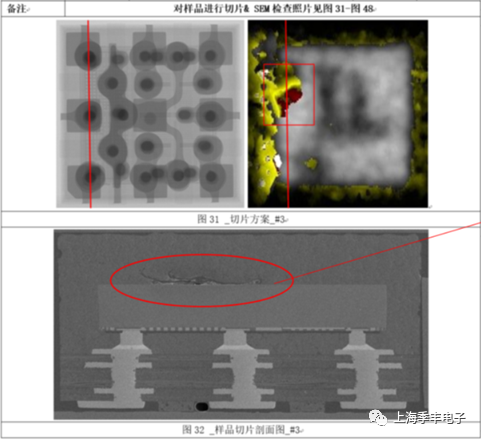

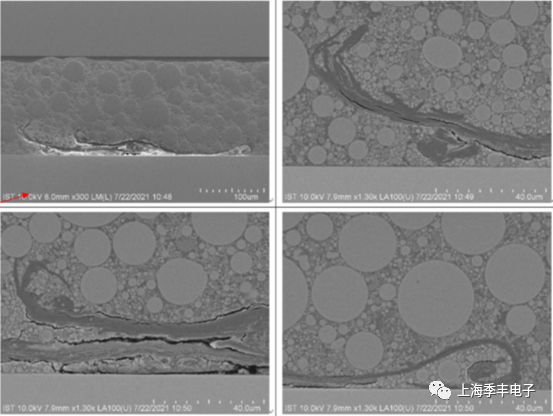

FCLAG产品SAT发现有异常,切片后发现有异物,成分分析主要为C、O、N(Al可能是制样时带入),大家帮忙分析下异物可能是什么,怎么产生的?

A

含N很有可能是CPD管道划到的塑胶,或者晶背的Tape residual。UV的蓝膜好像是含N的。

Q10

QFN封装做完预处理后epad上锡发生移动,有部分聚集现象,表面高低不平,这是怎么会事情?会不会影响后面的环境实验和ATE?那高高低低的ATE测试会否影响?

A

若是QFN背面少量的锡因为回流高温融化了,不影响后续的实验,融锡是正常的。但是芯片的表面高低不平,会导致pad和socket的pogopin出现接触问题,进而影响后续的实验。

Q11

芯片pad之间的间距有没有要求?

A

对边间距10um以上。

Q12

汽车级芯片一般FT要几个温度?-40 机台可以加么?CP作了数字扫描链检测,FT还是需要再做一遍么?CP和FT的测试项有哪些异同?

A

汽车级芯片一般FT要3个温度,handler一般可以到-55℃。

CP作了数字扫描链检测,FT可以不做,如果出于成本考量,CP侧重功能,FT侧重连接性。还有一些是CP不方便测,看具体device,比如SiP的肯定要CP测试。具体的可以参考DFT覆盖率和ATE覆盖率,里面内容都有定义的。

Q13

不做BTE了,直接就ATE有什么问题?

A

不能用ATE证明ATE。

Q14

如果测试覆盖率不够导致售后问题,是否就意味着推倒重来。或者新开发一款代替旧款?

A

那就想办法加test coverage。这个得自上而下理念。如果发现产品有某些缺陷前期各种测试没有覆盖到,后面处理起来就辛苦了。如果能及时找到规避方案还好。

在我看来,TEST coverage对于模拟就是把所有的block根据逻辑的依赖关系全拉出来测一遍,数字做扫描链,IO全测,加OS,还有就是加一些过压来看前后对比灭掉一些early failure。

还有,test case也要做全,考虑到各种应用环境。测试时长要够,抽样量要够。ATE和功能测试要匹配,测试指标要验证充分。

Q15

汽车级要求多少个ppm失效?

A

目标0,现在NXP 的标准是100PPB,100 PPB= 0.1PPM。

编辑:jq

-

封装

+关注

关注

128文章

9330浏览量

149044 -

电压

+关注

关注

45文章

5792浏览量

122384 -

BGA

+关注

关注

5文章

586浏览量

51950

原文标题:季丰电子IC运营工程技术知乎 – 21W30

文章出处:【微信号:zzz9970814,微信公众号:上海季丰电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

德州仪器TPS65176系列芯片封装及设计指南

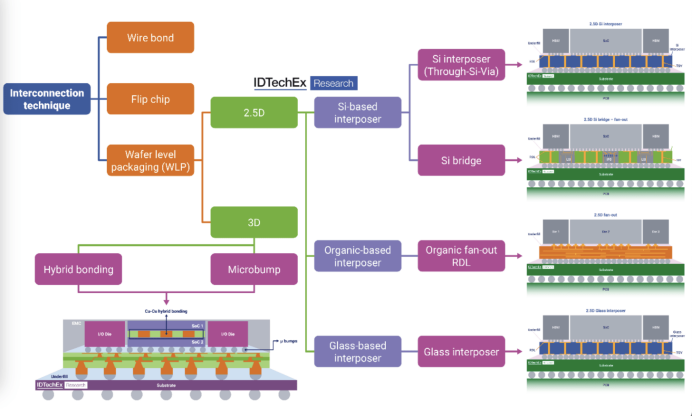

解析LGA与BGA芯片封装技术的区别

详解芯片封装的工艺步骤

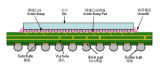

芯片封装之钼铜合金基板加工工艺优化与智凯中走丝技术的应用

写给小白的芯片封装入门科普

解疑答惑之芯片与封装

解疑答惑之芯片与封装

评论