在进行PCB设计时,我们经常会遇到各种各样的问题,如阻抗匹配、EMI规则等。本文为大家整理了一些和高速PCB相关的疑难问答,希望对大家有所帮助。

1、在高速PCB设计原理图设计时,如何考虑阻抗匹配问题?

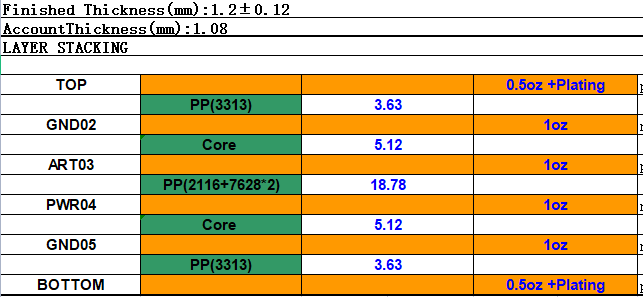

在设计高速 PCB 电路时,阻抗匹配是设计的要素之一。而阻抗值跟走线方式有绝对的关系,例如是走在表面层(microstrip)或内层(stripline/double stripline),与参考层(电源层或地层)的距离,走线宽度,PCB材质等均会影响走线的特性阻抗值。

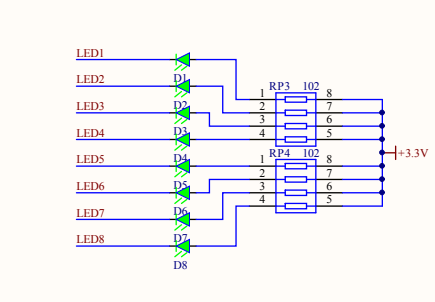

也就是说要在布线后才能确定阻抗值。一般仿真软件会因线路模型或所使用的数学算法的限制而无法考虑到一些阻抗不连续的布线情况,这时候在原理图上只能预留一些terminators(端接),如串联电阻等,来缓和走线阻抗不连续的效应。真正根本解决问题的方法还是布线时尽量注意避免阻抗不连续的发生。

2、当一块 PCB 板中有多个数/模功能块时,常规做法是要将数/模地分开,原因何在?

将数/模地分开的原因是因为数字电路在高低电位切换时会在电源和地产生噪声,噪声的大小跟信号的速度及电流大小有关。

如果地平面上不分割且由数字区域电路所产生的噪声较大而模拟区域的电路又非常接近,则即使数模信号不交叉,模拟的信号依然会被地噪声干扰。也就是说数模地不分割的方式只能在模拟电路区域距产生大噪声的数字电路区域较远时使用。

3、在高速PCB设计时,设计者应该从那些方面去考虑EMC、EMI的规则呢?

一般EMI/EMC设计时需要同时考虑辐射(radiated)与传导(conducted)两个方面。前者归属于频率较高的部分(》30MHz)后者则是较低频的部分(《30MHz)。所以不能只注意高频而忽略低频的部分。

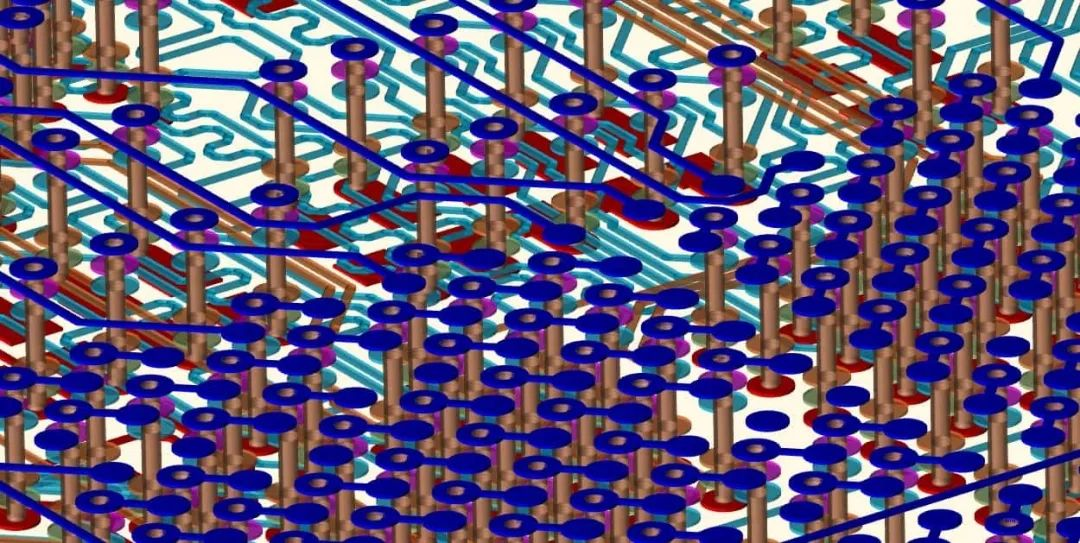

一个好的EMI/EMC设计必须一开始布局时就要考虑到器件的位置,PCB叠层的安排,重要联机的走法,器件的选择等,如果这些没有事前有较佳的安排,事后解决则会事倍功半,增加成本。

例如时钟产生器的位置尽量不要靠近对外的连接器,高速信号尽量走内层并注意特性阻抗匹配与参考层的连续以减少反射,器件所推的信号之斜率(slew rate)尽量小以减低高频成分,选择去耦合(decoupling/bypass)电容时注意其频率响应是否符合需求以降低电源层噪声。

另外,注意高频信号电流之回流路径使其回路面积尽量小(也就是回路阻抗loop impedance 尽量小)以减少辐射。还可以用分割地层的方式以控制高频噪声的范围。最后,适当的选择PCB 与外壳的接地点(chassis ground)。

4、在做PCB板的时候,为了减小干扰,地线是否应该构成闭和形式?

在做PCB板的时候,一般都要减小回路面积,以便减少干扰。布地线的时候,也不应布成闭合形式,而是布成树枝状较好,还有就是要尽可能增大地的面积。

5、怎样调整走线的拓扑架构来提高信号的完整性?

这种网络信号方向比较复杂,因为对单向,双向信号,不同电平种类信号,拓朴影响都不一样,很难说哪种拓朴对信号质量有利。而且做前仿真时,采用何种拓朴对工程师要求很高,要求对电路原理,信号类型,甚至布线难度等都要了解。

6、在布局、布线中如何处理才能保证100M以上信号的稳定性?

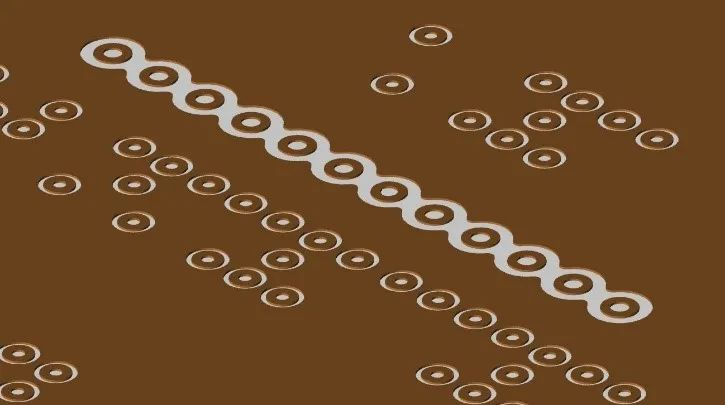

高速数字信号布线,关键是减小传输线对信号质量的影响。因此,100M 以上的高速信号布局时要求信号走线尽量短。数字电路中,高速信号是用信号上升延时间来界定的。

而且,不同种类的信号(如 TTL,GTL,LVTTL),确保信号质量的方法不一样。

编辑:jq

-

pcb

+关注

关注

4222文章

22475浏览量

385885 -

emc

+关注

关注

165文章

3644浏览量

181175 -

电源层

+关注

关注

0文章

18浏览量

8291

原文标题:干货 | 6个和高速PCB相关的疑难问题

文章出处:【微信号:电子工程世界,微信公众号:电子工程世界】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

教你们6个和高速PCB相关的疑难问题

教你们6个和高速PCB相关的疑难问题

评论