毕业进入集成电路封装这个行业马上15年了,工作地点换了三个:张江、青浦、江阴,企业也换了三个台资、外资和民营。从维修工程师、初级制程工程师到制程工程师,再到新产品导入经理,转入客服工程部门做经理;从自己给客户调试产品,到教工程师给客户做产品,再到跨部门协调大家给客户导入产品。所谓“久病成医”吧,我非常乐意分享一点自己对封装过程中风险评估的浅显理解,希望对有需要的公司、朋友提供一点帮助,希望祖国的的半导体产业早日强大。

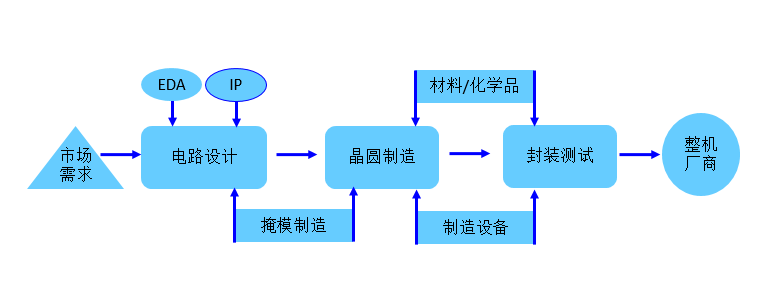

大体而言集成电路产业可分为三个阶段:电路设计,晶圆制造,封装测试。电路设计大体是一群电路系统毕业的学霸搞出来的(因为学霸,所以高薪),他们把设计好电路给晶圆制造厂(台积电、联电、中芯国际……),最后圆片从晶圆厂发货到封装测试厂(日月光、安靠、长电科技……)。简而言之的流程就这样啦,如果想知道更加详细的可以去咨询下度娘。

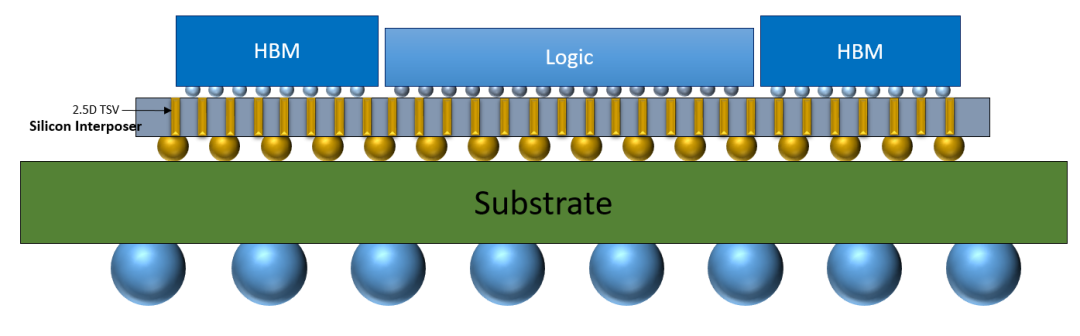

图1

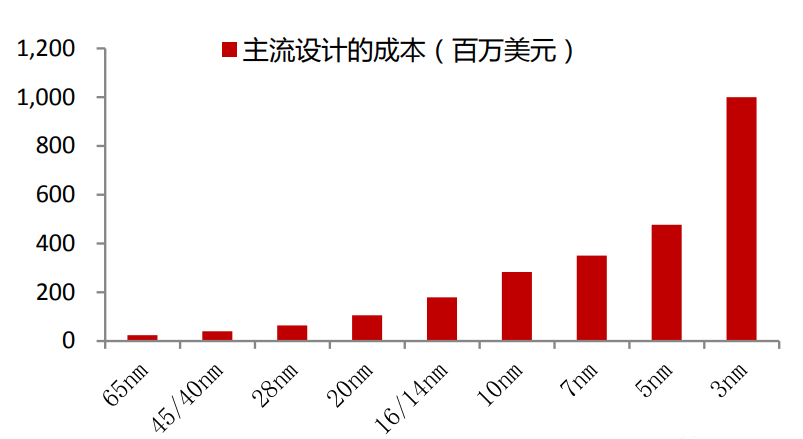

刚入行的时候,师傅就告诫说:千万别把圆片摔坏了,一片等于一辆宝马。现在知道圆片本身的价格只是百万分之一,最低端的芯片工艺从设计出来到成功流片至少百万人民币,而高端的5纳米工艺,那就是天文数字据说到了4~5亿美金。试想如果芯片流片成功,不能正常封装、量产、没法按计划推向市场,那将是多么悲剧的一件事情,轻则伤筋动骨掉几斤肉,重则公司关门大吉、人去楼空。市场的事情让市场去说,技术的事情让搞技术的人来谈。作为封装厂客服部门的工作人员,建议设计公司在项目启动之初就要和封装厂进行系统的TRA技术风险评估(TRA:Technical Risk Assessment)对接工作,防患于未然。

图2

一般来说,设计公司与封装工厂做TRA对接的最佳节点有4个:封装选型、项目启动之初,封装定版、样品制作、Pre-Qual.阶段,Formal Qual.封装测试和可靠性阶段,预量产阶段。

1.封装选型、项目启动之初的TRA

通常而言,初创设计公司都会去照抄竞争对手的样品封装,形成Pin-To-Pin的替换关系,便于打开终端市场,掘取第一桶金。而但凡有想法的设计公司,自己会去找到终端客户提供客制化芯片设计服务(比如功能、形状、特性)。这时设计公司就会面临封装选型的问题,比较什么类型封装、封装3D尺寸、管脚的数量/间距甚至封装材质。如果封装选型正确,可以不用开发新框架、新基板,不用买封装模具,可以省去大概2-3个月左右的时间;如果选型错误,需要设计、购买新框架或基板,甚至需要购买封装模具,这会耗用大概3-5个月时间和约10-50万的资金投入。另外一个,芯片的Bond Pad尺寸设计、Test Pad设计、Bond Pad布局也会影响到封装,比如芯片的Bond Pad设计为40um,而芯片性能需要用25um的焊线,这就会超封装设计规范(因为焊球的尺寸一般为2-3倍焊线直径,不得超出Bond Pad);又如Bond Pad布局不合理导致焊线交叉,甚至在超薄封装中做交叉焊线,这就面临封装难度增加甚至喊停;测试Pad只是给晶圆厂 Chip Probe用的,跟封装无关?No No No,因为如果测试Pad放在切割道中间,会导致封装厂必须使用激光开槽技术为刀切开路,使得封装成本增加。所以在封装选型、项目启动之初,就要跟封装厂初步定好封装方案,和基本的项目进度表,双方在统一的平台上使用统一的语言顺畅沟通,我们可以暂且给这个阶段的技术风险评估取名为TRA1。

2. 封装图初定、样品制作、Pre-Qual.阶段的TRA

我们可以把封装图初定、样品制作和Pre-Qual.这个阶段比喻成设计公司的孩子在学习“站立”。孩子站稳当了,后面才能学走路和跑步。封装图初定的时候,小的封装工厂可能靠单个工程师的经验做风险评估,专业的封装工厂会找一群工程师做风险评估,也许未来的封装工厂会用系统做风险评估。根据封装工厂提供的风险评估结果,一般而言封装工厂会自我风险闭环,确保识别出来的风险能被监控到位,不带病进入正式Qual.。如果某个站别的风险比较高,通常封装厂会建议客户投小量芯片进行DOE验证(Design Of Experiment),确定封装工艺参数区间。样品制作阶段就意味这流程、原材料都已经初定了,工厂按照Qual的、量产的流程进行生产,这一步完成后大家可以拿到封装良率、样品性能数据、测试良率三个数据,数据由设计公司和封装厂双方核对、判读,确认是否需要做出工艺、原材料甚至打线图的调整,为正式Qual.的工作做好准备工作。这项工作结束之后,可以请封装厂出具第二版技术风险评估报告,可简称为TRA2。

3.Formal Qual.和可靠性阶段的TRA

如果说前面的电性样品、Pre-Qual.是孩子在学习站立,那正式Qual.和可靠性就是孩子在学习走路了。产品进入正式Qual.阶段,也就意味风险都已经得到非常大的释放,这当中会产生大量的数据收集、封测Qual.报告和可靠性报告,其中盖公章的可靠性报告是产品打开市场的通行证。普通的产品下1批Formal Qual.即可,封装完成后进行测试,并选取测试良品安排可靠性;重要的产品或供重要的终端,通常会安排3批Formal Qual.,并分别取测试良品安排可靠性。更有讲究的设计公司会要求更加严苛,比如封装过程中必须使用不同批次的原材料,必须安排在不同班别时间和人员生产,必须使用同一型号而不同机台号码的设备;安排测试良品进行DPA(Destroy Physical Analysis),确认封装工艺中的重要监控项目是否达标。取得测试良品安排可靠性之后,一般就可以准备转量产审核了。可靠性项目和数量视设计公司或终端要求来定,一般来说250颗就够了,基本的项目含有MSL,TCT,HTSL,PCT等。在封装作业性正常、封装测试良率达标且可靠性通过的情况下,产品即可顺利转入量产。其实这个阶段完成之后,所有的技术风险已经得到了充足的释放,在TRA2的基础上略微更新即可生成TRA3。

4.初期量产阶段的TRA

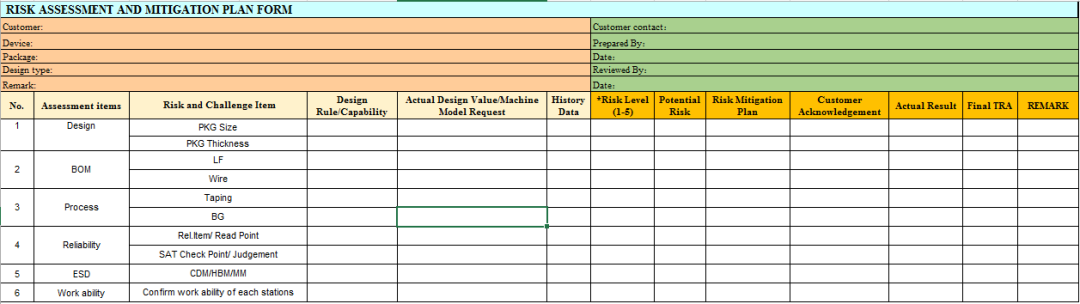

通常而言孩子学会走路不是目的,而学会奔跑才是重点,这个时代的变化太快了。产品经过双方及双方内部认可产品转入初期量产,有的工厂卡控初期量产的批次数量,也有的工厂卡控下单的数量。在这个阶段我们要注意,双方都可能存在责任部门转换的问题,比如在封装工厂,初期量产前的工作都是由CE (Customer Engineer)部门主导,进入初期量产阶段主导工作会转移到PE(Process Engineer)和CQE(Customer Quality Engineer);而在大型的设计公司,项目也会从NPI(New Product Income)转入到PE(Process Engineer)阶段。在这个阶段,责任承接部门通常会要求收集一些封装和测试的数据,比如Top Defect分析、封装和测试良率。如果确认产品质量或封装测试良率有问题,项目有可能会退回到Qual.阶段(虽然这种情形很少见到)。收集到完整的封装、测试数据,Top Defect分析后,在TRA3的基础上可以生成TRA4,通常而言这个项目可以说导入结束啦。表1是国内某工厂的TRA模板,供大家参考使用。

表1

最后讲个扁鹊三兄弟的故事吧。魏文王问扁鹊曰:“子昆弟三人其孰最善为医?”扁鹊曰:“长兄最善,中兄次之,扁鹊最为下。”魏文侯曰:“可得闻邪?”扁鹊曰:“长兄於病视神,未有形而除之,故名不出於家。中兄治病,其在毫毛,故名不出於闾。若扁鹊者,镵血脉,投毒药,副肌肤,闲而名出闻於诸侯。”

在做技术风险评估能力的所有等级中,当视“未有形而除之”为最高境界。希望通过这篇小文,电路设计从业人员、集成电路项目管理人员和有兴趣的朋友可以从中得到启发,尽早识别出项目的风险并解决,让项目更加顺利启动、进行和完成!

责任编辑:lq

-

集成电路

+关注

关注

5464文章

12681浏览量

375670 -

电路系统

+关注

关注

0文章

75浏览量

13402 -

晶圆制造

+关注

关注

7文章

318浏览量

25348

原文标题:浅谈集成电路封装过程中的风险评估

文章出处:【微信号:半导体科技评论,微信公众号:半导体科技评论】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

集成电路产业可分为三个阶段:电路设计,晶圆制造,封装测试

集成电路产业可分为三个阶段:电路设计,晶圆制造,封装测试

评论