文章来源:学习那些事

原文作者:小陈婆婆

本文介绍了晶圆拣选测试的目标、具体过程以及核心要点。

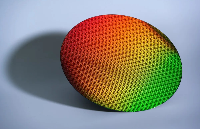

在半导体制造流程中,晶圆拣选测试(Wafer Sort)堪称芯片从“原材料”到“成品”的关键质控节点。作为集成电路制造中承上启下的核心环节,其通过精密的电学测试,为每一颗芯片颁发“质量合格证”,同时为工艺优化提供数据支撑。

1测试目标

一、核心目标

晶圆拣选测试的核心目标可拆解为四大维度:

功能验证的“全身体检”

通过探针卡与芯片焊盘的物理接触,测试系统依据DC(直流)、AC(交流)及功能规范,对芯片进行全信号通路检测。这相当于为芯片设计了一套“体检套餐”:

AC测试:考核信号传输速度、建立保持时间等动态特性

功能测试:通过向量激励验证数字/模拟电路功能实现

只有通过所有测试项的芯片,才能获得进入封装工序的“通行证”。

性能分级的“赛道划分”

对合格芯片实施速度分级(Speed Binning),通过调整测试条件(如电压、温度、时钟频率),将芯片按工作速度划分为不同等级。例如:

高速档:适用于高性能计算芯片

标准档:满足消费级产品需求

这种分级策略可实现芯片价值的最大化利用,避免“大材小用”或“小材大用”。

制造成品率的“健康诊断”

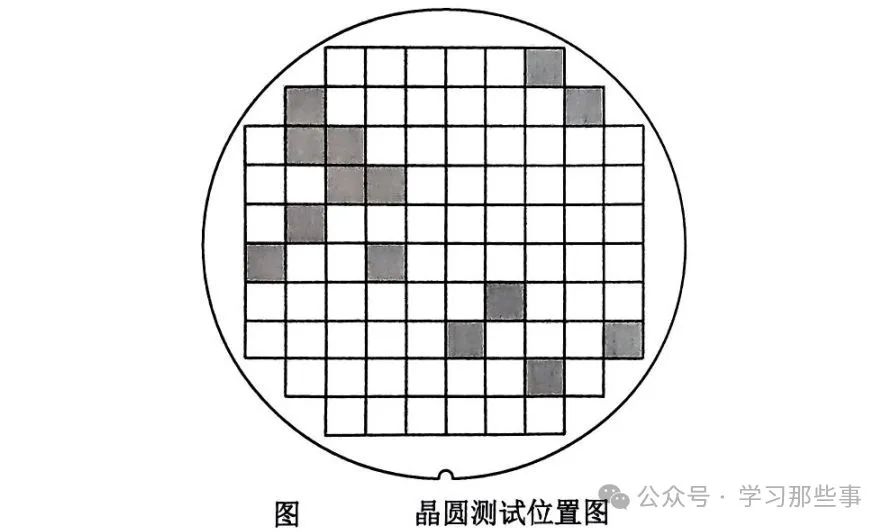

测试数据会生成晶圆级良率地图(Wafer Map),通过空间分布分析可追溯失效模式:

环形失效:可能源于光刻胶涂布不均

边缘聚集失效:需检查研磨工艺参数

随机点状失效:需排查晶圆本身缺陷

这些数据为工艺工程师提供了“CT扫描”般的诊断依据。

测试覆盖率的“成本平衡”

在测试成本与缺陷检出率之间寻求最优解,采用:

结构化测试:通过扫描链(Scan Chain)检测内部节点

边界扫描(JTAG):验证芯片间互连完整性

先进测试策略可使测试覆盖率达99%以上,同时控制测试时间在秒级。

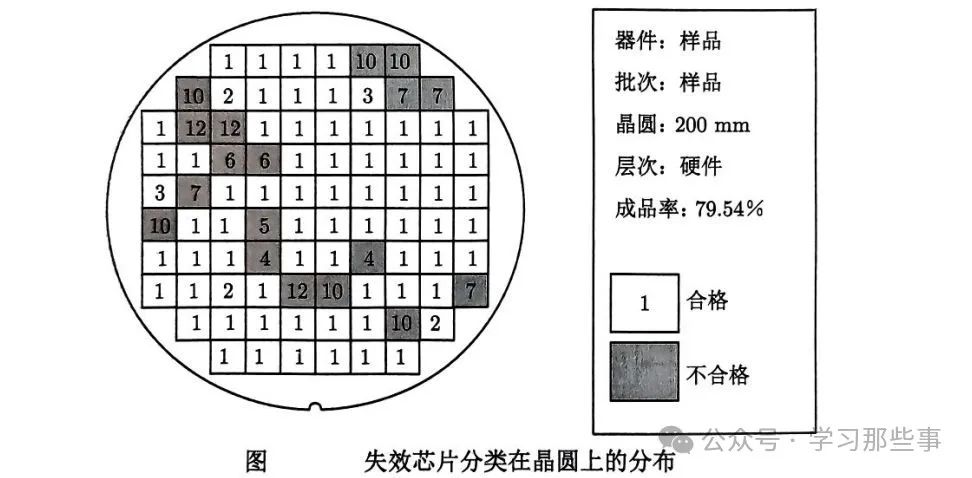

二、失效芯片的“溯源追踪”

现代测试系统采用失效分类编码(Binning)体系,将失效模式数字化:

Bin8/9:开路/短路失效,可能源于金属层刻蚀残留

Bin12:功能失效,可能涉及IP核设计缺陷

通过空间映射(Mapping)技术,可将编码数据与晶圆坐标关联,生成三维失效热图。结合制程数据(如机台编号、批次信息),可实现:

工艺相关失效:如化学机械抛光(CMP)导致的金属层凹陷

机台相关失效:某光刻机台对焦系统漂移引发的套刻偏差

材料相关失效:特定晶圆批次氧化层针孔密度超标

三、行业实践的演进方向

当前晶圆拣选测试正呈现三大趋势:

大数据驱动的预测性分析:通过机器学习建立测试数据与工艺参数的关联模型,实现缺陷预测

云测试平台:将测试数据上传云端,进行跨工厂、跨批次的质量追溯

先进封装适配:针对2.5D/3D封装需求,增加TSV通孔测试、微凸点检测等专项测试

作为半导体制造的“质量守门人”,晶圆拣选测试不仅守护着芯片良率的生命线,更通过失效数据的深度挖掘,持续推动着制造工艺的迭代进化。随着节点向3nm及以下推进,测试技术与工艺开发的协同创新,将成为突破物理极限的关键路径。

2晶圆拣选测试

晶圆拣选测试——半导体质量的“三重防火墙”

在半导体制造中,晶圆拣选测试(Wafer Sort)通过直流测试(DC Test)、输出检查(Output Check)和功能测试(Functional Test)构建起芯片质量的“三重防火墙”。这三类测试从电气特性、性能参数到逻辑功能,对芯片进行全方位“体检”,确保只有合格的芯片进入封装阶段。以下从行业实践角度,对三类测试进行技术拆解与案例分享。

一、直流测试(DC Test):芯片的“基础体检”

直流测试是芯片质量的“第一道关卡”,聚焦于芯片的静态电气特性,核心目标包括:

1.连接性验证(Continuity Check)

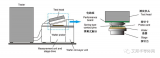

测试原理:通过探针卡与芯片压点(Pad)的物理接触,检测每根探针与对应焊盘的导通性。

行业价值:避免因探针接触不良导致的“假性失效”,例如探针微小偏移可能引发开路误判,需通过低阻值阈值(通常<10Ω)确认接触可靠性。

2.开路/短路检测(Open/Short Test)

短路:端口间电阻<10Ω(阈值因工艺而异),可能由金属层刻蚀残留或光刻胶残留导致。

开路:端口间电阻>1MΩ,常见于通孔未打通或金属线断裂。

案例:某12英寸晶圆边缘出现规律性开路失效,经分析为化学机械抛光(CMP)工艺压力不均导致金属层断裂。

3.漏电流测试(Leakage Test)

测试对象:截止态晶体管(如CMOS的PMOS/NMOS)或ESD保护电路。

行业挑战:随着节点推进至5nm以下,量子隧穿效应导致亚阈值漏电显著增加,需通过IDDQ测试(静态漏电流测试)筛选高漏电芯片。

标准参考:工业界通常要求漏电流<1μA/门(Gate),否则芯片可能因静态功耗超标被淘汰。

二、输出检查(Output Check):性能的“压力测试”

输出检查聚焦于芯片输出端口的驱动能力,模拟实际工作负载条件,验证其带负载能力:

1.灌电流(Sink Current)与拉电流(Source Current)测试

测试方法:

灌电流:在输出端施加低电平(如0V),测量可吸入的最大电流(如8mA),同时检测低电平电压(VOL)是否≤0.4V。

拉电流:在输出端施加高电平(如VDD),测量可输出的最大电流(如4mA),同时检测高电平电压(VOH)是否≥0.8VDD。

行业意义:输出电平稳定性直接影响芯片与其他器件的信号完整性。例如,某款MCU因输出驱动能力不足,导致I2C总线在长距离传输时信号失真。

2.动态负载模拟

先进实践:通过可编程负载板模拟电容性负载(如10pF~50pF),测试输出信号的上升/下降时间(Tr/Tf)。

案例:某高速接口芯片在50Ω负载下Tr=0.5ns达标,但接入10pF电容后Tr延迟至2ns,需优化输出级驱动电路。

三、功能测试(Functional Test):逻辑的“全场景验证”

功能测试是芯片质量的“终极考验”,通过输入测试向量(Test Pattern)验证逻辑正确性,覆盖数字电路与存储器两大领域。

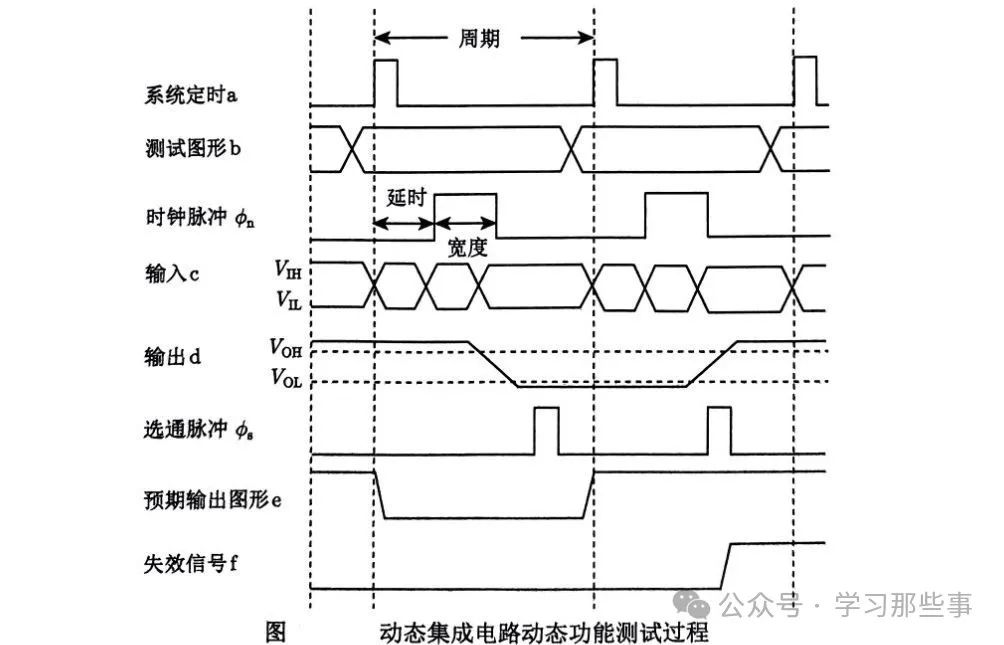

1. 数字电路功能测试

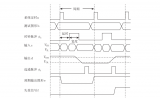

测试流程:

测试向量生成:采用ATPG(自动测试模式生成)工具生成覆盖所有故障模型的向量(如Stuck-at、Transition、Path Delay)。

动态测试:通过时钟脉冲(CLK)驱动输入信号,比较器(Comparator)实时检测输出电平(VOH/VOL)是否符合规范。

故障诊断:若输出与预期不符,通过故障字典定位到具体门电路或节点。

行业挑战:

测试覆盖率:需覆盖99.9%以上的逻辑门,但先进工艺中随机缺陷(如桥接、开路)仍可能导致逃逸。

测试时间优化:采用压缩算法(如CompactTest)将测试时间从数小时压缩至分钟级。

2. 存储器功能测试

存储器测试需覆盖地址译码、存储阵列、读出放大器等模块,常见故障包括:

硬故障(Hard Fault):

地址多重选择:一个地址选中多个单元(如字线短路)。

存储内容固定:无论写入何值,读出数据恒为“0”或“1”(如晶体管阈值电压漂移)。

软故障(Soft Fault):

读后恢复时间过长:读出放大器在连续读取相同数据后,无法快速切换状态(如电荷泵响应延迟)。

写后恢复时间过长:写操作后需等待一定时间才能读取正确数据(如位线电容放电不充分)。

测试方法:

March算法:通过递增/递减地址序列,检测相邻单元干扰(如March C+算法可覆盖95%以上的存储器故障)。

IDDQ测试:检测静态漏电,筛查字线/位线短路等隐蔽故障。

行业趋势:从测试到数据驱动的工艺优化

现代晶圆拣选测试已超越“质检”范畴,成为工艺优化的数据引擎:

大数据分析:通过测试数据与机台参数(如光刻机曝光能量、刻蚀机腔体压力)的关联分析,实现故障根源追溯。

AI赋能测试:采用机器学习模型预测测试逃逸率,动态调整测试向量优先级。

云测试平台:将测试数据上传至云端,支持跨工厂、跨批次的良率对比与缺陷共享。

3晶圆拣选测试核心要点

晶圆拣选测试核心要点:效率、精度与可靠性的三角平衡

在半导体制造中,晶圆拣选测试(Wafer Sort)是芯片从晶圆到封装的关键质控环节,其核心目标是在最短测试时间内,精准筛选出合格芯片,同时为工艺优化提供数据支撑。随着集成电路规模突破百亿级晶体管,测试效率与缺陷覆盖率的矛盾日益凸显。以下从行业实践角度,对晶圆拣选测试的四大核心要点进行技术解析。

一、测试消耗时间:效率与成本的博弈

测试时间直接关联到制造成本与产能利用率。以超大规模集成电路(VLSI)为例,其测试时间可能长达数小时,成为产能瓶颈。优化测试时间需从设计源头入手:

1.可测性设计(DFT)

内建自测试(BIST):在芯片设计中嵌入专用测试电路(如扫描链、MBIST控制器),绕过功能路径直接对关键模块(如存储器、锁相环)进行自检。例如,某款AI芯片通过BIST将测试时间从4小时压缩至30分钟。

并行测试:对数字、模拟、射频等混合信号电路实施同步测试。例如,某5G SoC芯片通过数字-模拟并行测试,将测试时间减少40%。

2.测试算法优化

压缩技术:采用差分测试向量压缩算法(如Golomb编码),将测试数据量减少50%以上。

自适应测试:根据前序测试结果动态调整后续测试向量,避免冗余操作。

二、失效模式:从“症状”到“病因”的溯源

集成电路故障可归纳为三大类,其检测需针对性设计测试向量:

1.固定故障(Stuck-at Fault)

表现:节点逻辑值永久固定为“0”或“1”,可能由晶体管栅氧击穿或金属层开路导致。

检测:通过全“0”/全“1”测试图形或March算法覆盖99%以上的固定故障。

2.桥接故障(Bridging Fault)

表现:非连接节点间意外导通(如金属层刻蚀残留导致相邻线短路)。

检测:棋盘测试图形可检测相邻单元干扰,但需结合电子束检测(EBI)定位物理缺陷。

3.延迟故障(Delay Fault)

表现:信号传输时序违反规范(如建立/保持时间不足),可能由互连线RC延迟增大导致。

检测:通过动态测试(At-Speed Test)在最高工作频率下施加时序紧张的测试向量。

三、静态漏电流测试(IDDQ Testing):缺陷的“显微镜”

IDDQ测试通过测量静态漏电流(通常为nA级)检测隐蔽缺陷,其原理基于CMOS电路的互补特性:

1.测试原理

正常CMOS电路在静态时,PMOS与NMOS管中仅有一个导通,漏电流极小(<1μA)。

工艺缺陷(如栅氧针孔、金属层空洞)可能导致漏电流激增至μA级甚至mA级。

2.行业价值

缺陷覆盖率提升:可检测传统功能测试无法覆盖的缺陷(如亚阈值漏电)。

工艺监控:IDDQ分布可反映光刻、刻蚀等关键工艺的稳定性。

3.局限性

诊断困难:IDDQ异常仅能提示缺陷存在,需结合物理失效分析(PFA)定位根源。

先进工艺挑战:FinFET及GAA晶体管导致漏电基准降低,需升级测试设备精度。

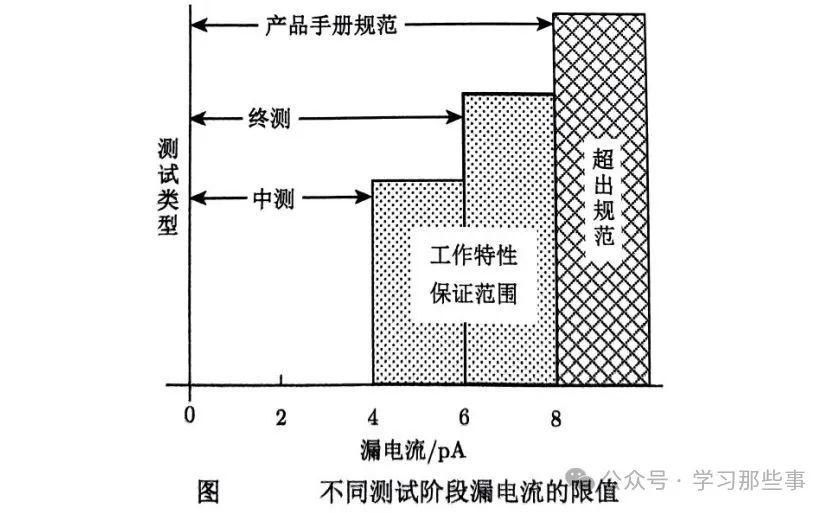

四、正常工作保障范围测试:可靠性的“护城河”

为确保芯片在全生命周期内可靠工作,需在测试阶段设置比规格更严苛的限值:

1.guard banding策略

漏电限值加严:例如,用户规格为8pA漏电,中测阶段采用4pA限值,终测阶段采用6pA限值,以抵消工艺波动与测试误差。

电压/温度裕量:在高温(125℃)或低压(VDD-10%)条件下验证功能正确性。

行业案例

汽车电子:AEC-Q100标准要求芯片在-40℃~150℃范围内通过动态测试,漏电流限值比消费级产品严格50%。

数据中心CPU:通过加速寿命测试(ALT)模拟10年使用场景,确保IDDQ在寿命末期仍低于规格。

五、行业趋势:从“被动检测”到“主动预防”

现代晶圆拣选测试正呈现两大趋势:

AI赋能测试:通过机器学习模型预测测试逃逸率,动态调整测试向量优先级。例如,某代工厂利用AI将测试时间减少30%,同时保持99.9%的故障覆盖率。

云测试平台:将测试数据上传至云端,进行跨工厂、跨批次的良率对比与缺陷共享。例如,某IDM企业通过云平台实现全球Fab数据实时分析,将缺陷定位时间从数天缩短至数小时。

晶圆拣选测试的四大要点——测试时间优化、失效模式分析、静态漏电流检测与保障范围测试,构成了半导体制造的“效率-精度-可靠性”三角平衡。随着节点向2nm及以下推进,测试技术与工艺开发的协同创新,将成为突破物理极限、保障芯片性能的关键路径。

-

集成电路

+关注

关注

5446文章

12469浏览量

372688 -

半导体

+关注

关注

336文章

29985浏览量

258306 -

晶圆

+关注

关注

53文章

5345浏览量

131690

原文标题:半导体制造的质量守门人——晶圆拣选测试

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

晶圆制造工艺的流程是什么样的?

晶圆测试探针台的组成以及晶圆测试的重要性和要求

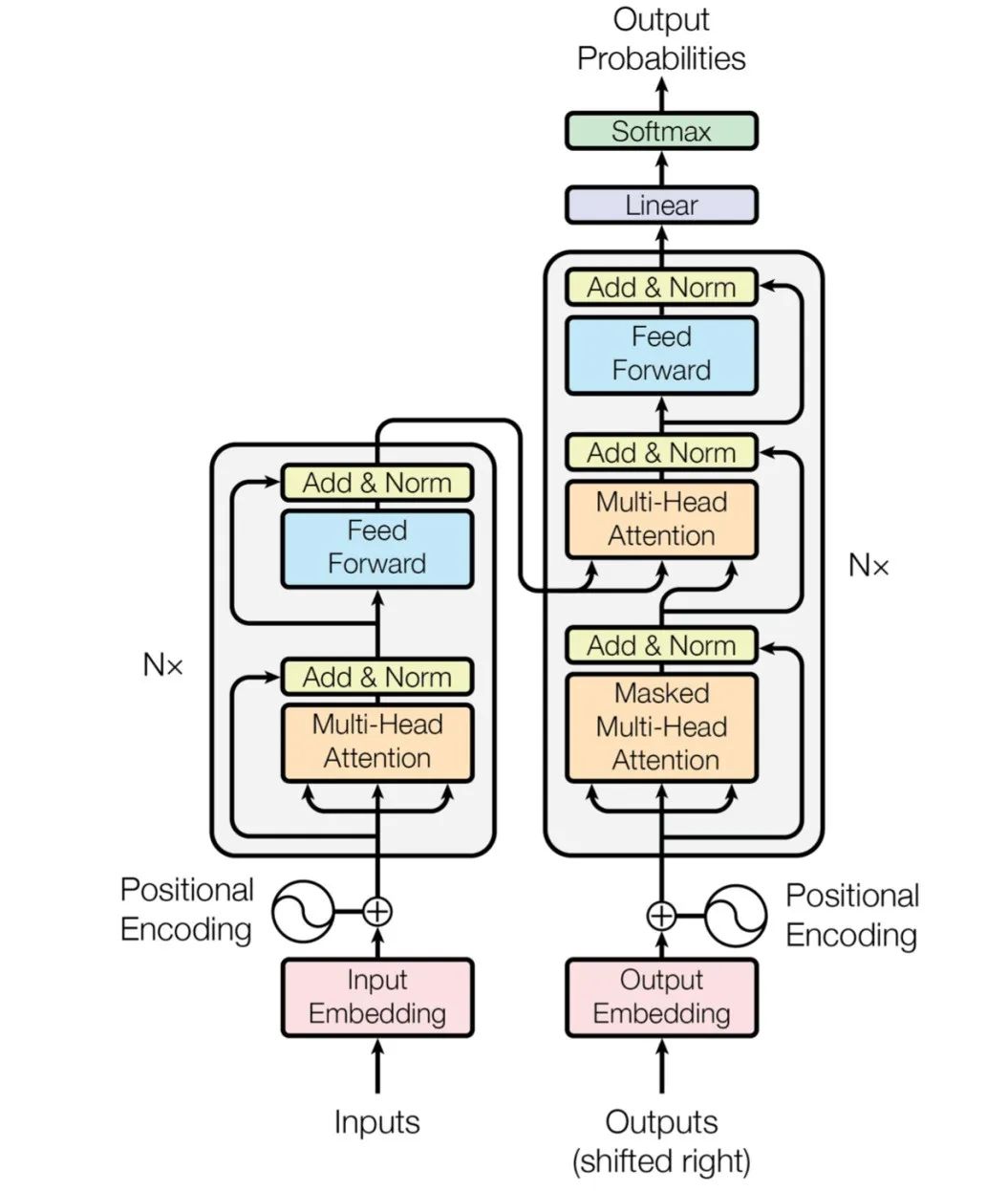

ChatGPT的核心要点

晶圆清洗后表面外延颗粒要求

晶圆拣选测试的具体过程和核心要点

晶圆拣选测试的具体过程和核心要点

评论