一、时钟相关概念

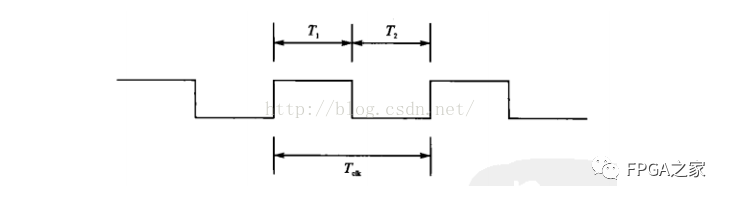

理想的时钟模型是一个占空比为50%且周期固定的方波。Tclk为一个时钟周期,T1为高脉冲宽度,T2为低脉冲宽度,Tclk=T1+T2。占空比定义为高脉冲宽度与周期之比,即T1/Tclk。

图1 理想时钟波形

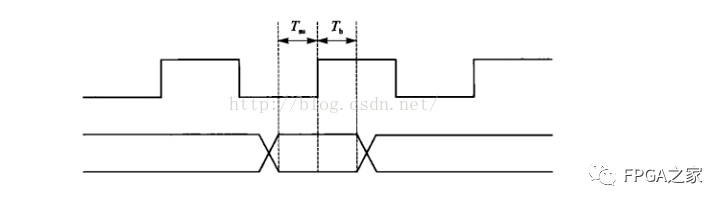

建立时间(Tsu):是指在时钟上升沿到来之前数据必须保持稳定的时间;

保持时间(Th):是指在时钟上升沿到来以后数据必须保持稳定的时间。如图2所示。

图2 建立和保持时间

一个数据需要在时钟的上升沿锁存,那么这个数据就必须在这个时钟上升沿的建立时间和保持时间内保持稳定。

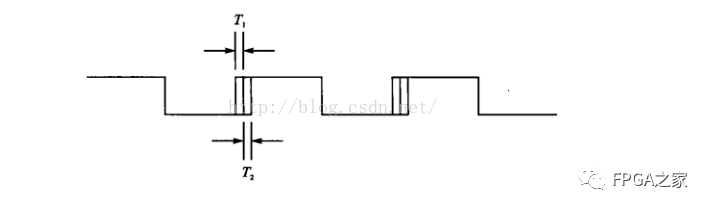

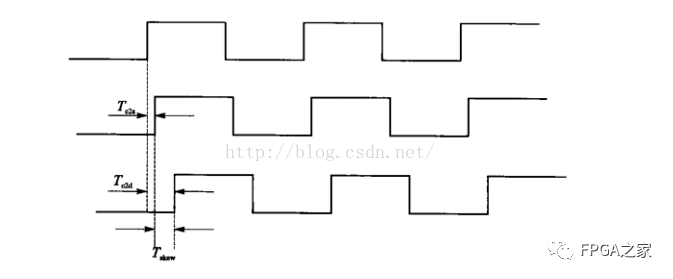

上面列举的是一个理想的时钟波形,而实际时钟信号的分析要比这复杂得多。时钟本身也具有一些不确定性,如时钟抖动(jitter)和时钟偏斜(sknew)等。时钟的边沿变化不可能总是理想的瞬变,它会有一个从高到低或者从低到高的变化过程,实际的情况抽象出来就如图3所示,时钟信号边沿变化的不确定时间称之为时钟偏斜(clock skew)。再回到之前定义的建立时间和保持时间,严格的说,建立时间就应该是Tsu+T1,而保持时间就应该是Th+T2。

图3 时钟抖动模型

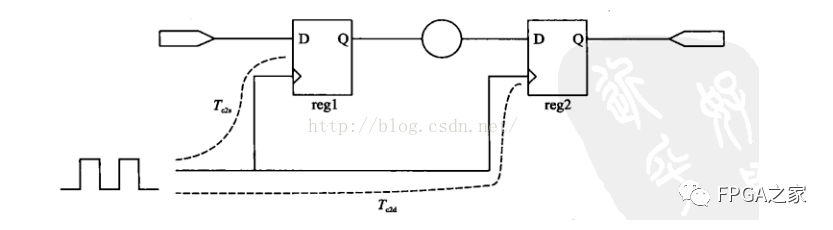

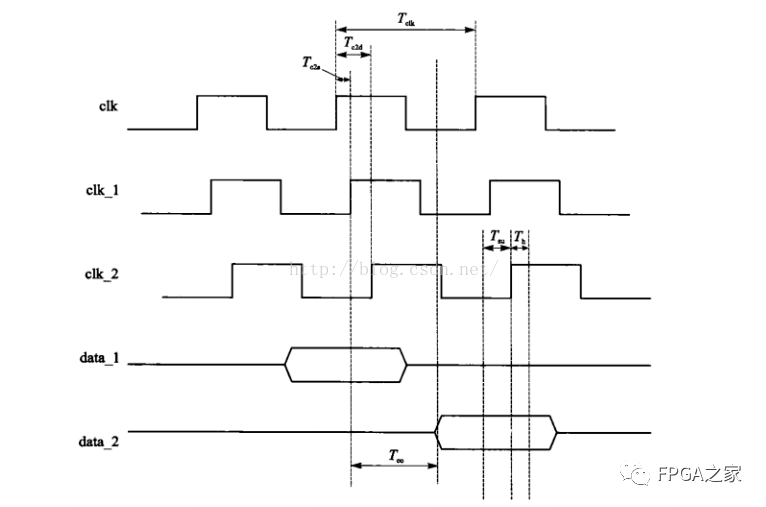

时钟分析的起点是源寄存器(reg1),终点是目的寄存器(reg2)。时钟和其他信号的传输一样都会有延时。图4中,时钟信号从时钟源传输到源寄存器的延时定义为Tc2s,传输到目的寄存器的延时定义为Tc2d,时钟网络延时就定义为Tc2d与Tc2s之差,即Tskew=Tc2d-Tc2s。

图4 时钟偏斜的寄存器传输模型

图5是时钟偏斜模型的波形表示。

图5 时钟偏斜的波形图

clk是源时钟,可以认为是一个理想的时钟模型。clk_1是时钟传输到源寄存器reg1的波形(延时Tc2s),clk_2是时钟传输到目的寄存器reg2的波形(延时Tc2d)。data_1是数据在源寄存器reg1的传输波形,data_2是数据在目的寄存器reg2的传输波形。

图6 数据与时钟关系

原文标题:时钟相关概念

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

FPGA

+关注

关注

1663文章

22494浏览量

638993 -

数据

+关注

关注

8文章

7347浏览量

95007 -

时钟

+关注

关注

11文章

1999浏览量

135225

原文标题:时钟相关概念

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Xilinx FPGA中的混合模式时钟管理器MMCME2_ADV详解

浅谈FPGA的时钟输入要求

Xilinx FPGA中IDELAYCTRL参考时钟控制模块的使用

原子钟相较于晶振有哪些特殊优势

数字IC/FPGA设计中的时序优化方法

如何使用FPGA实现SRIO通信协议

FPGA的基础概念和应用场景

PLL技术在FPGA中的动态调频与展频功能应用

FPGA芯片的概念和结构

电容在时钟电路中的应用有哪些

Xilinx Ultrascale系列FPGA的时钟资源与架构解析

FPGA时序约束之设置时钟组

FPGA中的时钟相关概念

FPGA中的时钟相关概念

评论