最近不可描述的网站上有一个活动,很多人post了比较沧桑感的照片。"How it stared & How it is going"

在信息技术这个行业,因为有了摩尔定律的原动力,技术和商业的发展的确会有指数发展的机会。记得很多年前有个大佬说:“软件产品的优势就是复制的成本几乎为0,因此这个是软件相对于其他行业最大的竞争优势”。

但是最近的大佬会说:“因为软件的产品复制成本几乎0,这使软件成为了一个没有护城河的行业!”。没错,大家都接受了一个大项目开源之后,就会诞生了一系列的自主可控的国产软件的中国特色。

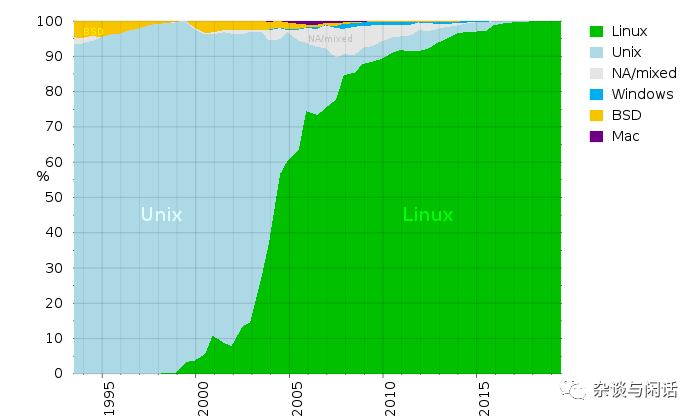

从最初的《集市和大教堂》开始,open source这个大旗的确是一呼百应,记得2010年的时候,云计算刚刚开始,微软就在担心windows 服务器版本的部署份额的下降,直到现在微软旗帜鲜明地支持Linux。这个是Top500操作系统的现状[1]。100% linux!!!

对于软件的开源,硬件公司,特别是家底比较厚的公司,也在发挥余热。最近被老黄收购ARM的消息淹没的IBM分拆其实也是一个时代的结束,并没有激起太多水花。

作为最近比较热门的自主可控的CPU的代表来讲,有MIPS,ARM,X86和Alpha 的ISA,但是作为现在唯一幸存的上一代的RISC的代表的open power就没有斩获一席之地。当然,一个技术方向的选择有很多因素,很多时候最先进的未必是最合适的。

这个就要回到上一篇的主题,hotchips一直就是芯片行业风向标。在整整10年之前,IBM也有一个session。[2]

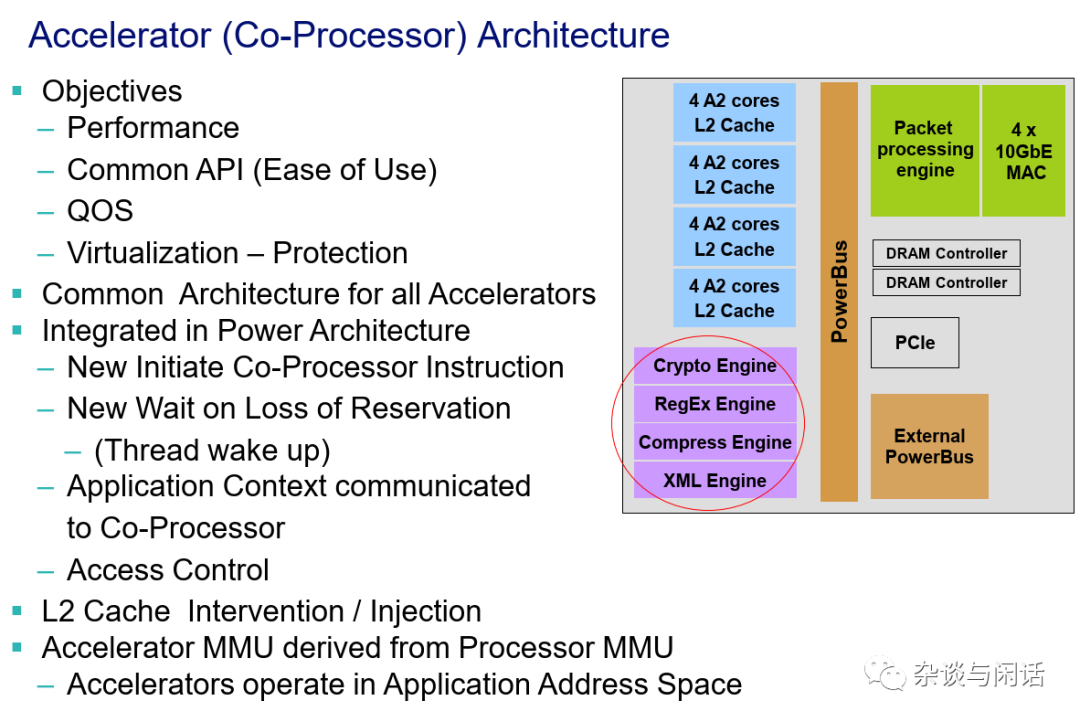

对!就是IBM在2010年左右所做的NP,或者说第二代的NP处理器。相对于第一代的NP,增加了更多的HW 加速功能。

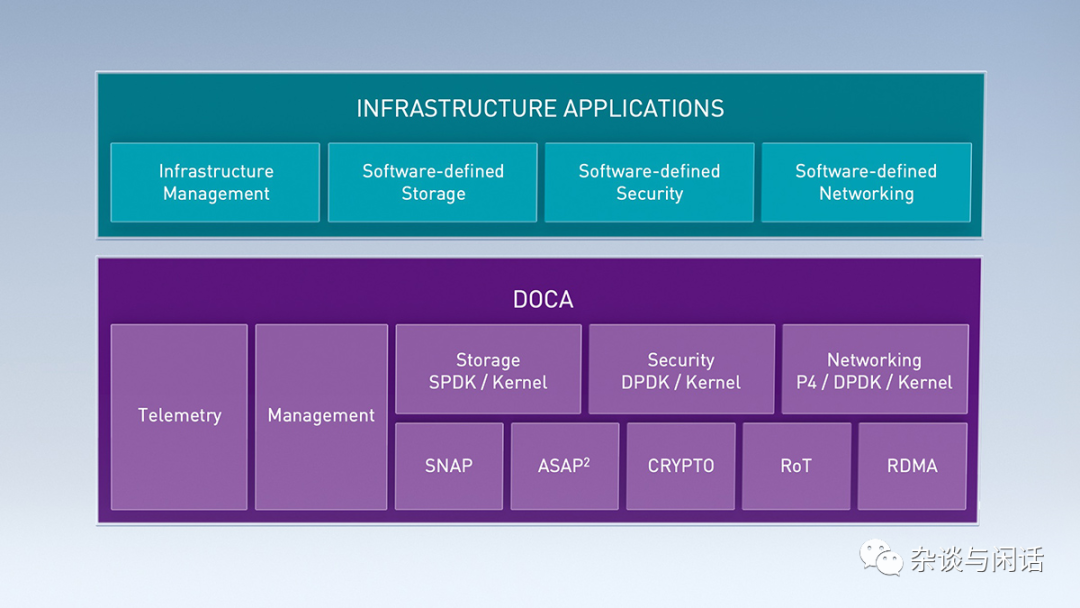

REG,compression, XML processing, cryptograghy, ethernet offload engine, 这些和老黄正在为那些互联网新贵的基础架构部门正在努力打造的DPU[3]类似。

IBM的45nm的工艺。400的片子,成本也不算低了。

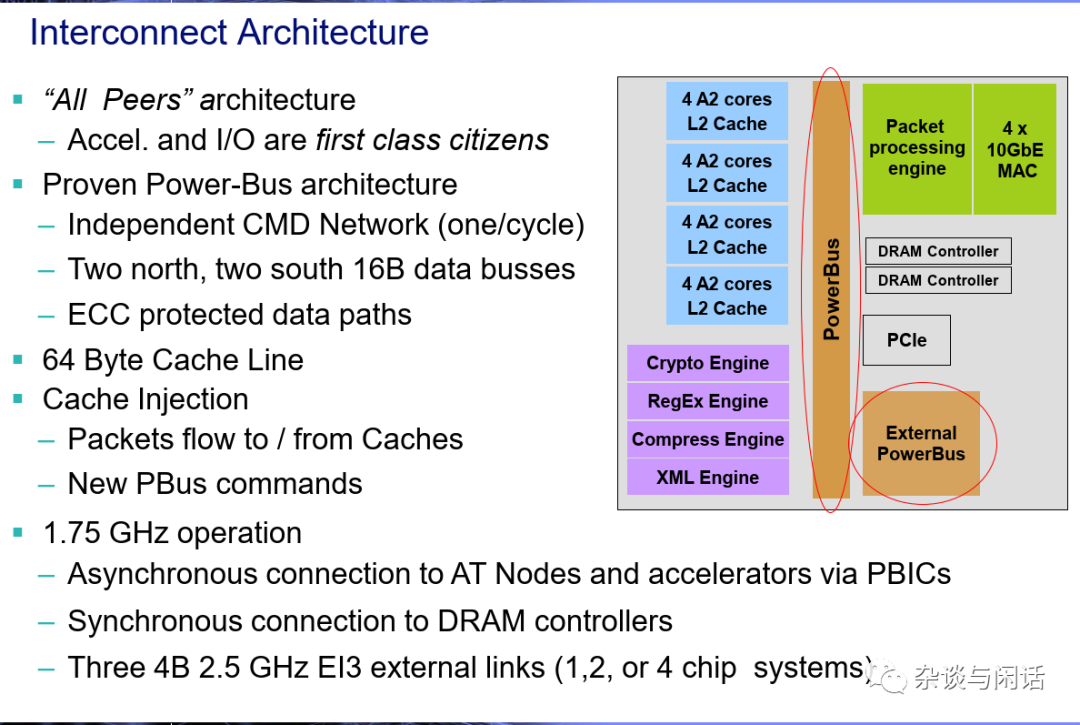

对于系统的互联,虽然不是上一期的NoC,但是PBus的功能定位也很清晰:

all peers 架构,也就是DDR连在系统的Front BUS上,这个是在AMD上次的复兴之前,MC和CPU都是分家,当然AMD这次又分家了。

两个南,北向的Data Bus,有点NoC的感觉。

Pakets flow可以直接到cache,这就是Intel DDIO, 估计现在的网卡都要这样了。

不同的A2 core的配置,不同的power domain,这样的片子功耗注定不会低了。16core的A2 估计至少50W之上了。

CPU Cluster和内存的连接,以及L1$和L2$都中规中矩。这里面的Line Locking和way locking不知道能不能用在新的CPU集成MC的架构中,理论上对于分离的MC和CPU架构更有用。

至于A2的core,我后面会讲,但是现在要看看每个功能模块先。不太明白这里虚拟化的作用。不过,想到RISC-V现在还不支持虚拟化,power的确是祖上有矿。

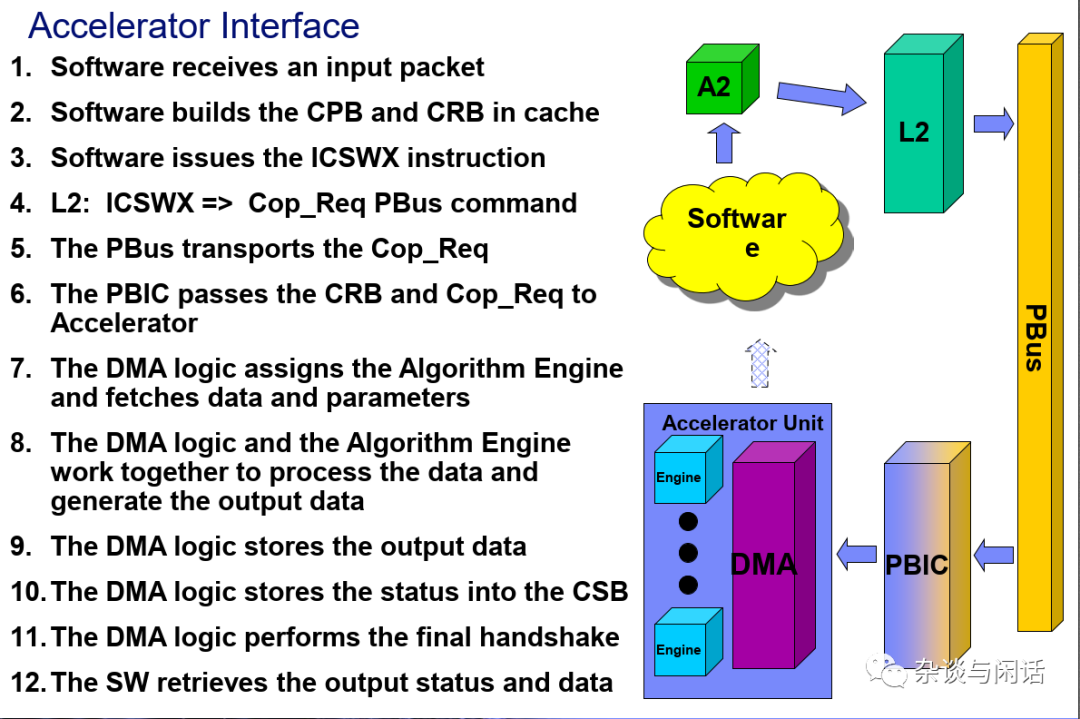

这个PBIC更像是加速单元的cache,这个思路的确是和Xilinx 的CCIX以及Intel的CXL一样。

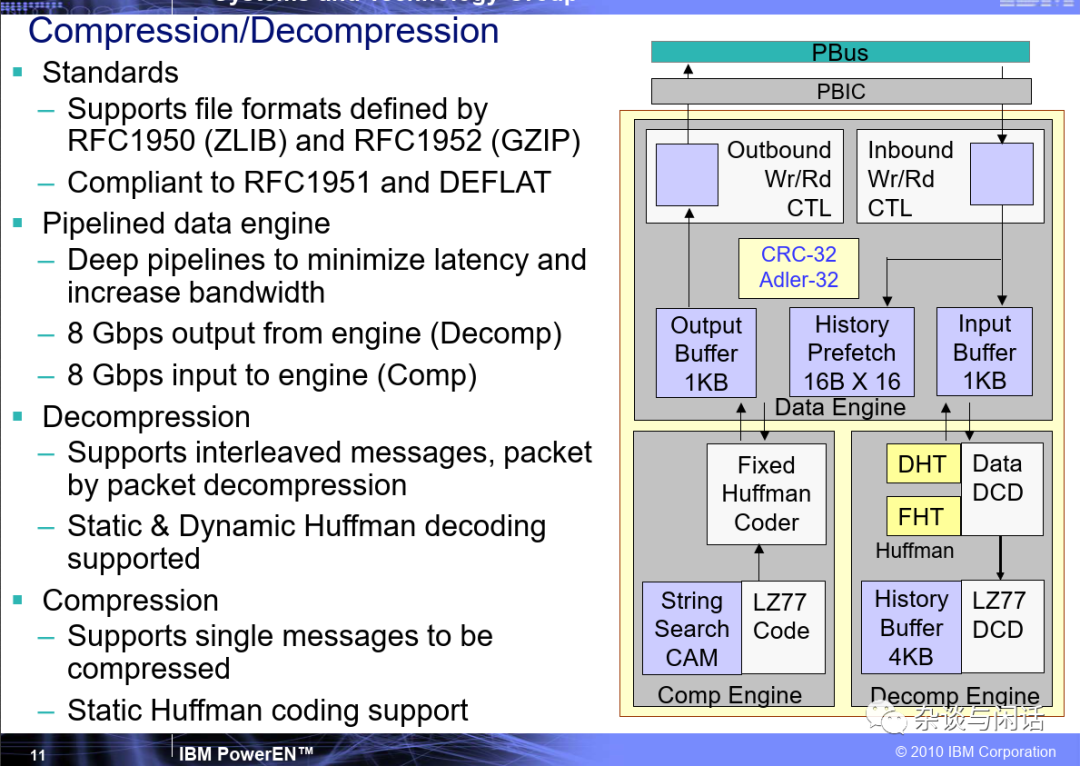

压缩

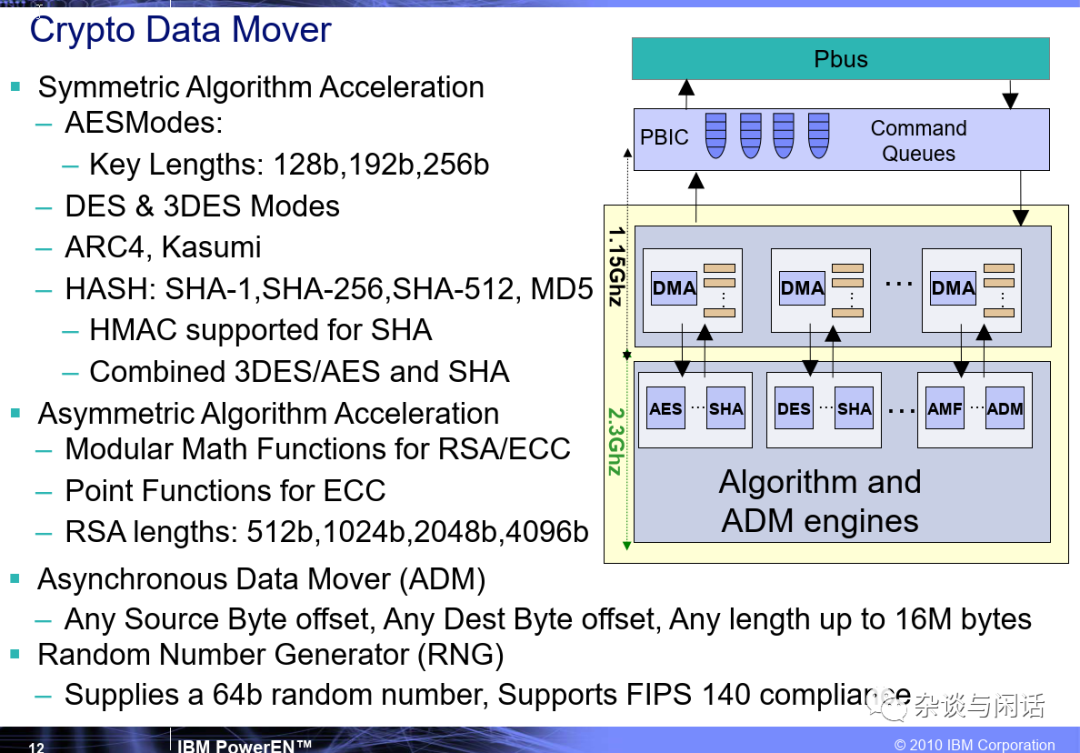

加密

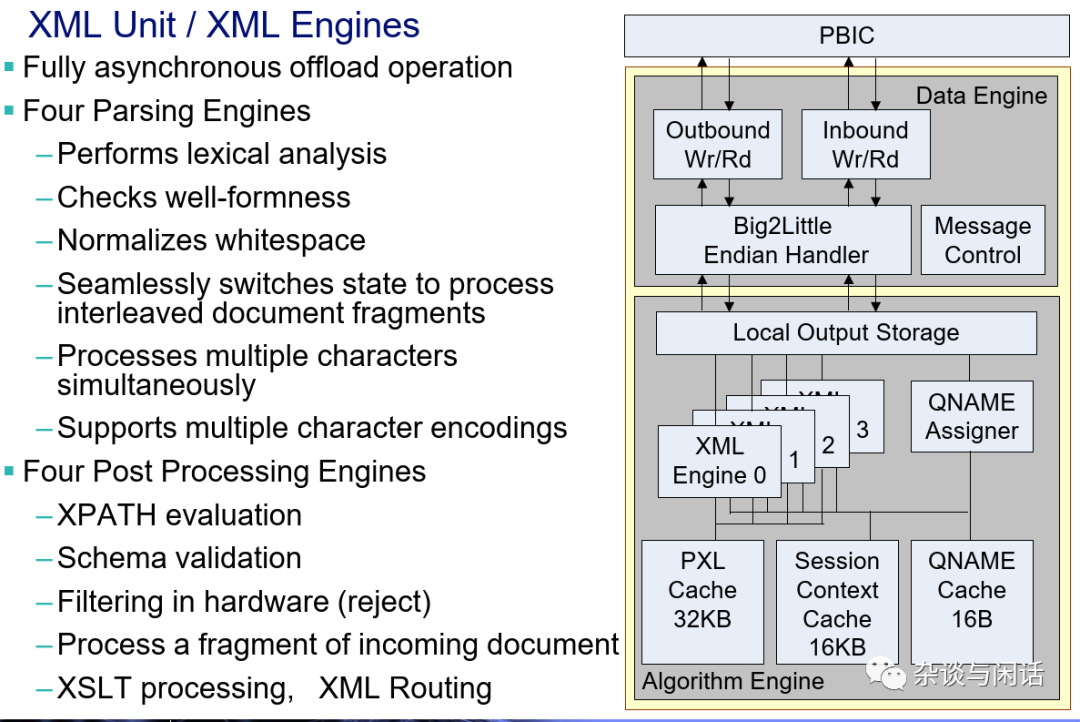

XML的处理,这个东西在现在也是内存数据厂家想要的东东。

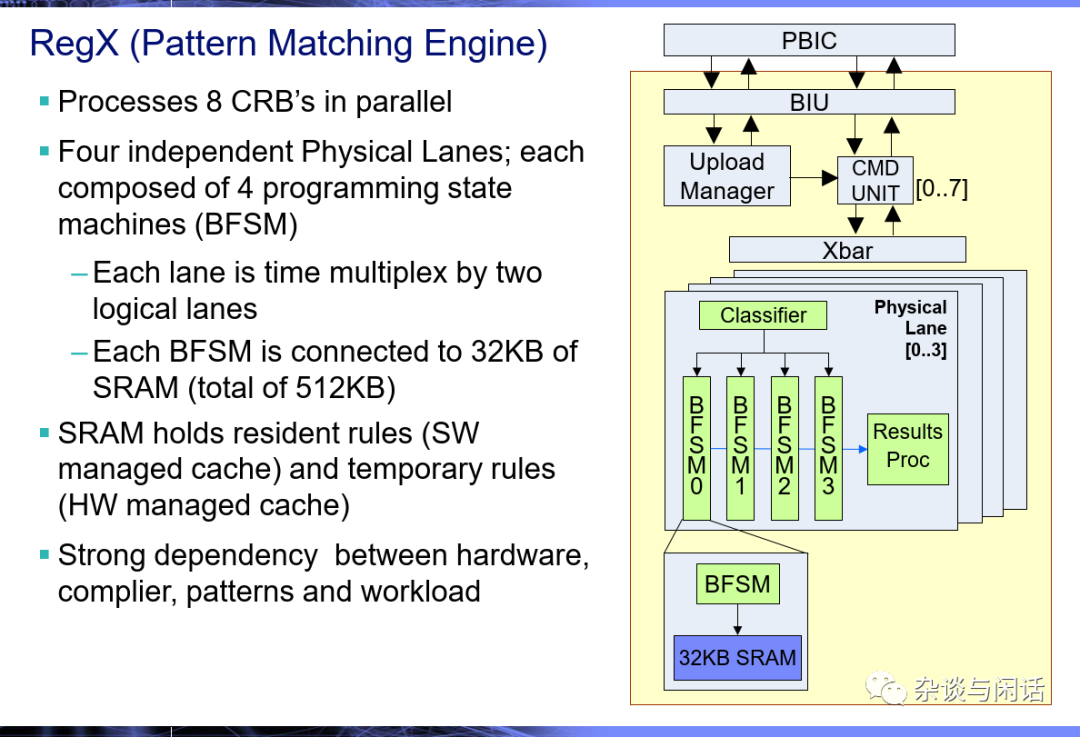

RegX

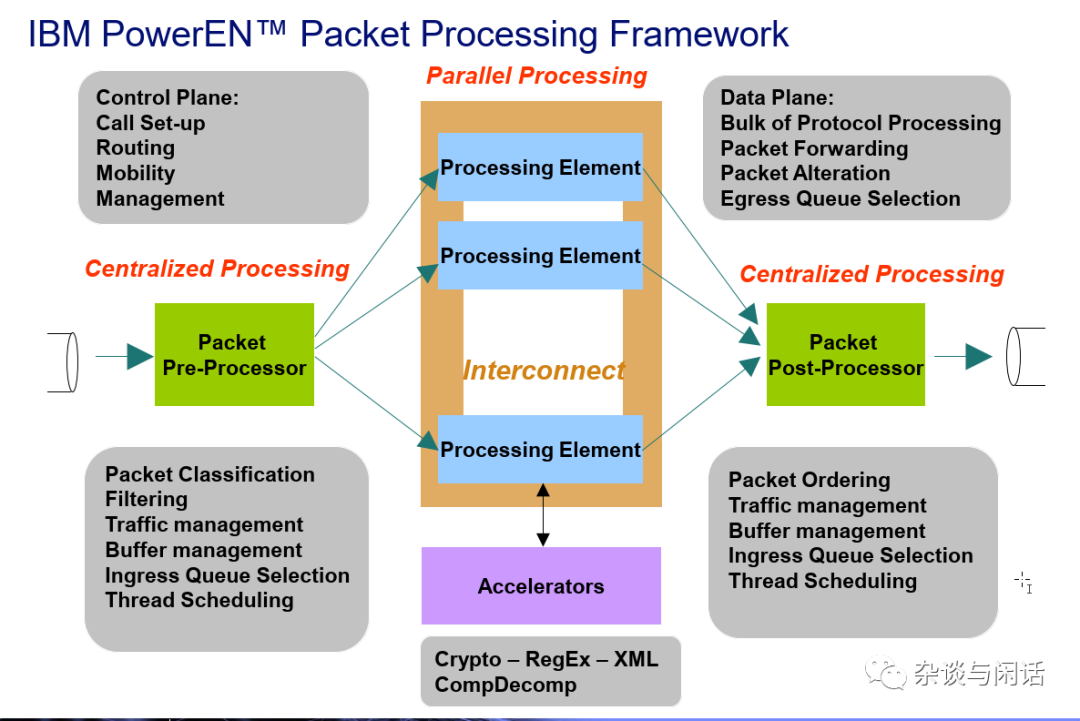

整个加速框架

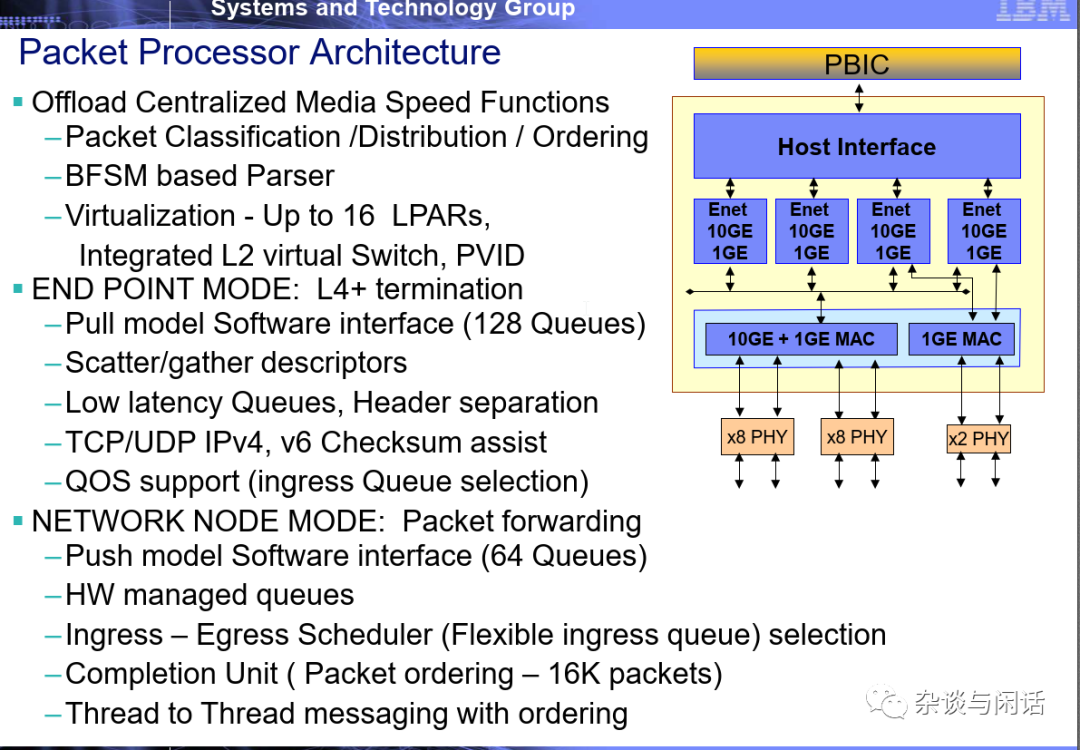

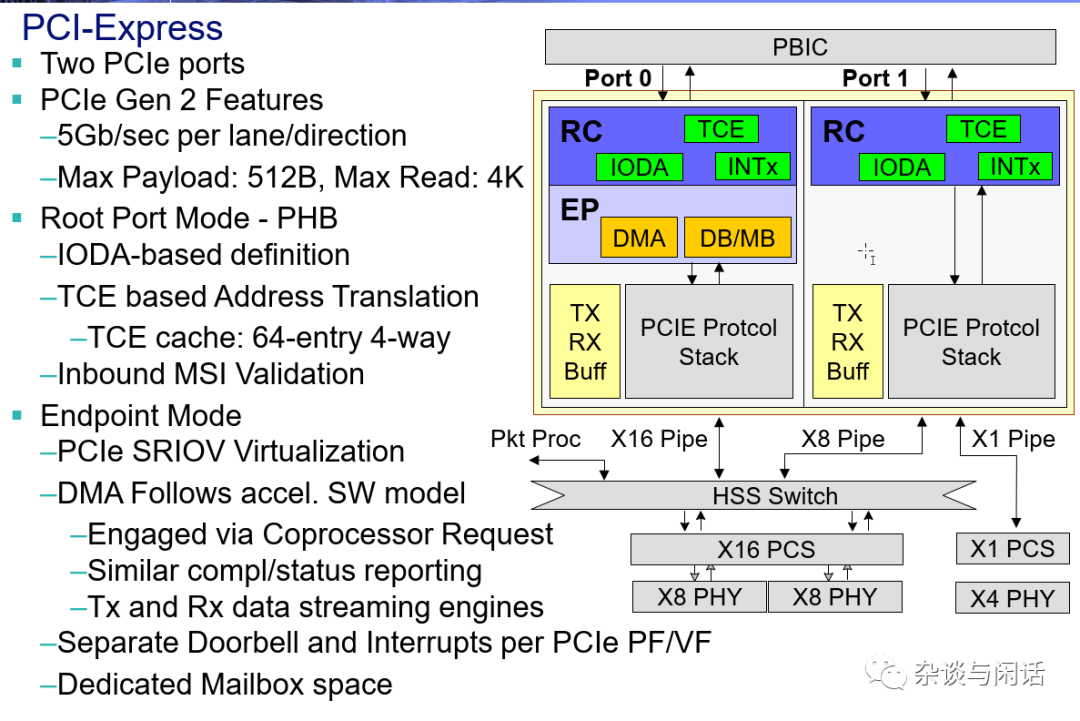

最后提了一下包处理和PCIE功能。相对来讲对于今天没有太大的参考意义了。网络也有一个虚拟的L2的switch,居然支持到L4,估计是为了做TCP的协议卸载。PCIE居然在2010年就支持了SRIOV,可惜了。可以支持Root port 和end port。

总体感觉IBM在10年前把除了虚拟化以外的workload都考虑到了。这些需求到现在还是有非常大的市场。不知道在片子正式量产的2013年发生了什么,IBM这个片子并没有像FSL,Nitro前身,凯威一样留下太多记忆。

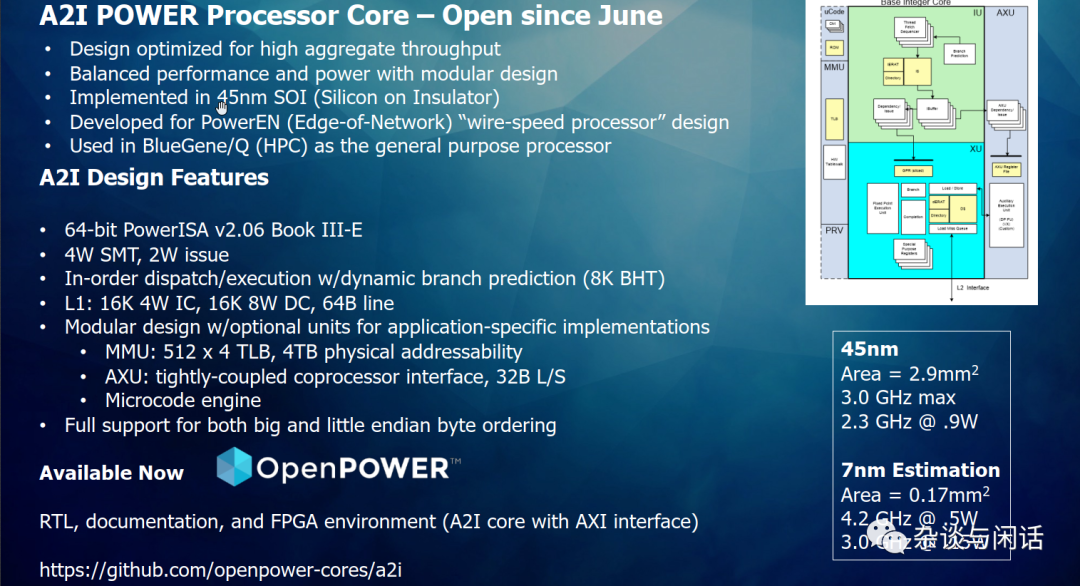

因此当IBM在2020年8月的openpower summit开源了A2的core时候,我才知道IBM曾经有这样一个东西。这个可能是一个介于SoC和NP之间的片子了。[4]

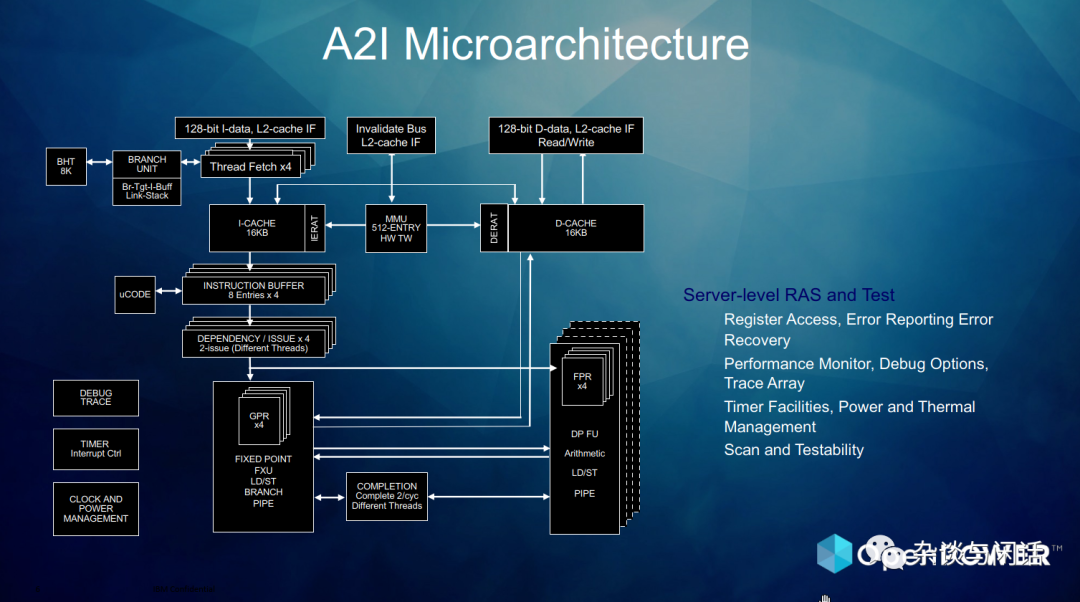

看架构,的确是一个非常成熟的CPU core,但是作为一个数据中心的网卡芯片,没有CPU是不够的,但是有CPU没有其他加速功能更是远远不够的。不知道IBM后续会不会把每个加速模块都开放出来。

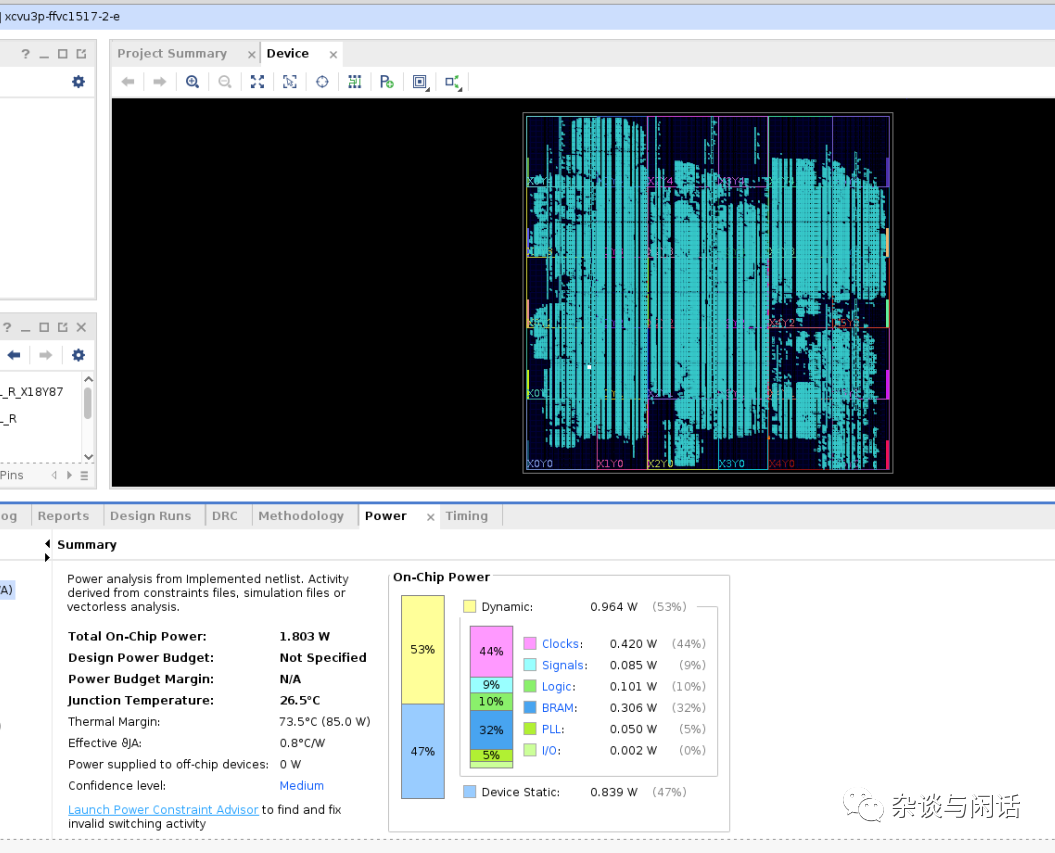

跑了一下工程,的确是大厂风范,一路都很顺利,而且是基于AXI的interface,基本可以直接连在AXI-IC上跑起来,但是没有对应的OS软件,而且也没有L2cache的clutser设置,感觉IBM可能后面还有。期待呀。

最后还要讲一下,这个片子可是IBM的蓝色基因的超算上的部件[5],但是主要是哪里呢?这个需要懂行的大侠指点一下。

责任编辑:lq

-

IBM

+关注

关注

3文章

1853浏览量

76784 -

云计算

+关注

关注

39文章

8003浏览量

143106 -

信息技术

+关注

关注

0文章

650浏览量

30964

原文标题:IBM也有DPU了?!

文章出处:【微信号:SSDFans,微信公众号:SSDFans】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

IBM与Anthropic达成战略合作

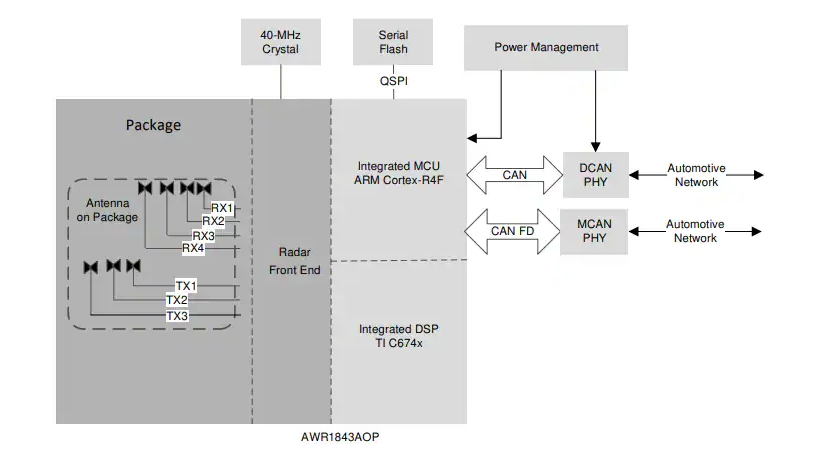

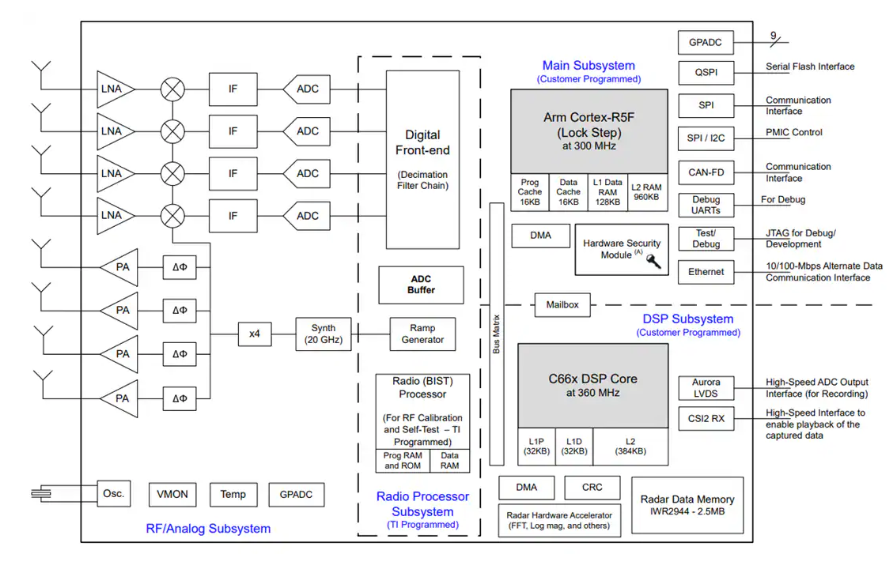

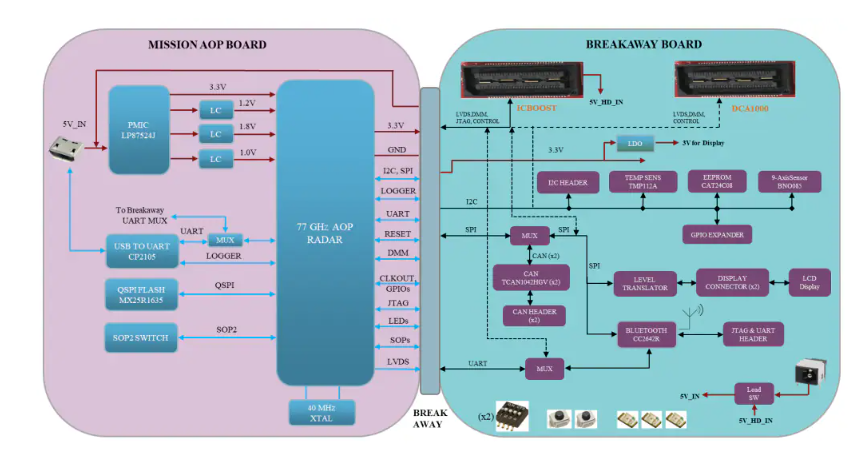

Texas Instruments AWR1843AOP汽车雷达传感器数据手册摘要

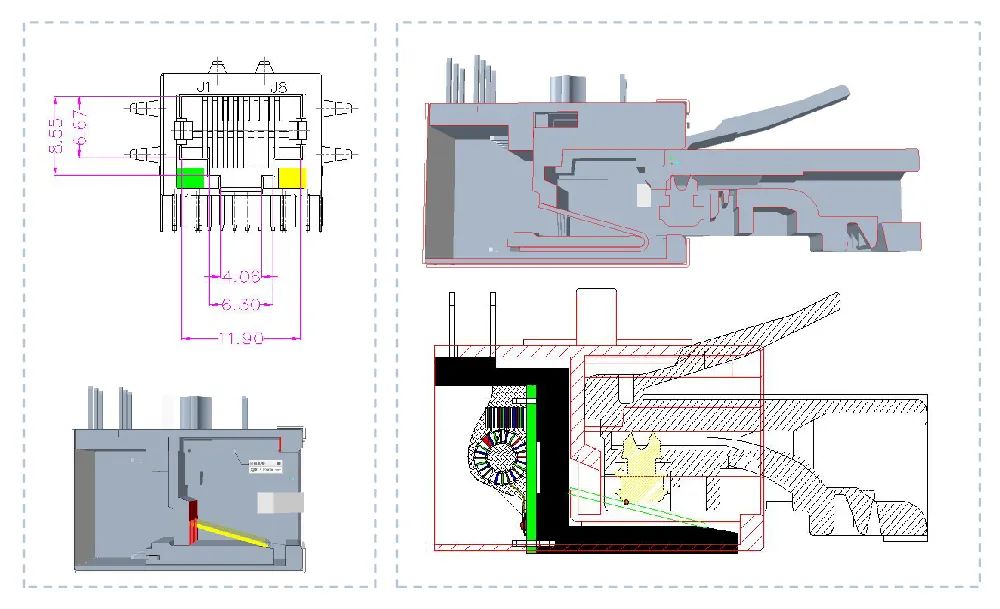

白光干涉仪在浸没式光刻后的3D轮廓测量

创飞芯40nm HV工艺OTP IP完成上架

Texas Instruments IWR2944毫米波雷达传感器数据手册

RJ45接口详解,如何使用?从生产工艺到设计原理参考

RJ45是什么?RJ45接口定义和类型介绍 一文掌握RJ45

IBM的45nm的工艺

IBM的45nm的工艺

评论