当信号被传输时,由于阻抗和其他影响,接收到的信号总是失真的。这就是为什么设计者致力于最小化对信号质量的影响。

设计者试图通过限制电子噪声、电感耦合、电容和线电阻改变信号形状和振幅的程度来实现信号的完整性。随着信号频率的增加,这些效应被放大,需要特别注意控制它们在电子电路中的不良影响。许多印刷电路板现在以10千兆赫或更高的数字信号频率工作,这意味着需要采取适当的措施来防止不可接受的信号退化及其相应的错误。

什么是PCB中的信号完整性?

信号完整性(SI)表示信号沿PCB线路传播而不失真的能力。信号完整性是指通过传输线的信号质量。当信号从驱动器传输到接收器时,它给出了信号衰减量的测量值。这个问题在较低的频率下不是主要的问题,但是当PCB以更高的速度和高频(>50MHz)工作时,这是一个需要考虑的重要因素。在高频区,数字和模拟信号都需要考虑。

当一个信号从驱动器传播到接收器时,它不会保持不变,不管最初发送的是什么,都会受到不同程度的失真。这种信号失真是由阻抗失配、反射、振铃、串扰、抖动和地面反弹等因素造成的。设计者的首要目标应该是最小化这些因素,这样原始信号就可以以最小的失真到达目的地。此外,还需要特别注意保持信号质量并控制其在电子电路中的不良影响。

在这里,我们将讨论潜在的信号完整性问题,它们的来源,理解它们的重要性,以及我们如何分析和解决这些问题。关于电气设计,信号完整性应该集中在两个主要方面:定时和信号质量。

信号是否在规定的时限内到达目的地?

当它到达目的地时,状况是否良好?

有几个因素导致信号退化。这些包括信号的特性、系统阻抗、传播延迟、衰减、串扰、电压波动和电磁干扰。

为什么保持信号完整性是一个挑战?

保持信号完整性是指确保系统内可接受的信号质量。

快速的技术进步使得系统开发者很难在接收端保持不失真的信号。带宽的增加是信号完整性的瓶颈。今天的电子产品需要更快的总线周期时间、增强信号处理时间(以纳秒为单位),甚至需要更快的上升时间。

电路板的空间要求也会影响信号的完整性。PCB仍然需要足够的空间来放置集成电路、连接器和无源元件。这个空间会导致部件之间的距离变大,从而导致延迟。我们都知道距离会降低整个系统的速度。当由上升时间小于4到6纳秒的信号驱动时,电路板迹线充当传输线。在低频下,一个迹线的电阻特性发挥作用。另一方面,在高频下,它开始充当电容器,电感。

什么因素导致信号完整性问题?

信号特性、系统阻抗、传输延迟、衰减、串扰、电压波动和电磁干扰等因素都会导致信号失真,从而导致信号完整性问题。

信号特性:理想情况下,数字信号是方波,但实际上,信号从一种状态切换到另一种状态需要一些时间。所以,这就是为什么,总是存在一定程度的信号失真。信号的上升时间决定了可能的最大数据传输速率,通常通过评估信号的拐点频率来测量。电路设计者的目标是实现一个电路在所有频率到信号拐点频率的平坦响应。

互连效应:理想的互连只会在信号中引入延迟,但实际上,它也会改变信号的timing和幅度。这种偏差分别称为抖动和振幅噪声。

阻抗:信号所看到的阻抗变化会引起反射、响铃和失真。随着与数字电路相关的信号频率的增加,干扰程度加剧。PCB跟踪分支、线头、连接器引脚和过孔都会产生阻抗不连续性。

传播延迟:传播距离不同或通过不同媒介的信号不会同时到达目的地。这些差异称为信号偏移,会导致信号采样误差,特别是在高时钟频率下。

衰减:信号的振幅会因PCB线路的电阻和电路板的介电损耗因子而降低。这种效应在高频下更为明显,因为信号往往在高频下沿迹线表面传播。衰减会导致缓慢的信号上升时间,并增加数据错误的可能性。

串扰:由于电感和电容耦合,快速的电压和电流转换会在相邻的线路上产生电压。这些电压尖峰被称为串扰,可能导致数据错误。

反射:反射是由终端和电路板布局问题引起的,其中输出信号反弹回源并干扰脉冲。

接地弹跳:由于电流过大,电路的接地参考电平从原来的水平偏移。这是由于接地电阻和互连电阻,如连接线和迹线,因此,接地中不同点的接地电压水平将不同。这被称为接地反弹,因为接地电压将随电流变化。

电源电压波动:当设备切换时,流动的电流会在电源和接地轨道上产生电压降。这反过来又会导致每个设备的电源电压波动,累积的影响会产生噪音并可能导致高误码率。

电磁干扰(EMI):每一次开关操作都会产生一定量的噪声,并且由于器件在时钟频率下进行开关,其强度会被放大。这种噪声可以被用作天线的迹线辐射。辐射信号的强度与开关频率成正比,并可能导致不必要的干扰。

责任编辑:tzh

-

pcb

+关注

关注

4391文章

23742浏览量

420710 -

驱动器

+关注

关注

54文章

9012浏览量

153328 -

emi

+关注

关注

54文章

3864浏览量

134088 -

数字电路

+关注

关注

193文章

1648浏览量

83029

发布评论请先 登录

三环电容ESL对高频信号完整性影响?

技术资讯 I 信号完整性与阻抗匹配的关系

深圳 9月12-13日《信号完整性--系统设计及案例分析》公开课,即将开课!

上海 6月20-21日《信号完整性--系统设计及案例分析》公开课,即将开课!

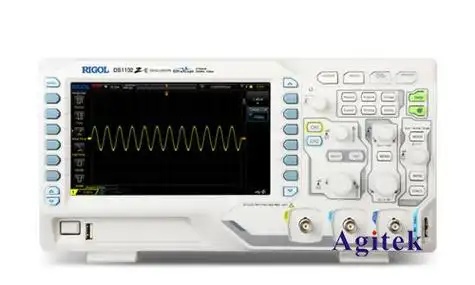

信号完整性测试基础知识

信号完整性优化:捷多邦的5大核心技术

普源示波器在信号完整性分析中的应用研究

什么因素导致信号完整性问题?

什么因素导致信号完整性问题?

评论