引言

“计算机组成原理”是计算机科学与工程技术类专业的一门核心课程,是学习计算机硬件系统的关键课程。本课程以计算机组成结构为中心阐述基本概念和原理,具体介绍了计算机硬件系统中各大部件的组成原理、逻辑实现、设计方法及互连构成整机的技术。提高该课程的实验教学水平,对于学生加深对课程的理解,培养学生设计能力和创新能力具有重要的意义。

随着电子技术的不断发展,数字系统的设计方法也在不断地进步,传统的手工设计过程已经被先进的EDA工具所替代。计算机作为一个典型的复杂数字系统,其设计方法发生了根本性的变革,因此应用EDA技术是计算机组成原理课程实验改革的方向。

目前高校开展本课程实验教学的方法有2种:一种方法是利用现有的计算机组成原理实验仪,该实验仪已将CPU的各个组成部件全部做好,学生只需按书中要求拨动相应开关就能完成实验,这种方法的缺点是不利于学生的理解,局限性较大,器件的品种、数量扩展困难,学生的设计难以突破实验箱的限制;另一种方法是应用EDA技术进行实验,利用软件生产商提供的ispDesign-EXPERT等软件工具进行模拟仿真,并通过可编程器件及相应硬件资源来直观地观察实验结果,加深对理论的理解。实践证明:基于EDA技术的实验教学,在巩固学生计算机组成原理课程理论的学习,熟悉CPU各个功能部件的工作情况,促进学生的感性认识,培养学生计算机应用能力和创新能力等方面起了积极的作用。

1、实施方案

计算机组成原理课程实践教学包含课程实验(18学时)和课程设计实验(一周)2个环节,其中课程实验主要验证计算机各部件组成和功能,课程设计实验主要完成计算机整机设计。课程实验内容包括:①运算器组成实验;②乘法器设计实验;③半导体存储器实验;④数据传送实验;⑤微程序控制器设计实验;⑥组合逻辑控制器实验;⑦并行接口实验;⑧程序中断实验。

课程设计为一个综合性的实验,实验内容是完成模型计算机的设计和EDA实现。课程设计的目标由简单到复杂分为4个阶段,学生可根据进展情况完成不同难度的设计。第1阶段完成基本模型机设计与实现;第2阶段增加移位控制指令,设计移位运算电路;第3阶段设计一个具有较完整指令系统的模型机,该模型机的指令系统包括算术逻辑指令、访存指令、转移控制指令、v0指令和停机指令,寻址方式包括立即寻址、直接寻址、间接寻址和相对寻址;第4阶段设计一个带接口的模型机,实现中断功能和访问并口、串口功能。

2、实验环境

本课程实验硬件环境为:PC一386以上微机、西安唐都科教仪器公司的TDN一CM++计算机组成原理实验台;软件环境为:WINDOWS操作系统、TDN一CM++计算机组成原理实验软件CMPP和ispDesigoMERT软件。PC机用于与实验台联机实时调试,利用实验软件提供图形调试功能,动态实时显示模型计算机各部件之间的数据传输以及各部件和总线上的所有信息。

本实验系统中使用的大规模可编程逻辑器件是Lattice公司的ispIS11032芯片。isp是指芯片具有“在系统可编程功能”,这种功能可随时对系统进行逻辑重构和修改。

对ispISI1032芯片的逻辑系统设计是通过使用硬件描述语言或原理图输人来实现的,硬件描述语言有ABEL,VHDL等多种语言。

实验系统中采用ispDesigaEXPERT软件来对可编程逻辑器件ispIS11032进行编程设计实现。ispDesignEXPERT可采用原理图或硬件描述语言或这2种方法的混合输人共3种方式来进行设计输人,并能对所设计的数字电子系统进行功能仿真和时序仿真,其编译器是软件所需要的熔丝图文件。该软件支持所有Lattice公司的ispLsI器件。

3、利用EDA技术进行实验的步骤

采用ispDesiglEXPERT软件来对可编程逻辑器件进行编程设计实现所需的数字系统功能一般要经过如下步骤。①建立新工程;②输人原理图或硬件描述语言进行设计;③对源程序进行编译;④连接下载电缆;⑤将生成的JED文件下载到可编程逻辑器件中;⑥连接实验电路;⑦在实验板上验证所设计系统的逻辑功能。

4、利用EDA技术进行阵列乘法器设计的实例

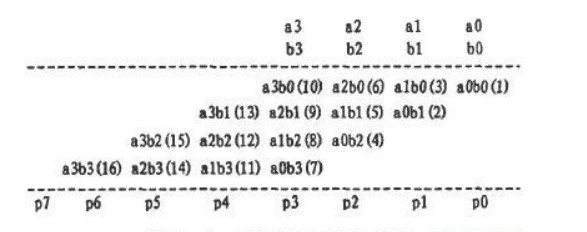

实验要求用ispIS11032芯片来实现一个4x4位乘法器。4x4位乘法器设计原理见图1。

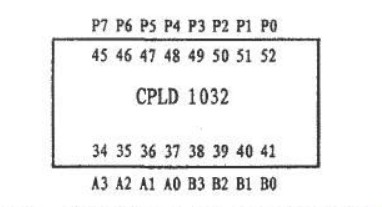

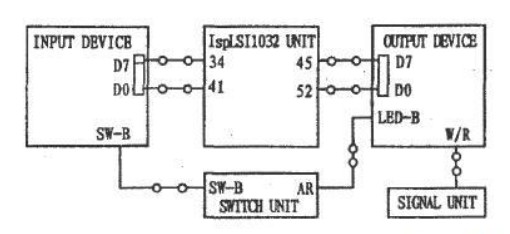

根据上述乘法的逻辑原理用ABEL语言编写功能描述程序。其在ispISI1032芯片中对应的管脚安排如图2所示,验证实验连线图如图3所示。

5、结束语

与以往传统的实验方法相比,学生在实验过程中可以把重点放在模型计算机的设计和仿真验,使本课程的实践教学环节更好地达到教学目的。软件设计调试阶段完成后的硬件下载和测试,又使学生能够学习硬件环境下的调试方法。实践表明,新的实验模式激发了学生学习的积极性,加深了对本课程的掌握程度,同时还能够学到先进的设计技术,学生普遍欢迎这种改革。新的实验模式有效地锻炼了学生的设计能力和实践能力,为学生提供了充分的创造空间,收到了传统实验方法难以获得的效果。

责任编辑:tzh

-

芯片

+关注

关注

463文章

54412浏览量

469193 -

计算机

+关注

关注

19文章

7839浏览量

93459 -

eda

+关注

关注

72文章

3143浏览量

183723

发布评论请先 登录

利用EDA技术进行阵列乘法器设计的实例

利用EDA技术进行阵列乘法器设计的实例

评论