CDCF5801A:时钟乘法器的卓越之选

在电子工程师的日常设计工作中,时钟信号的处理至关重要,而时钟乘法器则是实现精确时钟信号的关键组件。今天,我们就来深入探讨德州仪器(Texas Instruments)推出的CDCF5801A时钟乘法器,看看它在时钟处理方面的独特魅力。

文件下载:cdcf5801a.pdf

一、产品概述

CDCF5801A是一款具备延迟控制和相位对齐功能的时钟乘法器,它能将参考时钟(REFCLK)信号进行乘法运算,同时还能对CLKOUT/CLKOUTB信号进行精确的延迟或提前操作,步长仅为1.3 mUI。这种独特的功能使得它在众多应用场景中都能发挥出色的性能。

二、产品特性

1. 低抖动时钟乘法

CDCF5801A支持×1、×2、×4、×8的时钟乘法,能够在输入频率范围为12.5 MHz至240 MHz的情况下,输出25 MHz至280 MHz的稳定时钟信号,并且具有低抖动特性,确保了时钟信号的高质量。

2. 故障安全上电初始化

该器件具备故障安全上电初始化状态机,能在各种上电条件下保证正常运行,为系统的稳定性提供了有力保障。

3. 可编程双向延迟

通过DLYCTRL和LEADLAG引脚,CDCF5801A可以实现可编程的双向延迟,延迟步长为1.3 mUI,这使得它能够灵活地进行相位对齐,满足不同应用的需求。

4. 多种输出驱动能力

它支持单端和差分输出,输出能够驱动LVPECL、LVDS和LVTTL等不同类型的负载,具有很强的通用性。

5. 低功耗设计

CDCF5801A采用了三种功率操作模式,能够有效降低功耗,在280 MHz/3.3 V的工作条件下,功耗小于190 mW。

6. 无需外部组件

PLL部分无需外部组件,简化了设计,降低了成本和电路板空间。

7. 扩频时钟跟踪能力

具备扩频时钟跟踪能力(SSC),可以有效降低电磁干扰(EMI)。

三、引脚功能

CDCF5801A共有24个引脚,每个引脚都有其特定的功能:

1. 时钟输出引脚

CLKOUT和CLKOUTB是低噪声CMOS输出引脚,用于输出时钟信号。

2. 延迟控制引脚

DLYCTRL引脚的每个上升沿可以使CLKOUT/CLKOUTB信号延迟或提前1/768个CLKOUT/CLKOUTB周期(1.3 mUI)。

3. 电源和地引脚

包括VDDREF、VDDP、VDDO、VDDPD、VDDPA等电源引脚,以及GND、GNDO、GNDP、GNDPA等地引脚,为器件提供稳定的电源和接地。

4. 控制引脚

LEADLAG引脚用于控制输出时钟相对于REFCLK的延迟或提前;MULT[0:1]和P[0:2]引脚用于选择频率乘法和除法比率;P0、STOPB和PWRDN引脚用于选择不同的功率模式。

四、频率设置

通过设置MULT[0:1]和P[1:2]引脚,可以选择不同的频率乘法和除法比率,从而实现从25 MHz到280 MHz的输出频率。具体的设置可以参考文档中的表1,需要注意的是,在输入频率范围有重叠的情况下,应选择表格中更靠近顶部的输入频率范围,以确保设备的最佳运行。

五、功率模式

CDCF5801A提供了多种功率模式,通过PWRDNB和STOPB引脚进行选择:

1. 掉电模式

当PWRDNB为低电平时,器件进入掉电模式,CLKOUT/CLKOUTB输出低电平。

2. 时钟停止模式

当STOPB为低电平时,输出被禁用,PLL和PA仍在运行,CLKOUT和CLKOUTB输出一个直流值。

3. 正常模式

当PWRDNB和STOPB都为高电平时,器件正常工作,输出频率根据MULT[0:1]和P[0:2]的设置而定。

六、应用场景

1. 视频图形和游戏产品

在这些应用中,需要精确的时钟信号来确保图像和游戏的流畅运行,CDCF5801A的低抖动特性和相位对齐功能能够满足这些需求。

2. 数据通信和电信

在数据传输和通信系统中,稳定的时钟信号是保证数据准确传输的关键,CDCF5801A可以提供高质量的时钟信号,提高系统的可靠性。

3. FPGA噪声消除

FPGA在工作过程中会产生噪声,CDCF5801A可以通过相位对齐和延迟控制,有效消除FPGA产生的噪声,提高系统的性能。

七、使用注意事项

1. VDDREF的选择

VDDREF可以设置在1.2 V至VDD之间的任何值,它直接影响输入的触发电压。在使用小信号摆幅驱动输入时,如PECL,建议将VDDREF直接连接到VDD,并对REFCLK输入进行交流耦合和重新偏置。

2. 反馈回路

如果在CDCF5801A的CLKOUT到DLYCTRL反馈回路中使用了有源元件(如微控制器、ASIC、DSP等),请参考应用报告SCAA075。

八、总结

CDCF5801A作为一款功能强大的时钟乘法器,具有低抖动、可编程延迟、多种输出驱动能力和低功耗等优点,适用于多种应用场景。在设计过程中,工程师们可以根据具体需求合理设置引脚和参数,充分发挥其性能优势。你在实际使用中是否遇到过类似的时钟乘法器?它们的表现如何呢?欢迎在评论区分享你的经验和见解。

-

低抖动

+关注

关注

0文章

76浏览量

6124

发布评论请先 登录

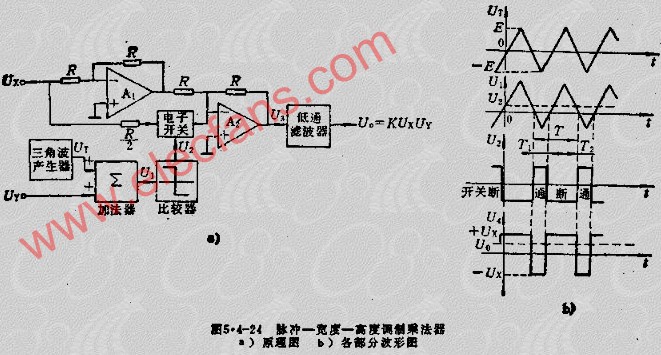

脉冲-宽度-高度调制乘法器

进位保留Barrett模乘法器设计

使用verilogHDL实现乘法器

乘法器原理_乘法器的作用

CDCF5801A具有延迟控制和相位对准的时钟乘法器数据表

CDCF5801A时钟乘法器技术文档总结

CDCF5801A:时钟乘法器的卓越之选

CDCF5801A:时钟乘法器的卓越之选

评论