CDCVF25084:高性能时钟乘法器的深度剖析

在电子设计领域,时钟信号的处理至关重要,它直接影响着整个系统的稳定性和性能。今天,我们就来深入探讨德州仪器(Texas Instruments)的CDCVF25084——一款3.3 - V 1:8零延迟(PLL)x4时钟乘法器。

文件下载:cdcvf25084.pdf

1. 产品概述

CDCVF25084是一款高性能、低偏斜、低抖动的锁相环(PLL)时钟乘法器。它利用PLL技术,能精确地将输出时钟的频率和相位与输入时钟信号对齐,并且具有四倍的乘法因子。该器件的标称电源电压为3.3 V,适用于多种电子设备的时钟分配应用。

由于文档搜索出现问题,暂时未能获取到CDCVF25084时钟乘法器应用场景的相关内容。不过我们可以结合其特性推测,它可能广泛应用于通信设备、数据处理系统、工业控制等对时钟信号要求较高的领域。

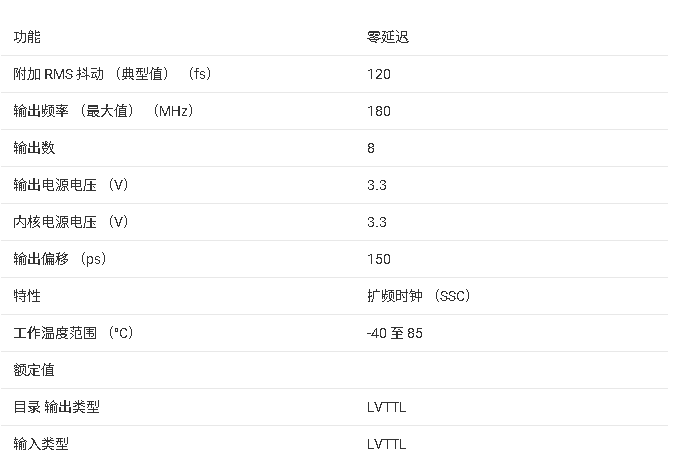

2. 关键特性

2.1 频率范围

输入频率范围为2.5 MHz至45 MHz,输出频率范围为10 MHz至180 MHz,能够满足多种不同频率需求的应用场景。

2.2 兼容性

与LVCMOS/LVTTL I/O兼容,方便与其他数字电路进行接口。

2.3 低抖动

在75 MHz至180 MHz的范围内,周期到周期的抖动低至±120 ps,确保了时钟信号的稳定性和准确性。

2.4 输出配置

将一个时钟输入分配到两组四个输出,每组输出都能提供低偏斜、低抖动的CLKIN x 4的副本,并且所有输出工作在相同频率,输出占空比自动调整为50%,不受CLKIN占空比的影响。

2.5 自动频率检测

具备自动频率检测功能,当CLKIN没有输入信号时,设备自动进入掉电模式,输出呈低电平状态,有助于降低功耗。

2.6 集成设计

采用单3.3 - V电源供电,工业温度范围为–40°C至85°C,内部集成了25 - Ω的片上串联阻尼电阻,无需外部RC网络,减少了外部元件数量,降低了成本和电路板空间。

2.7 频谱兼容性

与扩频时钟(SSC)兼容,可有效减少电磁干扰。

3. 功能模式

| 通过S1和S2两个选择引脚,可以确定设备的工作模式,具体如下表所示: | S2 | S1 | 1Y0–1Y3 | 2Y0–2Y3 | OUTPUT SOURCE | PLL SHUTDOWN |

|---|---|---|---|---|---|---|

| 0 | 0 | Hi - Z | Hi - Z | N/A | Yes | |

| 0 | 1 | Active | Hi - Z | PLL † | No | |

| 1 | 0 | Active | Active | Input clock (PLL bypass) | Yes | |

| 1 | 1 | Active | Active | PLL † | No |

需要注意的是,当CLK输入频率 < 2 MHz时,输出会切换到低电平。

4. 引脚功能

4.1 输出引脚

- 1Y[0:3]:第一组时钟输出,是CLKIN的低偏斜副本,每个输出都集成了25 - Ω的串联阻尼电阻。

- 2Y[0:3]:第二组时钟输出,同样是CLKIN的低偏斜副本,每个输出也集成了25 - Ω的串联阻尼电阻。

4.2 输入引脚

- CLKIN:时钟输入,为CDCVF25084时钟驱动器提供要分配的时钟信号,同时为集成的PLL提供参考信号。CLKIN必须具有固定的频率和相位,以便PLL能够锁定。

- FBIN:反馈输入,为内部PLL提供反馈信号,必须连接到其中一个输出以完成内部PLL的反馈回路,使输入时钟到输出时钟的延迟标称值为零。

4.3 控制引脚

- S1, S2:选择引脚,用于确定设备的工作模式。

4.4 电源和接地引脚

- VDD:电源电压,范围为3 V至3.6 V。

- GND:接地引脚。

5. 电气特性

5.1 绝对最大额定值

在使用过程中,需要注意以下绝对最大额定值,超出这些范围可能会对设备造成永久性损坏:

- 电源电压范围:–0.5 V至4.6 V

- 输入电压范围:–0.5 V至4.6 V

- 输出电压范围:0.5 V至VDD + 0.5 V

- 输入钳位电流:–50 mA

- 输出钳位电流:–50 mA

- 连续总输出电流:±50 mA

- 封装热阻:PW封装为147°C/W

- 存储温度范围:–65°C至150°C

5.2 推荐工作条件

| 为了确保设备的正常工作,建议在以下条件下使用: | 参数 | 最小值 | 标称值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| 电源电压(VDD) | 3 | 3.3 | 3.6 | V | |

| 低电平输入电压(VIL) | 0.8 | V | |||

| 高电平输入电压(VIH) | 2 | V | |||

| 输入电压(VI) | 0 | 3.6 | V | ||

| 高电平输出电流(IOH) | -12 | mA | |||

| 低电平输出电流(IOL) | 12 | mA | |||

| 工作环境温度(TA) | -40 | 85 | °C |

5.3 电气参数

文档中还给出了一系列电气参数,如输入电压、输入电流、功耗电流、动态电流、输出三态电流、输入电容、输出电容等,这些参数对于电路设计和性能评估非常重要。

6. 开关特性

6.1 PLL锁定时间

当输出频率为100 MHz时,PLL锁定时间为2 µs。

6.2 相位偏移

在不同的输出频率范围内,CLKIN到FBIN的相位偏移有所不同,如在75 MHz至180 MHz范围内,相位偏移为±100 ps。

6.3 传播延迟

在PLL旁路模式下,传播延迟为2.3至4.5 ns。

6.4 输出偏斜

输出之间的偏斜(Yn到Yn)在一定条件下有相应的规格,如在PLL旁路模式下为900 ps,在PLL模式下,不同频率范围的偏斜也有所不同。

6.5 抖动

包括周期到周期抖动、周期抖动和相位抖动等,在不同频率范围内有不同的抖动指标,如在75 MHz至180 MHz范围内,周期到周期抖动为±120 ps。

7. 封装与布局

CDCVF25084采用16引脚的TSSOP封装,文档中还提供了详细的封装信息、引脚排列图、示例电路板布局和示例模板设计等,为工程师的实际应用提供了便利。

8. 总结

CDCVF25084时钟乘法器以其高性能、低抖动、集成度高和多种功能模式等特点,为电子工程师在时钟信号处理方面提供了一个优秀的解决方案。在实际设计中,工程师需要根据具体的应用需求,合理选择工作模式和配置参数,确保设备在最佳状态下运行。同时,要严格遵守绝对最大额定值和推荐工作条件,以保证设备的可靠性和稳定性。

大家在使用CDCVF25084的过程中,有没有遇到过什么问题或者有什么独特的应用经验呢?欢迎在评论区分享交流。

-

电子设计

+关注

关注

42文章

2867浏览量

49916

发布评论请先 登录

关于E203内核高性能乘法器优化(一)

模拟乘法器AD834的原理与应用

使用verilogHDL实现乘法器

乘法器原理_乘法器的作用

CDCVF25084 3.3V 1:8零延迟(PLL)x4时钟乘法器技术文档总结

CDCVF25084:高性能时钟乘法器的深度剖析

CDCVF25084:高性能时钟乘法器的深度剖析

评论