来源:半导体行业观察

位于加利福尼亚州弗里蒙特的MRAM初创公司Spin Memory表示,它已经开发出一种晶体管,可以大大缩小MRAM和电阻性RAM的尺寸。据该公司称,该设备还可以克服DRAM中一个名为Row Hammer的顽固安全漏洞。

Spin Memory的垂直环绕栅晶体管可以缩小MRAM和RRAM存储单元。

Spin Memory将设备称为“通用选择器”(Universal Selector)。在存储器单元中,选择器是用于访问所述存储器元件——MRAM中的一个磁隧道结。也是RRAM的一种电阻材料RRAM,也就是DRAM的电容器。这些通常内置于硅的主体中,而存储元件则构造在其上方。使选择器更小并简化与选择器接触的互连的布局,可以使存储单元更紧凑。

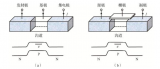

一般而言,晶体管是在硅平面的水平上构建的。当设备开启时,电流流过源极和漏极之间的沟道区域。通用选择器使该几何体倾斜90度。源极在底部与埋在硅中的导体相连,沟道区域是垂直的硅柱,漏极在顶部。栅极是器件中控制电荷流动的部分,四周围绕着沟道区离子。

“通用选择器”就像普通的晶体管一样,但是倾斜了90度。存储元件(通常为MRAM)连接到设备上方的漏极。

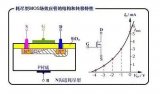

这种垂直的gate-all-around 器件类似于用于制造当今的多层NAND闪存存储芯片的器件。但是Spin Memory的设备仅跨越一层,并且被调整为在低得多的电压下运行。

据该公司称,这种垂直设备将使DRAM阵列密度提高20%至35%,并使制造商可以在同一区域内将多达MRAM或RRAM存储器的容量提高五倍。

选择器是Spin Memory正在开发的三项发明中的一部分,以促进MRAM的采用。另外两个是改进的磁隧道结,以及一种电路设计,这些都可以提高MRAM的耐用性和读写速度,并消除错误源。该公司产品开发高级副总裁Jeff Lewis表示,这种结合将使MRAM的性能达到与SRAM(当今CPU和其他处理器中嵌入的超快存储器)相当的水平。

使用“通用选择器”可以实现更紧凑的存储单元设计。

Lewis说:“由于其已知的猥琐问题,将SRAM用作主要的片上存储器正成为问题。” 由于MRAM只是一个晶体管和一个磁性隧道结,因此有一天可以比由六个晶体管组成的SRAM具有更高的密度优势。更重要的是,与SRAM不同,即使在存储单元没有电源的情况下,MRAM也会保留其数据。但是,目前,MRAM单元比SRAM大得多。“我们的主要目标之一是为MRAM设计一个较小的单元,以使其作为SRAM替代品具有更大的吸引力。”

有了DRAM(计算机选择的主要内存),通用选择器具有一个有趣的副作用:它应使内存不受 Row Hammer的影响。当一行DRAM单元快速充电和放电时,会发生此漏洞。(基本上,以极高的速率翻转位。)此操作产生的杂散电荷可以迁移到相邻的单元格行,从而破坏该位的位。

Row Hammer是DRAM可靠性和安全性的主要问题之一,长期以来一直困扰着存储器行业。作为DRAM长期以来的主要干扰问题,随着单元的缩小, Row Hammer.只会成为一个更大的问题,” 思科系统公司设备可靠性专家Charles Slayman说。

而据刘易斯称,由于晶体管通道位于硅主体之外,因此该新器件不受此问题的影响,因此它与漂移电荷隔离。他说:“这是排除Row Hammer的根本原因。”

为了在DRAM中使用,可能必须将设备缩小很多。但是改善MRAM是近期目标。这将涉及优化驱动电流和设备其他方面的强度。

来源:半导体行业观察

原文标题:热点 | 取代SRAM,MRAM又走近了一步!

文章出处:【微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

-

sram

+关注

关注

6文章

833浏览量

117727 -

晶体管

+关注

关注

78文章

10440浏览量

148610 -

MRAM

+关注

关注

1文章

254浏览量

32985

原文标题:热点 | 取代SRAM,MRAM又走近了一步!

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

同步DRAM相比传统异步DRAM有哪些特点

揭秘芯片测试:如何验证数十亿个晶体管

CGH40006P射频晶体管

电压选择晶体管应用电路第二期

晶体管的基本结构和发展历程

0.45-6.0 GHz 低噪声晶体管 skyworksinc

多值电场型电压选择晶体管结构

半导体存储芯片核心解析

晶体管光耦的工作原理

垂直环绕栅晶体管可缩小MRAM和RRAM存储单元!

垂直环绕栅晶体管可缩小MRAM和RRAM存储单元!

评论