本篇博文主要讲解了动态更改 UltraScale/UltraScale+ GTH/GTY 收发器线速率设置的方法。

您是否曾想过要使用 UltraScale/UltraScale+ GTH/GTY 收发器来动态更改线速率设置?

有许多客户会将 GTH/GTY 收发器用于其自己的通信协议,因此询问我们如何才能使用收发器来更改线速率。

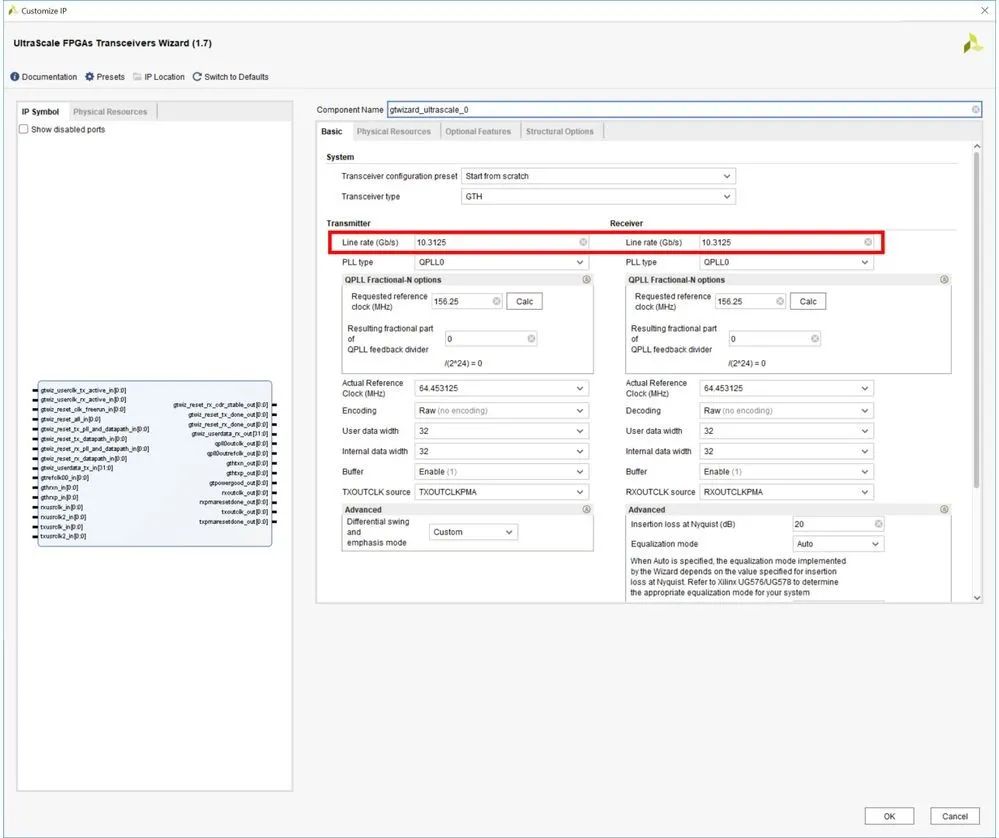

在 Vivado IP Catalog 的 UltraScale FPGAs TransceiversWizard 中仅含一项线速率设置。

由于 UltraScale/UltraScale+ GTH/GTYTransceiver Wizard 不允许更改线速率设置,因此必须由收发器用户手动执行更改。

1.如何通过 DRP 接口更改线速率

(a) 生成收发器 IP

使用要实现的线速率配置生成收发器 IP。

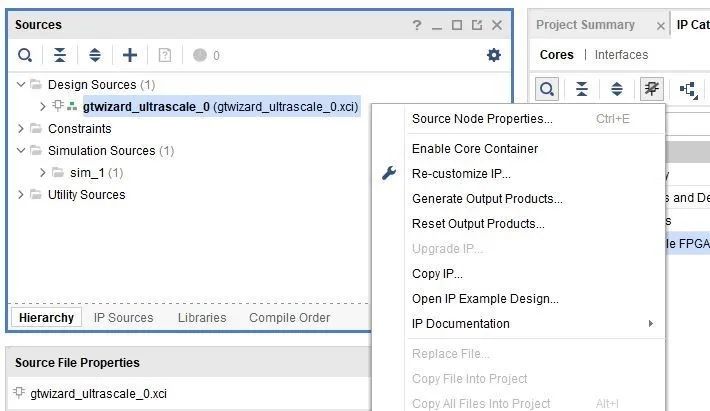

(b) 生成设计样本

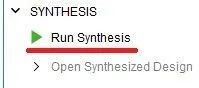

(c) 对设计样本执行逻辑综合

单击 Flow Navigator 中的“运行综合 (Run Synthesis)”:

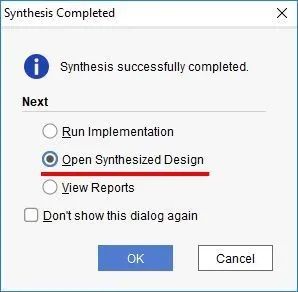

综合完成后,选择“打开已综合的设计 (Open Synthesized Design)”以打开网表。

(d) 运行随附的脚本

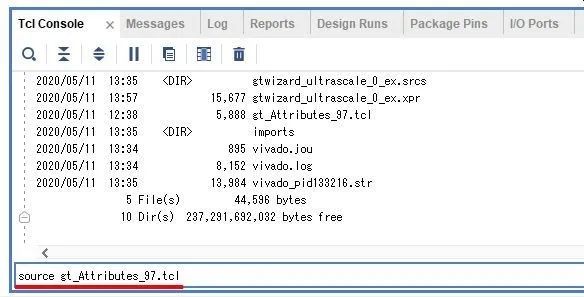

在 Tcl 控制台 (Tcl console) 中运行gt_Attributes_97.tcl脚本:

执行此脚本即可将“Channel/Common”属性输出到gtParams.txt文件。

并且,GTH/GTY 中的属性和修复后的 GTH/GTY 端口也都将包含在同一个文件中输出,以便于您进行比较。

针对要实现的每项 GTH/GTY 配置重复上述步骤 (a) 到 (d)。

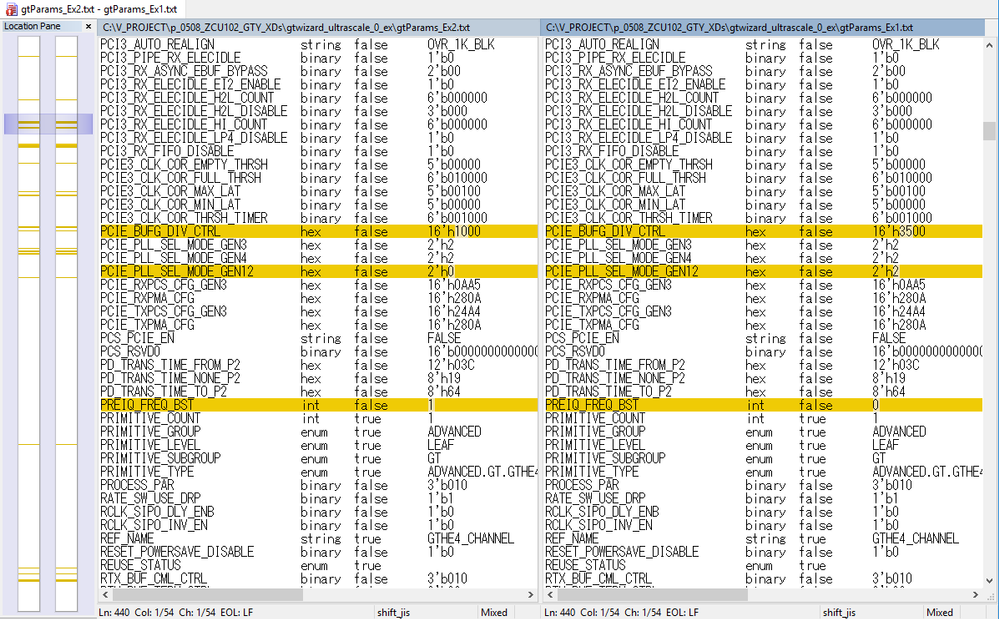

(e) 比较输出

通过比较来自 GTH/GTY 配置的gtParams.txt输出,即可立即查看不同的属性。

(f) 动态重配置端口接口 (DRP I/F)

所需属性必须通过 DRP I/F 来设置。

在 (UG576)/(UG578) 的附录 B/C 中详列了每个属性的地址。

如果您不熟悉 DRP I/F,请参阅 (UG576)/(UG578) 的第 2 章,以获取更多信息。

(g) 复位

在 DRP I/F 上设置完属性后,必须先再次执行复位,然后才能使用 GTH/GTY。

注:建议最好使用此脚本生成gtParams.txt,然后再进行比较,而不是直接比较封装器 RTL。

由于除 Channel 和 Common 属性外,还可比较修复后的外部端口,因此您可放心更改这些属性。

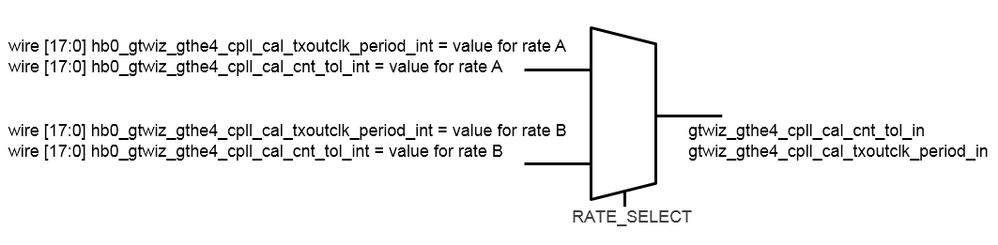

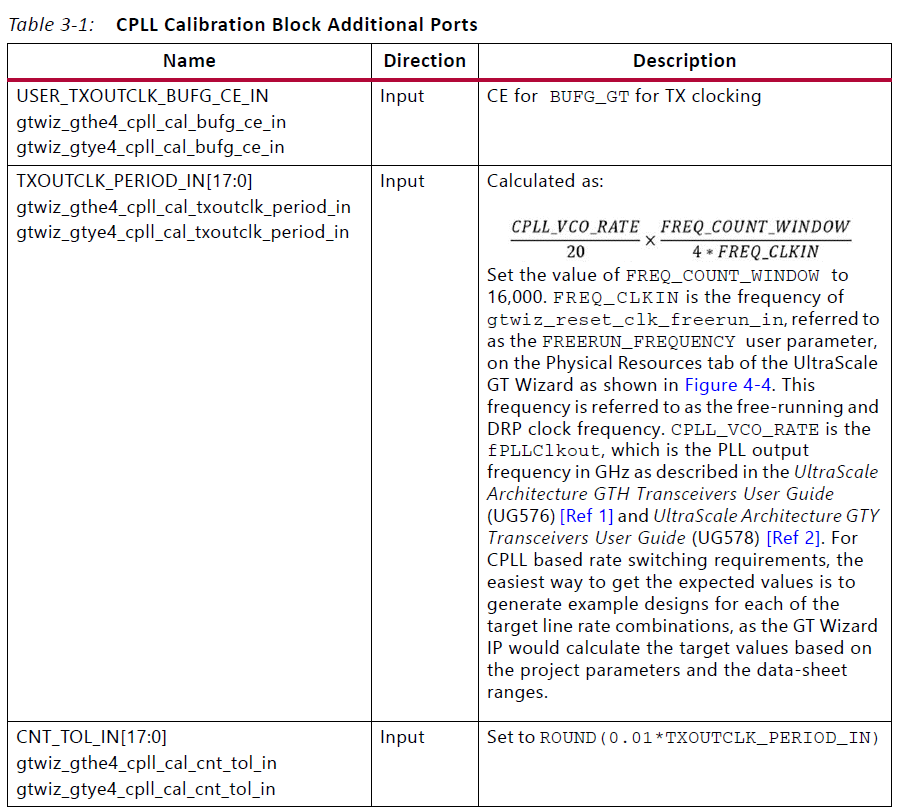

2.更改 CPLL 校准模块的设置

如果在设计中使用了 CPLL,那么必须在 CPLL 校准模块中更改信号。

请参阅(赛灵思答复记录 70485),以获取有关更改信号所需的设置更改的信息

【答复记录70485,https://china.xilinx.com/support/answers/70485.html】

综上,如需动态更改UltraScale/UltraScale+ GTH/GTY 的线速率,请遵循上述步骤 (1) 和 (2) 进行操作。

-

收发器

+关注

关注

10文章

3795浏览量

110634 -

IP

+关注

关注

5文章

1849浏览量

154957 -

UltraScale

+关注

关注

0文章

125浏览量

32224

原文标题:开发者分享 | 如何动态更改 UltraScale/UltraScale+ GTH/GTY 线速率

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

现已上市:AMD Spartan UltraScale+ FPGA SCU35 评估套件——面向所有开发人员的经济实惠平台

AMD Spartan UltraScale+ FPGA的优势和亮点

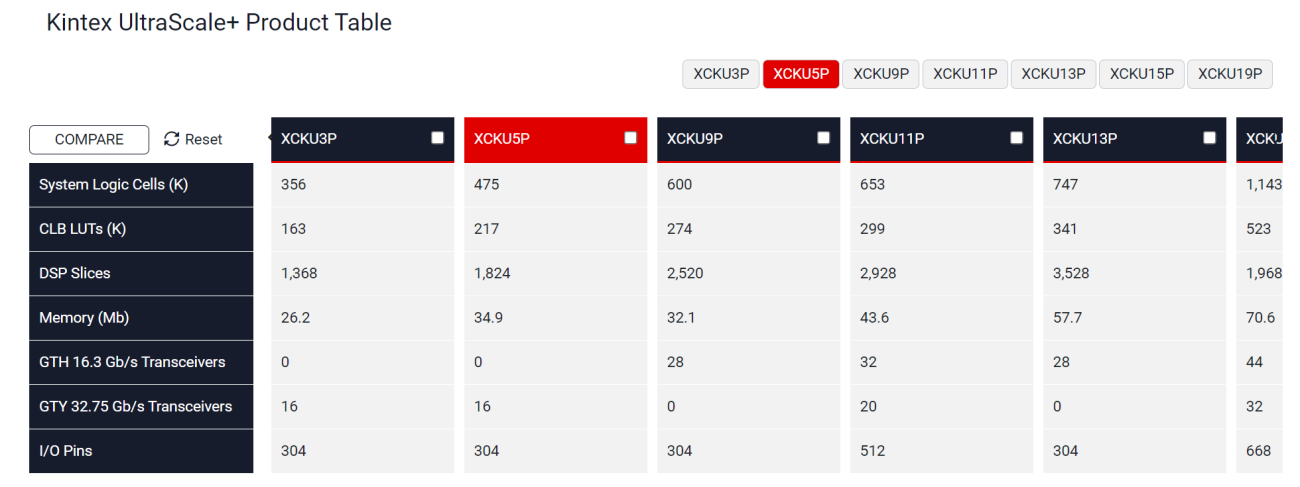

fpga开发板 璞致 Kintex UltraScale Plus PZ-KU3P 与 PZ-KU5P核心板与开发板用户手册

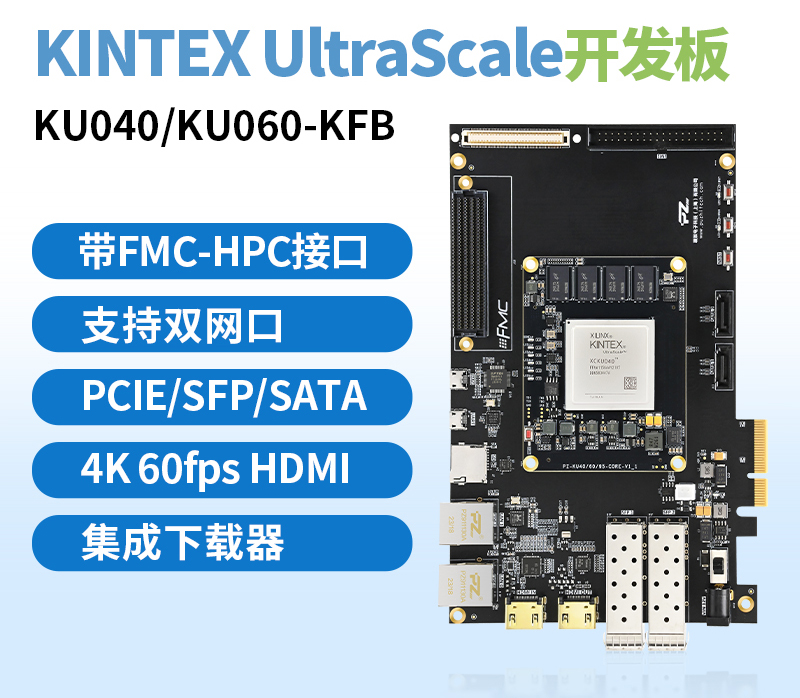

Kintex UltraScale 纯 FPGA 开发平台,释放高速并行计算潜能,高性价比的 FPGA 解决方案

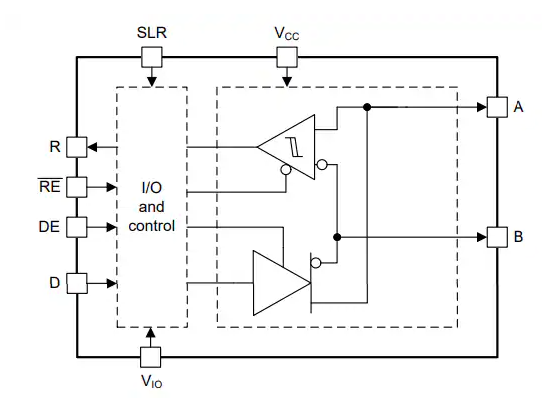

德州仪器THVD1400V汽车级RS-485收发器技术解析

璞致电子 UltraScale+ RFSoC 架构下的软件无线电旗舰开发平台

AMD FPGA异步模式与同步模式的对比

AMD Spartan UltraScale+ FPGA 开始量产出货

Xilinx Ultrascale系列FPGA的时钟资源与架构解析

无线收发器工作原理,无线收发器怎么使用

高速接口7系列收发器GTP介绍

动态更改UltraScale/UltraScale+ GTH/GTY收发器线速率设置的方法

动态更改UltraScale/UltraScale+ GTH/GTY收发器线速率设置的方法

评论