EPFL研究人员已经开发出一种比当今最快的晶体管运行速度快十倍的器件。新设备的运行速度也比目前计算机中的晶体管快100倍左右。他们发明的纳米级设备能够产生高功率太赫兹波。这位科学家说,众所周知,这些波很难产生。由于很难产生这种波,因此它有着广泛的应用前景,包括成像或传感以及高速无线通信。

研究人员还说,该装置的高功率皮秒操作有望用于先进的医疗技术,包括癌症治疗。太赫兹波在电磁频谱中介于微波和红外辐射之间,以每秒10亿至30万亿次的频率振荡。太赫兹波因其独特的特性而受到追捧,包括穿透纸张、衣物、木材和墙壁的能力。

这些电波还能够携带数据,这可能为更快的无线通信打开了大门。这些波也是非电离的,不会对人体健康造成危害。科学家们创造的技术可以安装在芯片上,也可以是柔性介质,有朝一日可以安装在智能手机或其他手持设备上。所描述的设备是紧凑和廉价的,能够在短时间内从一个微小的源产生高强度的波。

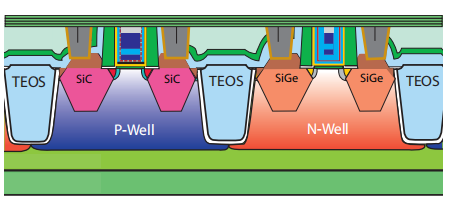

它通过在10皮秒范围内产生从10V到100V的电压尖峰来产生“火花”。该设备每秒可以接受多达5000万个信号,从而以近乎连续的方式产生火花。结构包括一对金属板,它们之间的距离接近20纳米。通过向其中一块板施加电压电子浪涌形成纳米等离子体。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

晶体管

+关注

关注

78文章

10443浏览量

148687 -

纳米

+关注

关注

2文章

731浏览量

42663

发布评论请先 登录

相关推荐

热点推荐

晶体管中界面层的作用和重要性

在芯片制造的宏大叙事中,人们常常津津乐道于光刻机如何雕刻纳米级线条,刻蚀机如何打通层层叠叠的沟槽。但有一个极其关键的薄膜,薄到只有几个原子层厚度,却决定着整个晶体管的生死——它就是界面层。

我们该如何理解“微加工”,纳米级精度技术构成的重新解读

在于“稳”。

当你的设备每分钟发射数千万个脉冲,第一个孔和第一千万个孔的几何一致性,才是衡量工艺水平的标尺。而要做到这一点,单靠硬件远远不够。

这里就不得不提闭环控制的重要性。在纳米级加工中,热漂移

发表于 03-16 16:27

CGH40006P射频晶体管

)更高的电子迁移率,显著提升开关速度和频率响应。宽带宽能力:支持多倍频程应用,适用于十倍频程带宽功率放大器。高功率密度:单位栅宽功率密度高,减少器件尺寸,提升系统集成度。效率与增益高效率设计降低

发表于 02-03 10:00

漏致势垒降低效应如何影响晶体管性能

随着智能手机、电脑等电子设备不断追求轻薄化,芯片中的晶体管尺寸已缩小至纳米级(如3nm、2nm)。但尺寸缩小的同时,一个名为“漏致势垒降低效应(DIBL)”的物理现象逐渐成为制约芯片性能的关键难题。

比斯特850B晶体管双面自动点焊机成为动力电池产线的“效率引擎”的依据

作为电芯成组过程中的重要工序,焊接的速度、质量与稳定性,往往是整条产线效率提升的瓶颈所在。深圳比斯特自动化设备有限公司深刻洞察这一产业需求,推出的850B晶体管双面自动点焊机,凭借其创

决战纳米级缺陷!东亚合成IXEPLAS纳米离子捕捉剂如何助力先进封装?

随着芯片制程不断微缩,先进封装中的离子迁移问题愈发凸显。传统微米级添加剂面临分散不均、影响流动性等挑战。本文将深度解析日本东亚合成IXEPLAS纳米级离子捕捉剂的技术突破,及其在解决高密度封装可靠性难题上的独特优势。

破解铜/银迁移难题:纳米级离子捕捉剂在先进封装中的工程化应用

在追求更高I/O密度和更快信号传输的驱动下,铜互连与银浆印刷已成为先进封装的标准配置。然而,Cu²⁺和Ag⁺在电场下的迁移速度是Al³⁺的5-8倍,极易引发枝晶生长导致短路失效。本文聚焦这一行业痛点,系统阐述纳米级离子捕捉剂IX

晶体管的定义,晶体管测量参数和参数测量仪器

晶体管是一种以半导体材料为基础的电子元件,具有检波、整流、放大、开关、稳压和信号调制等多种功能。其核心是通过控制输入电流或电压来调节输出电流,实现信号放大或电路开关功能。 基本定义 晶体管泛指

多值电场型电压选择晶体管结构

多值电场型电压选择晶体管结构

为满足多进制逻辑运算的需要,设计了一款多值电场型电压选择晶体管。控制二进制电路通断需要二进制逻辑门电路,实际上是对电压的一种选择,而传统二进制逻辑门电路通常比较复杂

发表于 09-15 15:31

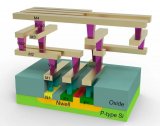

晶体管架构的演变过程

芯片制程从微米级进入2纳米时代,晶体管架构经历了从 Planar FET 到 MBCFET的四次关键演变。这不仅仅是形状的变化,更是一次次对物理极限的挑战。从平面晶体管到MBCFET,

下一代高速芯片晶体管解制造问题解决了!

步骤造成的损坏,并且可以使用成熟的二氧化硅材料和工具来构建。

由于现在的壁厚为 15 纳米,这可能会影响晶体管密度,因为外壁叉片器件比内壁叉片晶体管更大。然而,外壁叉片

发表于 06-20 10:40

新纳米级设备比晶体管运行速度快十倍

新纳米级设备比晶体管运行速度快十倍

评论