互连设计技术包括测试、仿真以及各种相关标准,其中测试是验证各种仿真分析结果的方法和手段。优秀的测试方法和手段是保证互连设计分析的必要条件,对于传统的信号波形测试,主要应当关注的是探头引线的长度,避免pigtail引入不必要的噪声。本文主要讨论互连测试技术的新应用及其发展。

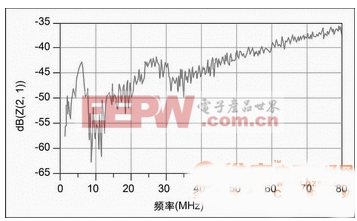

图1:0.1uf电容阻抗曲线

近些年,随着信号速率的不断提升,测试对象出现了显著的变化,不再仅仅局限于传统的利用示波器测试信号波形,电源地噪声、同步开关噪声(ssn)、抖动(jitter)逐渐成为互连设计工程师的关注重点,一些射频领域的仪器已被应用于互连设计。互连设计中常用的测试仪器包括频谱分析仪、网络分析仪、示波器以及这些仪器所使用的各种探头和夹具,为了适应不断提高的信号速率,这些测试仪器的使用方法发生了显著的变化。本文以这些测试仪器为工具,主要从测试的校准方法、无源器件的建模方法、电源完整性测试、时钟信号抖动的测试方法等方面介绍近年来互连设计测试技术的发展。

在文章的最后,还将结合刚刚结束的designcon2005大会对未来测试技术的发展作简要介绍。

校准方法

在三种常用的测试仪器中,网络分析仪的校准方法最为严谨,频谱分析仪次之,示波器的校准方法最为简单。因此,我们这里主要讨论网络分析仪的校准方法。网络分析仪常用的校准方法有三种,thru、trl和solt。三种方法的特性如表1所示。

表1:网络分析仪常用的校准

thru的实质是归一化,校准时网络分析仪记录夹具的测试结果(s21_c),在实际测试中,直接将测试结果(s21_m)与s21_c相除,即得到待测件的测试结果(s21_a)。thru校准忽略了测试夹具中的不匹配造成的反射以及空间中的电磁耦合,因此,它的校准精度最低。在仅测试s21,而且测试精度要求不高的情况下可以使用该校准方式。

在pcb等非coaxial结构中,有时需要对走线、过孔、连接器等的特性做测试。在这种情况下,测试仪器供应商没有提供标准校准件,而且测试人员也很难在测试校准端口做出良好的开路、短路、匹配负载等校准件,因此,不能做传统的solt校准。利用trl校准的优点是不需要标准校准件,可以将测试校准端口延伸至所需要的位置。目前trl校准在pcb结构测试中的使用已经比较广泛。

solt通常被认为是标准的校准方法,校准模型中共有12个校准误差参数,通过使用短路、开路、负载和直通对各种误差做校准计算。由于测试仪器供应商通常仅提供coaxial校准件,所以在非coaxial结构,无法使用solt校准方法。

以上三种校准方法都可以利用信号流图的方式做详细的分析,其中各个误差参数在信号流图中均有对应参数。通过信号流图,可以很清楚的了解各种校准方法的误差敏感度,从而了解实际测试的误差范围。这里需要提出的一点是,即使是标准的solt校准方法,在校准模型中也忽略了五个误差参数。通常情况下,这五个误差参数不会影响校准精度。但在使用时如果不注意校准夹具的设计,会出现无法校不准的现象。

频谱分析仪内部提供一个标准源供校准使用,校准时只需要将内部标准源通过测试夹具与输入端口相连即可,校准所需时间约为10分钟。示波器的校准则更为简单,将探头连接至内部标准源,确认即可,校准所需时间约为1分钟。

无源器件的测试和建模

随着信号速率的不断升高,无源器件在信号链路中的作用越来越重要,系统性能仿真分析准确与否,往往决定于无源器件的模型精度。因此,无源器件的测试和建模逐渐成为各个设备供应商的互连设计中的重要组成部分。常用的无源器件有以下几种:连接器、pcb走线及过孔、电容、电感(磁珠) 。

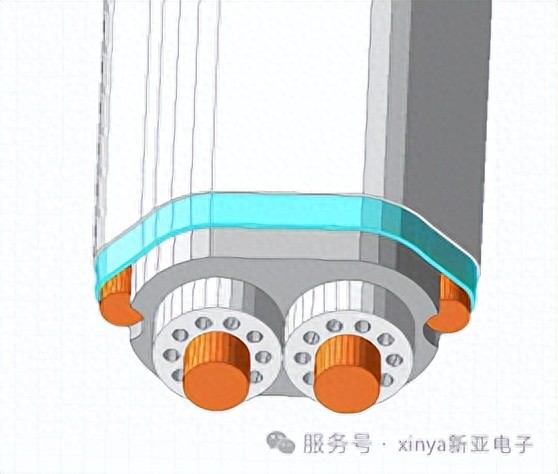

在高速信号完整性设计中,连接器对信号链路的影响最大。对于经常使用的高速连接器,通常的做法是按照trl校准方法做校准夹具,对连接器进行测试建模,供仿真分析使用。pcb走线及过孔的测试建模方法与连接器相类似,也使用trl校准将测试端口移至所需位置,然后测试建模。

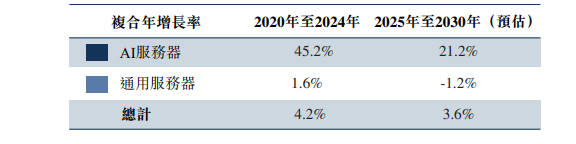

图2:某单板电源阻抗特性

电容模型在信号完整性分析中有应用,更主要的应用在电源完整性分析中。业界常用的电容建模仪器是阻抗分析仪和网络分析仪,分别适用于不同频段,阻抗分析仪适用于低频段,网络分析仪适用于高频段。如果具体实际测试中使用网络分析仪做电源完整性测试,建议在电容建模的全频段均使用网络分析仪,以保证建模和应用的一致性。由于电容的阻抗较小,在使用网络分析仪建模时,通常使用并联方式。目前业界在电容建模中没有解决的问题是如何消除夹具与电容之间的互耦,以减小夹具对建模结果的影响。

在传统的电源设计中,经常会使用电感(磁珠)对电源做隔离,以减小噪声干扰。而实际设计中,经常会出现去除隔离电感(磁珠),电源地噪声反而减小。这是由于电感(磁珠)与其它滤波器件产生谐振。为了避免这种情况的发生,有必要对电感(磁珠)建模并仿真以避免谐振。业界常用的电感(磁珠)建模方式也是采用网络分析仪,具体方法与电容建模相类似,不同之处在于电感(磁珠)建模时采用串联方式,电容建模时采用并联方式。

上面的几种无源器件的建模主要应用在信号完整性和电源完整性方面,近些年emi的仿真分析正逐步发展,关于emi无源器件的测试建模也逐渐成为互连设计的重点。如图1所示为电容的阻抗曲线。

电源完整性测试

随着芯片功率不断升高,工作电压不断降低,电源地噪声逐渐成为互连设计中关注的对象。从测试对象的角度,电源完整性测试可分为两部分,电源系统特性测试和电源地噪声测试。前者是对系统供电部分性能的测试(无源测试),后者是直接测试系统工作时的电源地噪声(有源测试),同步开关噪声也可归类为电源地噪声。

测试电源系统性能时,通常使用网络分析仪,测试对象是电源系统的self-impedance和transfer-impedance。一般情况下,电源系统的阻抗均远小于网络分析仪系统阻抗(50欧姆),所以测试时只要做直通校准就可以了,利用公式s21=z/25就可以得到电源系统的阻抗。图2所示为某单板电源阻抗特性。

测试电源地噪声可以使用频谱分析仪和示波器,频谱分析仪的输入端口不能接入直流分量,因此在测试电源地噪声时,必须在测试夹具中串连dc-blocking。频谱分析仪的输入阻抗为50欧姆,电源地网络的阻抗一般为毫欧姆级,所以,测试夹具不会对待测系统产生影响。示波器的输入阻抗随设置的不同而改变,以泰克公司的tds784为例,其低频截至频率随耦合方式和系统阻抗变化而变化,如表2所示。

上面所描述的方法都是测试单板上的电源地噪声,而真正影响芯片工作的是芯片内的电源地噪声,这时需要借助同步开关噪声测试来确定芯片内的电源地噪声。设芯片有n个io端口,令其中一个保持静止,另外n-1个同时翻转,测试静止网络上的信号波形,即同步开关噪声。同步开关噪声中既包括电源地噪声,也包括封装内不同信号之间的串扰,目前没有办法将二者完全区分开。

表2:示波器输入阻抗随设置而改变

时钟信号抖动的测试

在一些高端产品中,抖动逐渐成为影响产品性能的重要指标,这里仅对如何利用频谱分析仪测试时钟信号抖动及问题定位做简单介绍,关于数据信号的抖动测试暂不涉及。

在大多数系统中,时钟都是由晶振或锁相环产生。时钟信号的抖动测试比较简单,不需要高端的测试仪器,使用常用的频谱分析仪就可以做问题定位。理想的时钟信号的频谱是干净的离散频谱,仅在时钟频率的倍频上有分量。如果时钟信号出现抖动,在这些倍频的附近会出现旁瓣,抖动大小与这些旁瓣的功率大小成正比。

利用频谱分析仪测试时钟抖动的具体方法是在时钟信号链路上任意找一个可测试点,将该点信号通过dc-blocking连接至频谱分析仪,观察测试结果。由于测试夹具是线性系统,因此,不必担心产生新的频谱分量。前面提到时钟都是由晶振或锁相环产生,在这种情况下,引入时钟抖动的重要原因是晶振或锁相环的电源噪声。利用前面介绍的方法测试所得的晶振或锁相环的电源噪声,与时钟频谱中的旁瓣做对比,基本可以确定出导致时钟抖动的原因。问题的解决办法是根据时钟频谱旁瓣,重新设计晶振或锁相环的滤波电路,在一般情况下,这些问题可以通过合理选择滤波电容解决。

designcon2005的技术方向

designcon是每年互连技术领域的第一次大会,每年的大会上在今年designcon2005中,主要有以下一些技术发展趋势:

a.单纯的电源完整性的仿真与测试在业界已经有很多应用,不再是分析工作中的难点。

b.电容和电感(磁珠)的建模已经在业界推广,其方法已经较为完善。

c.互连设计的重点向封装移动,板级分析已经较为成熟,同步开关噪声的仿真与测试逐渐成为业界关注的问题。

d.抖动(jitter)的测试方法及标准逐渐成为业界关注的问题,大会上有多家测试设备供应商推出自己的抖动分析仪。

总结

本文简要的对目前互连设计领域的测试对象和测试方法做了简要的介绍。随着信号速率的不断提高,逐渐出现一些新的测试内容,其中包括电源地噪声、无源器件建模、抖动等内容。作者根据自己的工作经验,提出了对于这些新的测试内容的测试方法。在传统的信号波形测试中,主要应考虑减小地线长度,以避免pigtail耦合入噪声,降低测试精度。在未来的互连设计中,由于信号工作频率提升,工作重点将向芯片封装转移,相关的测试和建模技术将成为工作重点。

-

pcb

+关注

关注

4417文章

23965浏览量

426166 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

44715

发布评论请先 登录

800G/1.6T高速互连物理层演进与测试挑战

高速PCB谐振威力,不容小觑

从内存接口到PCIe/CXL、以太网及光互连,高速互连芯片市场分析

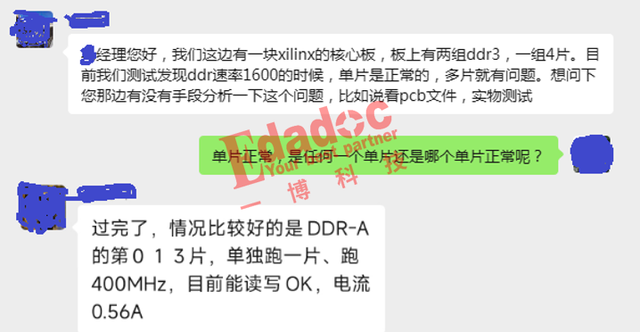

真不敢信,PCB板上就挪动了一个电阻,DDR3竟神奇变好了

立讯精密在高速互连领域取得里程碑式突破

Amphenol Multi-Trak™:下一代高速互连解决方案

极细同轴线束在MIPI/USB3/HDMI高速互连中的应用与挑战

micropython 文件同步失败是怎么回事?

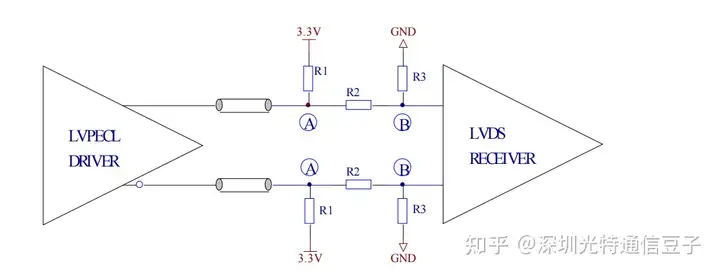

LVPECL 与 LVDS 及 PECL 与 LVDS 的互连技术解析

立讯技术高速裸线技术如何抢占高速互连赛道

GT-BGA-2000高速BGA测试插座

光纤VS 同轴互连:如何选择正确的高速测试方案?

高速PCB互连的测试技术是怎么回事

高速PCB互连的测试技术是怎么回事

评论