(1)合理选择层数:高频电路往往集成度较高,布线密度大,因此必须采用多层板进行布线,这也是降低干扰的有效手段。合理选择层数,可以大幅度地降低pcb尺寸,充分利用中间层来设置屏蔽,更好地实现就近接地,有效地降低寄生电感,有效地缩短信号的传输距离,大幅度地降低信号间的交叉干扰等。所有这些嘟有利于高频电路的可靠工作。有资料显示,同种材料的4层板要比双面板的噪声低20dB,但是板层数越高,制造工艺越复杂,成本也越高。

(2)减少高速电路元器件引脚间引线的弯折:高频电路布线的引线最好采用全直线。若需要弯折,可用45°折线或圆弧线,这样可以减少高频信号对外的发射和相互间的藕合。

(3)缩短高频电路元器件引脚间的引线:满足布线最短的最有效手段是在自动布线前对重点高速网络进行布线预约。

(4)减少高频电路元器件引脚间的引线层间交叠:所谓减少引线的层间交叠,是指减少元器件连接过程中所用的过孔。一个过孔可带来约0.5pF的分布电容,减少过孔数能显著提高速度。

(5)注意信号线近距离平行布线时所引入的交叉干扰:若无法避免平行分布,可在平牙剥言号线的反面布置大面积的地线,从而大幅度地降低干扰。同层内平行布线几乎无法避免,但是在相邻的两个层的布线方向务必取为相互垂直,在高频电路布线中最好在相邻层分别进行水平和竖直布线。在无法避免同层内平行布线时,可以在pcb反面大面积敷设地线来降低干扰。这是针对常用的双面板而言的,在使用多层板时可利用中间的电源层来实现这一功能。经过覆铜的pcb,除能提高高频抗干扰能力以外,还对散热、提高pcb强度等有很大好处。另外,若在金属机箱上的pcb固定夕助口上镀锡栅条,则不仅可以提高固定强度、保障接触良好,而且可以利用金属机箱构成合适的公共线。

(6)对特别重要的信号线或局音弹元实施地线包围的措施。对时钟等单元局部进行包地处理对高速系统创寻非常有益。

(7)各类信号布线不能形成环路,也不能形成电流环路。

(8)每个集成电路块的附近应设置,个高频去藕电容。

地线设计

地线设计在电子设备中,控制干扰的重要方法是接地。如果能将度翅拜口屏蔽正确结合起来使用,可解决大部分的干扰问题。在电子设备中,地线结构大致有系统地、机壳地(屏蔽地)、数字地(逻辑地)和模拟地等。在地线设计中应注意以下4点。

1)正确选择单点接地与多点接地在假须电路中,信号的工作频率通常小于1MHz,布线和元器件间的电感影响较小,而接地电路形成的环汤树干扰影响较大,因而应采用一点接地方式。当信号工作频率大于10MHz时,地线阻抗将变得很大,此时应尽量降低地线阻抗,应采用就近多点接地方式。当工作频率在1~10MHz时,如果采用一点接地方式,其地线长度不应超过波长的1/20,否则应采用多点接地方式。

2)将数字电路与模拟电路分拜当pcb上既有高速逻辑电路又有线性电路时,应使它们尽量分开,两者的地线不要相混,并且分别与电源端地线相连。要尽量加大线性电路的接地面积。

3)尽量加粗接地线若接地线很细,接地电创各随电流的变化而变化,导致电子设备的定时信号电平不稳,抗噪声性能变坏。因此,应尽量将陵地线加粗,使它能通过3倍于pcb的允许电流。若有可能,接地线的宽度应大于3mm。

4)将接地线构成闭环路设计仅由数字电路组成的pcb的地线系统时,应将地线设计成闭环路,这样可以明显地提高抗噪声能力。其原因在于,pcb上有很多集成电路元器件,尤其遇有耗电多的元器件时,因受地线粗细的限制,会在地线上产生较大的电位差,从而引起抗噪声能力下降。若将地线构成环路,则会缩小电位差,从而提高电子设备的抗噪声能力。

责任编辑:ct

-

pcb

+关注

关注

4392文章

23750浏览量

421056 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

44402

发布评论请先 登录

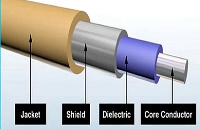

高速信号线是否必须选双屏蔽极细同轴线束?

高扇出信号线优化技巧(下)

高扇出信号线优化技巧(上)

PCB设计如何用电源去耦电容改善高速信号质量

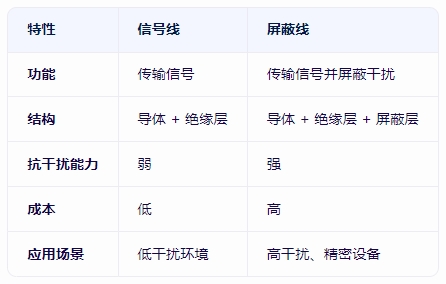

信号线和屏蔽线有什么区别

一文告诉你为什么不要随便在高速线旁边铺铜!

信号线和光纤线的区别是什么

高速信号线走线规则有哪些

信号线电压高怎么回事,如何解决

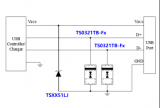

晶扬电子高速信号线专用浪涌保护器件TS0321TB-Fx解析

高速PCB信号线如何去设计地线

高速PCB信号线如何去设计地线

评论