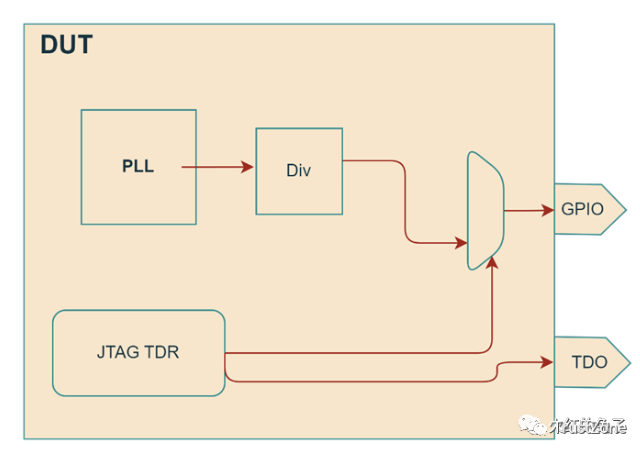

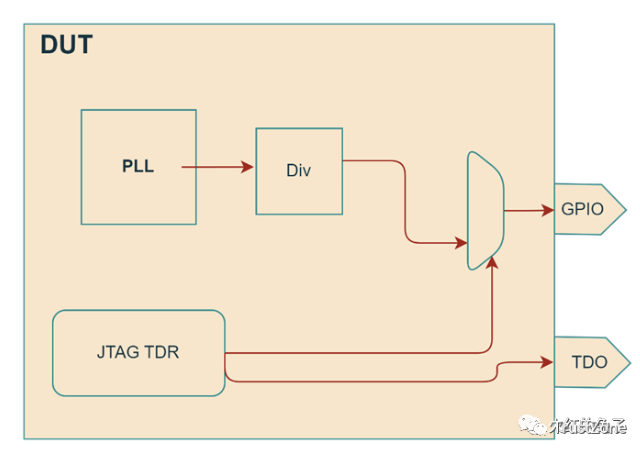

自动测试设备 (ATE)对PLL(锁相环)进行测试时,我们首先要明白PLL在系统级芯片(SoC)中的重要性。

2023-11-01 15:43:10 683

683

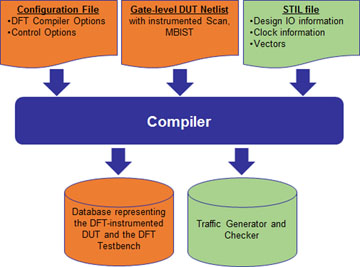

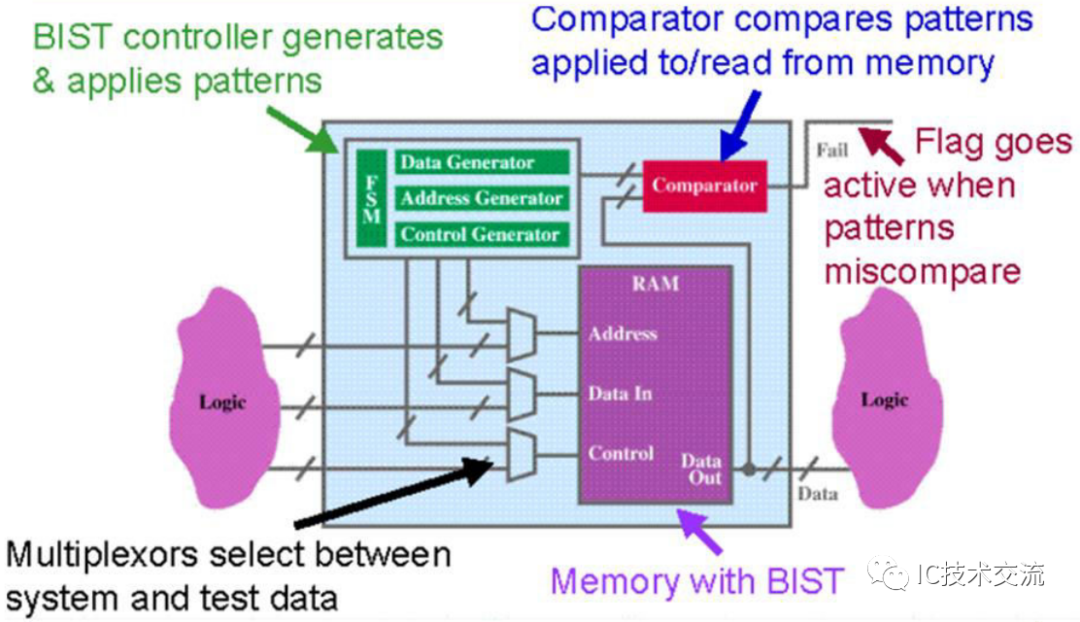

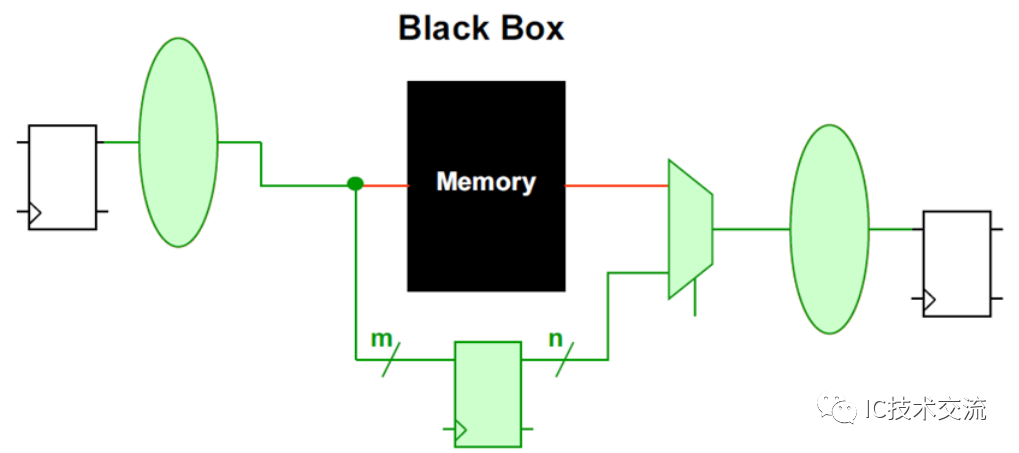

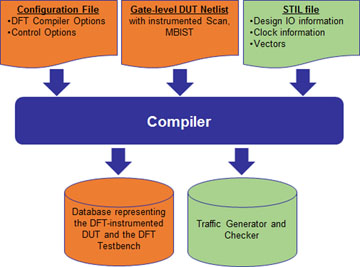

当SoC上有超过80%的芯片面积被各种形式的存储器占用之时,存储器的DFT测试已经变得非常重要。

2023-12-09 09:56:55 1205

1205

片上芯片SoC挑战传统测试方案,SoC生产技术的成功,依靠的是厂商以最低的生产成本实现大量的生产能力

2012-01-28 17:14:43 1834

1834

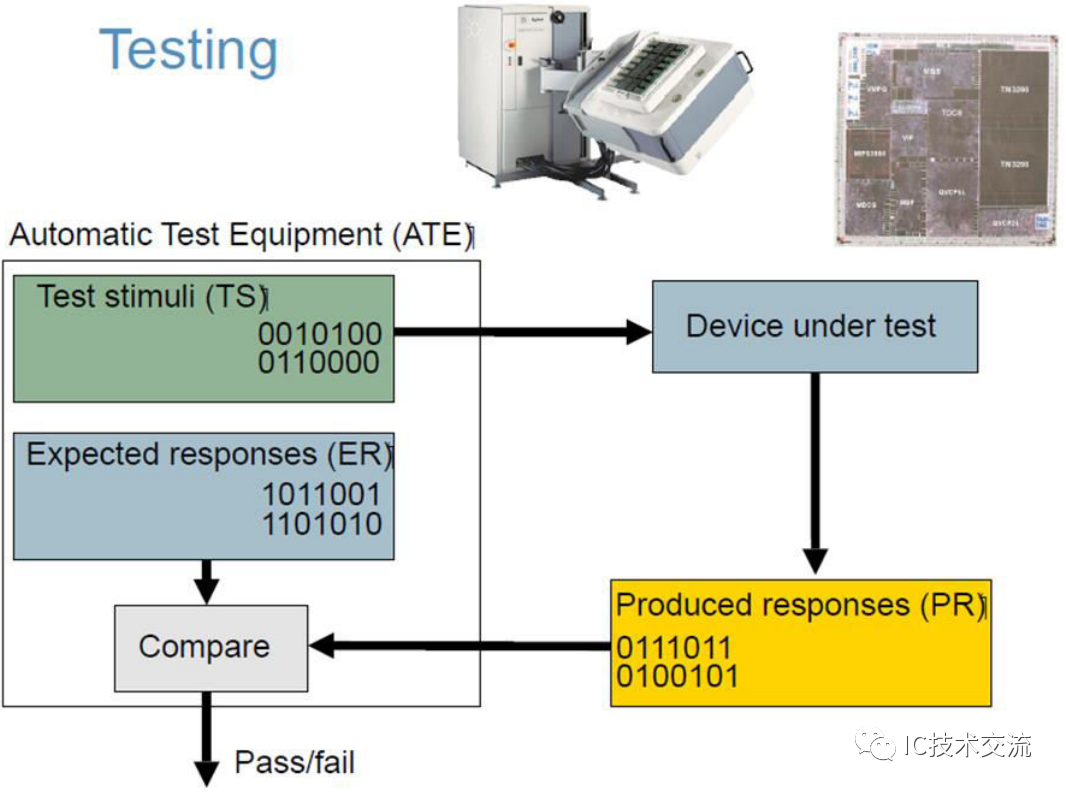

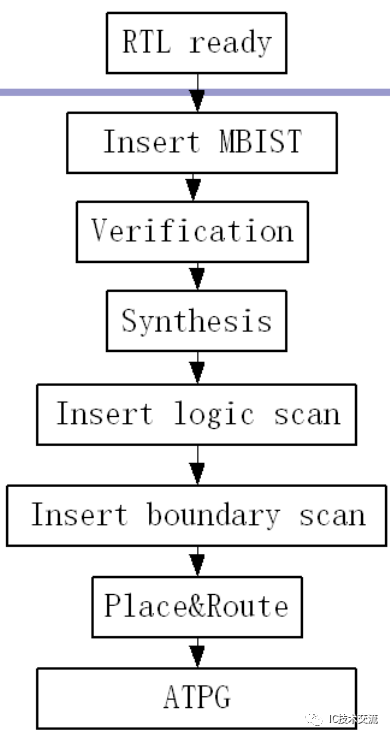

DFT:全称是 Design for Test,可测性设计,通过在芯片原始设计中插入各种用于提高芯片可测试性(包括可控制性和可观测性)的硬件逻辑,从而使芯片变得容易测试,大幅度节省芯片测试的成本

2021-07-23 07:28:32

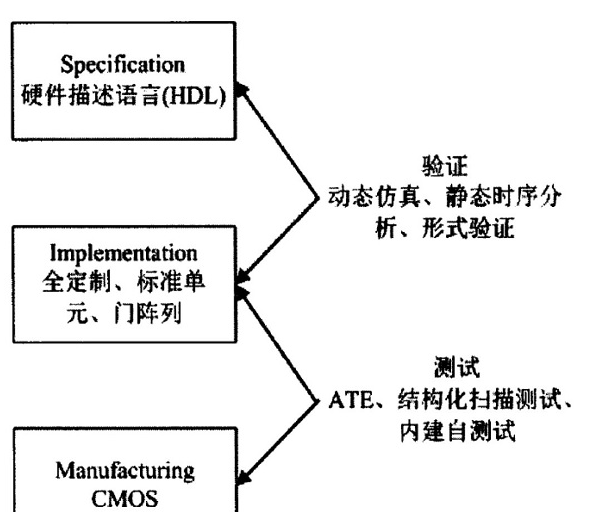

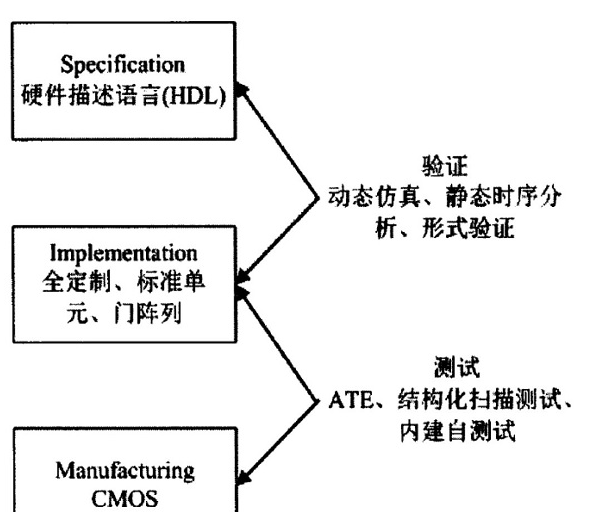

虽然可测性设计(DFT)与内置自检(BIST)技术已在SoC(系统级芯片)设计中受到广泛关注,但仍然只是被看作“后端”的事。实际上,这些技术在器件整个设计周期中都非常重要,可以保证产品测试错误覆盖率

2011-12-15 09:53:14

DFT是什么?DFT在芯片设计领域的含义,即可测性设计(Design for Test), 可测试性设计(Design for Test,简称DFT)是电路和芯片设计的重要环节,它通过在芯片原始

2012-01-11 14:33:22

DFT是什么?DFT在芯片设计领域的含义,即可测性设计(Design for Test), 可测试性设计(Design for Test,简称DFT)是电路和芯片设计的重要环节,它通过在芯片原始

2012-01-11 14:28:06

量也大为减小.DFT与FFT相比还具有变换点数或采样率选择更灵活、实时性更好、更容易控制溢出和动态范围、运算编程简单、可方便地在非DSP芯片中编程实现等优点.因此在实际应用中可以从具体条件出发

2014-05-22 20:43:36

SoC测试技术传统的测试方法和流程面临的挑战是什么?SoC测试技术一体化测试流程是怎样的?基于光子探测的SoC测试技术是什么?有什么目的?

2021-04-15 06:16:53

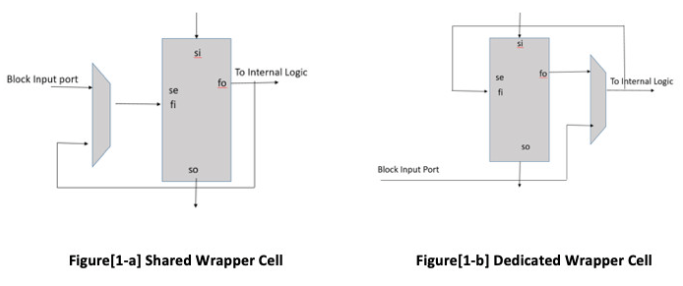

全面测试。SoC 设备的测试已经成为一个越来越具有挑战性的任务,因为这些设备已经变得非常复杂。SoC 芯片是逐块构造的,因此当它也是逐块进行测试时,测试是有效的。设计者可以安装一个专门的,可配

2022-04-01 11:18:18

请问为什么SoC的发展能够将测试与测量设备带入芯片领域?

2021-04-15 06:02:34

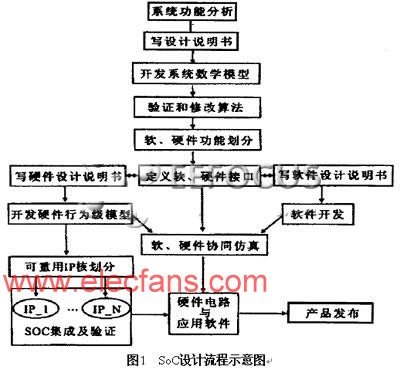

、SoC验证技术、可测性设计技术、低功耗设计技术、超深亚微米电路实现技术,并且包含做嵌入式软件移植、开发研究,是一门跨学科的新兴研究领域

2016-05-24 19:18:54

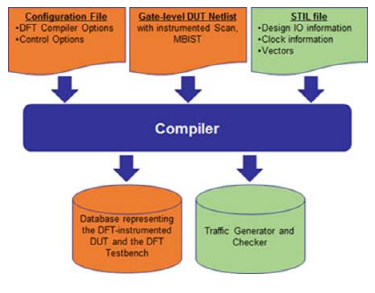

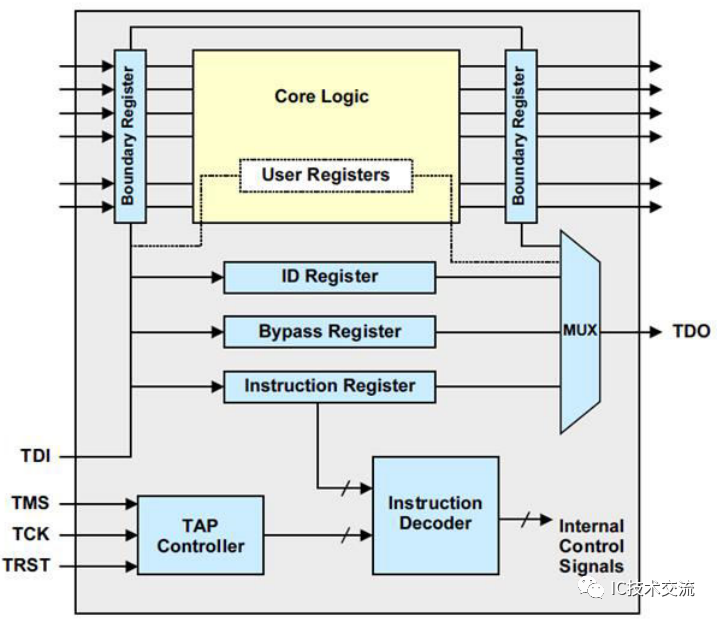

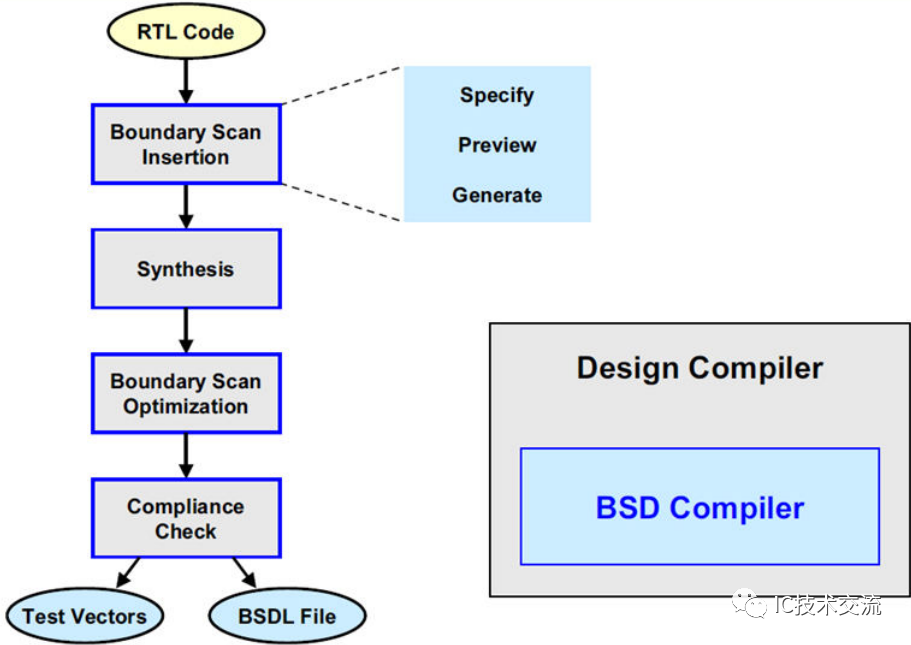

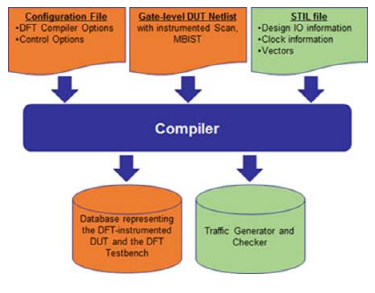

dft可测试性设计,前言可测试性设计方法之一:扫描设计方法可测试性设计方法之二:标准IEEE测试访问方法可测试性设计方法之三:逻辑内建自测试可测试性设计方法之四:通过MBIST测试寄存器总结...

2021-07-22 09:10:42

哪位大虾推荐个测试元器件管脚可焊性的装置啊,谢谢啦

2012-10-26 12:40:45

实验二 FFT与DFT计算时间的比较及圆周卷积代替线性卷积的有效性实验:一 实验目的1:掌握FFT基2时间(或基2频率)抽选法,理解其提高减少乘法运算次数提高运算速度的原理。2:掌握FFT圆周卷积

2011-12-29 21:52:49

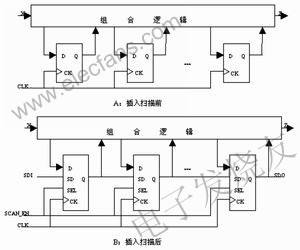

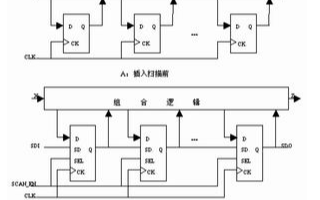

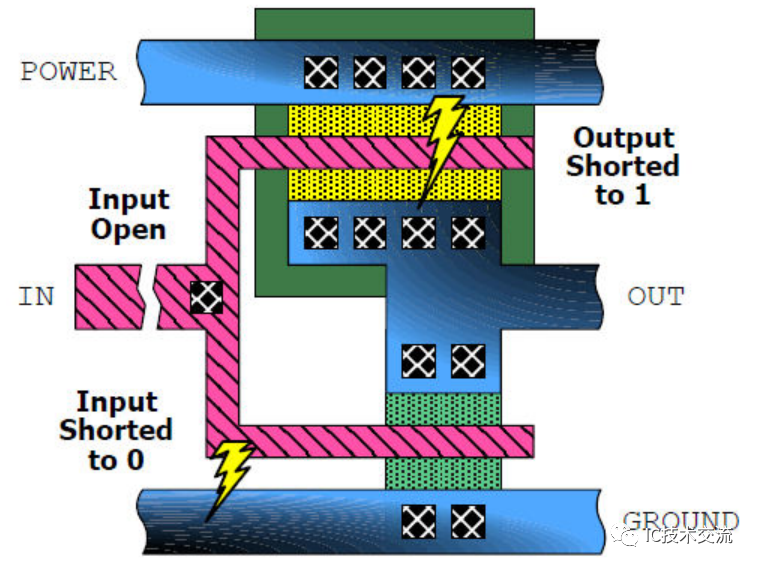

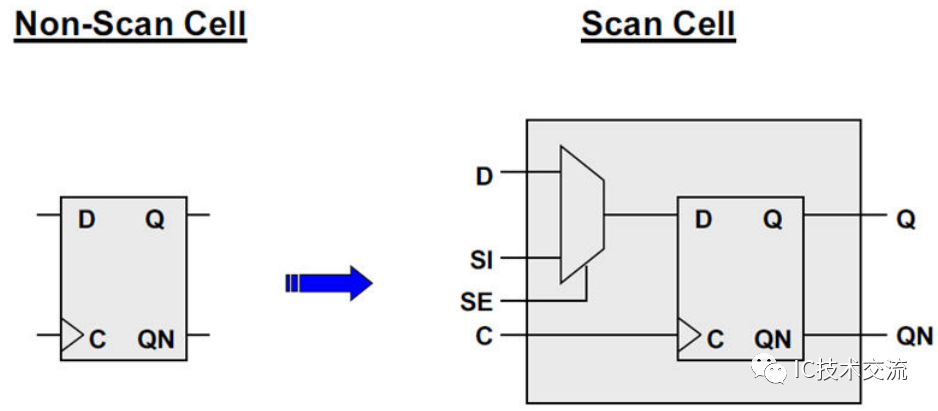

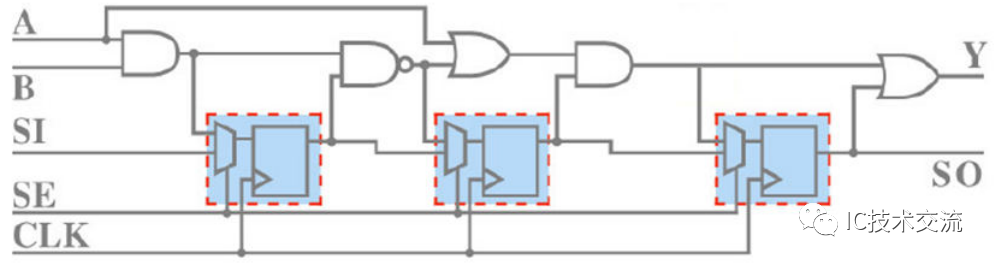

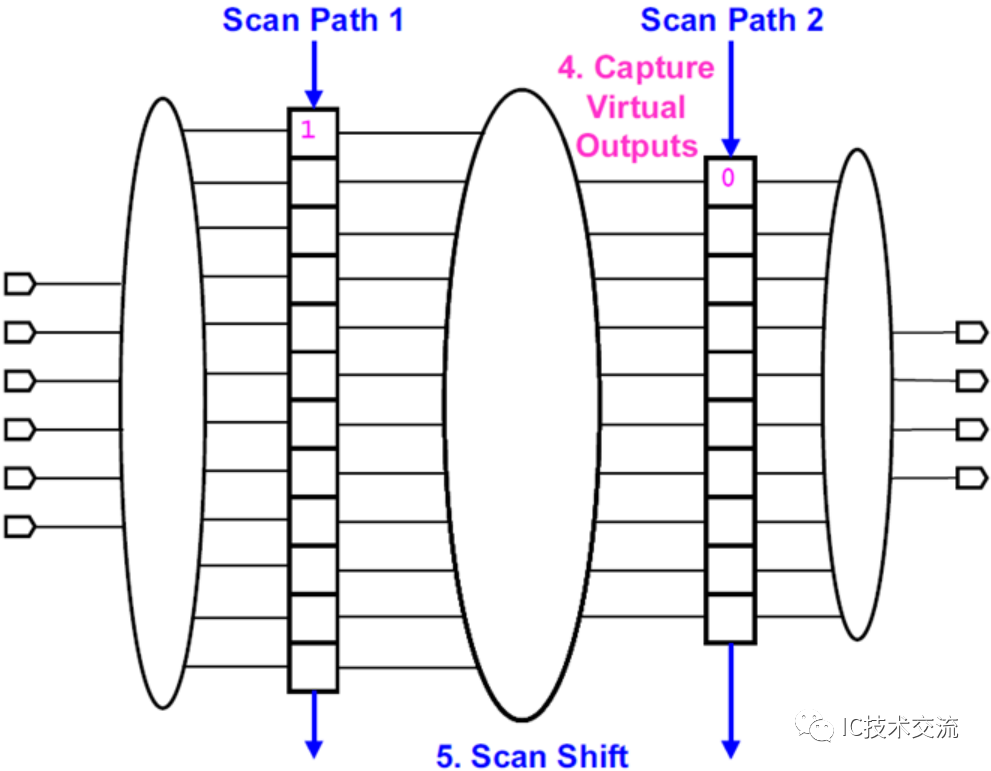

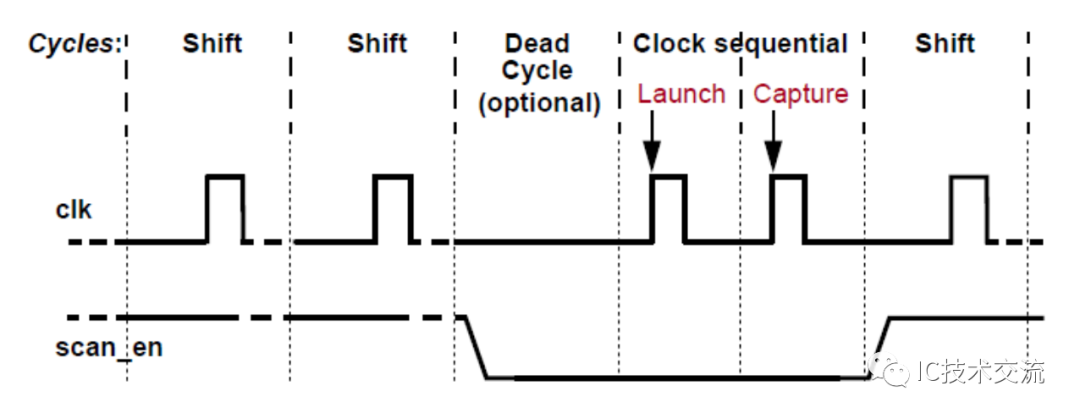

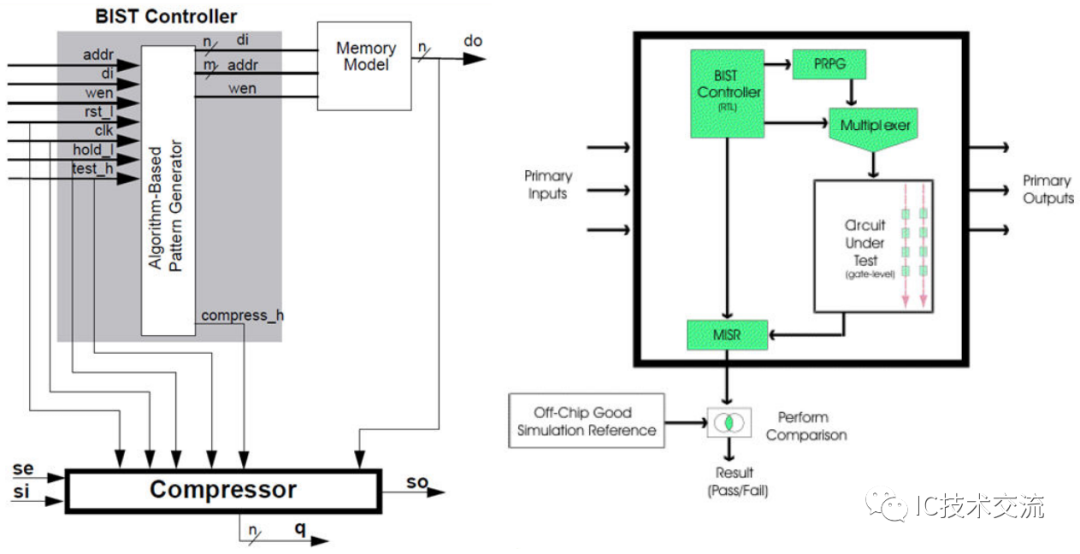

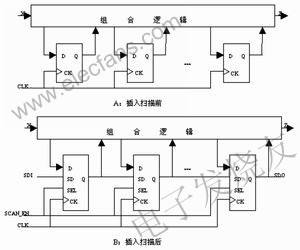

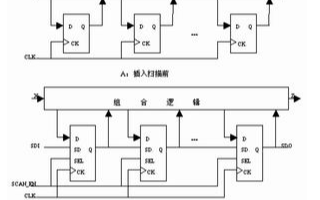

法是一种针对时序电路芯片的DFT方案.其基本原理是时序电路可以模型化为一个组合电路网络和带触发器(Flip-Flop,简称FF)的时序电路网络的反馈。内建自测试 内建自测试(BIST)设计技术通过在

2011-12-15 09:35:34

策略性是指对于IP包的路由是以网络管理员根据需要定下的一些策略为主要依据进行路由的。例如我们可以有这样的策略:“所有来直自网A的包,选择X路径;其他选择Y路径”,或者是“所有TOS为A的包选择路径F;其他选者路径K”。

2019-07-23 06:11:18

测试性设计是第二代的DFT方法,其主要思想是从可测试性观点出发,对电路结构提出一定的设计规则以使所设计的电路便于测试。这种方法通常采用扫描设计,通常采用扫描设计,包括电平敏感扫描设计、扫描通路和扫描

2018-09-19 16:17:24

产品设计的可测试性(De sign For Testability. OFT) 也是产品可制造性的主要内容从生产角度考虑也是设计的工艺性之一。它是指在设计时考虑产品性能能够检测的难易程度,也就是说

2016-07-28 10:08:06

TD-HSDPA准入策略的外场测试的目的是什么?TD-HSDPA准入策略的外场测试有哪些步骤?TD-HSDPA准入策略的外场测试的结论和部署建议是什么?

2021-05-26 06:49:15

ICE在调试过程中加入了 100%可见性和可重复性,从而克服了电路内仿真 (ICE) 环境的不可预知性,并可使用其他“基于虚拟的”使用模型;•Veloce DFT可提升流片之前的可测试性设计 (DFT

2016-04-15 16:25:55

1、汽车SoC嵌入式存储器的优化诊断汽车片上系统(SoC)中的嵌入式存储器通常占据了很大的芯片面积。因此,它们的缺陷会严重影响任何自动驱动设备的生产产量。伴随着技术提升阶段和批量生产期间的统计过程

2022-09-07 15:08:41

可扫描触发器的作用有哪些?标准IEEE测试访问方法主要有哪些应用领域?可测试性设计方法有哪几种?分别有哪些优点?

2021-08-09 07:23:28

,下一步是在看不见的芯片块上测试模型的性能,以验证其预测的有效性。如果工程师验证的结果令人满意,则可以进行部署了。通过这些步骤进行的芯片块放置预测将比传统方法更有效、更快。块(block)放置的额外

2022-11-22 15:02:21

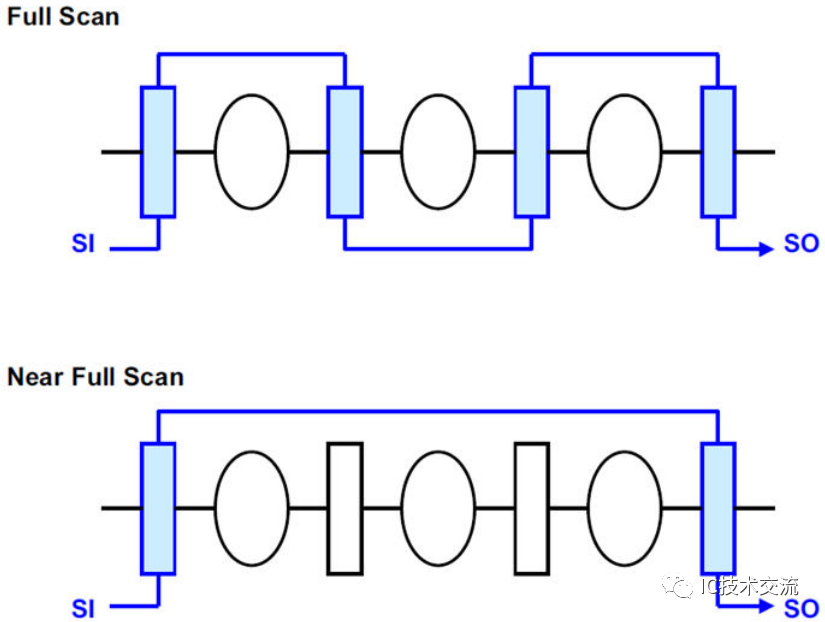

基于扫描的DFT方法扫描设计的基本原理是什么?扫描设计测试的实现过程是怎样的?基于扫描的DFT对芯片测试的影响有哪些?

2021-05-06 09:56:36

随着集成电路的发展,越来越多的ASIC和SoC开始使用嵌入式SRAM来完成数据的片上存取功能。但嵌入式SRAM的高密集性物理结构使得它很容易在生产过程中产生物理故障而影响芯片的良率,所以,SRAM

2019-10-25 06:28:55

,运算结果返回去覆盖原列向量得到一个新的矩阵,然后再对原矩阵进行行向量的DFT,同样返回得到一个新的矩阵。最后对这两个矩阵进行运算得到最终结果。这两者的次序是可颠倒的。问题在于,我不知道如何在

2012-06-27 05:23:25

如何实现SoC系统内部的实时可视性?如何在不影响系统性能的情况下采集和上载数据点?增加SoC可视性的方法包括哪些?

2021-04-15 06:03:13

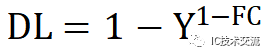

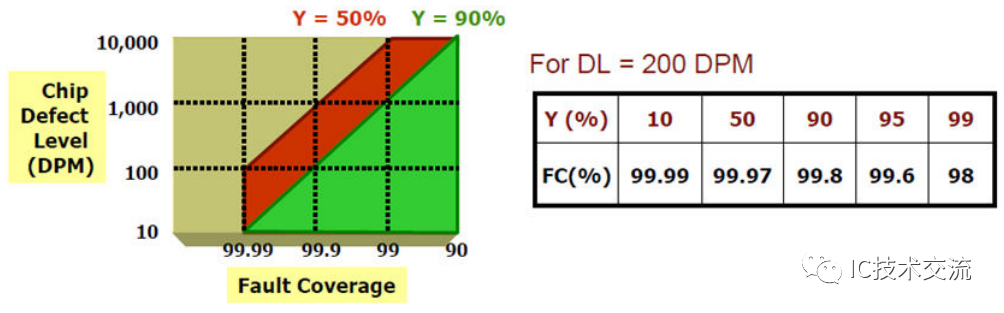

提高DFT设计测试覆盖率的有效方法是什么

2021-05-07 06:37:41

什么是可测试性?为什么要发展测试友好技术?如何去改进可测试性?

2021-04-13 06:54:39

如何改进电路设计规程来提高可测试性?

2021-04-26 06:49:51

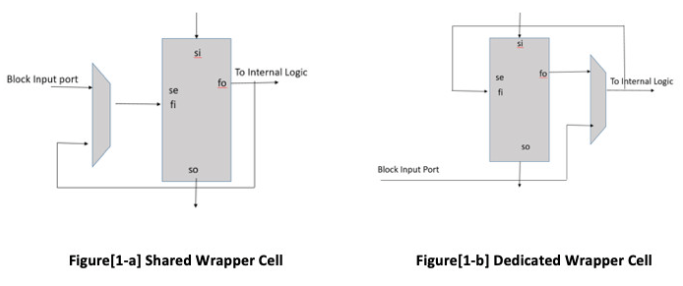

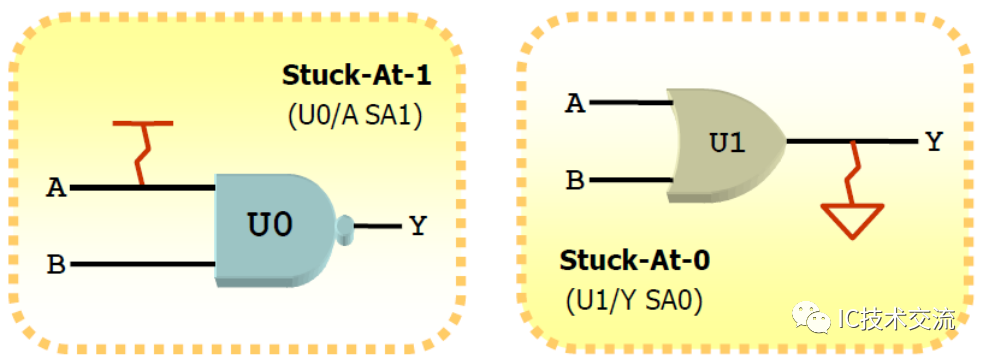

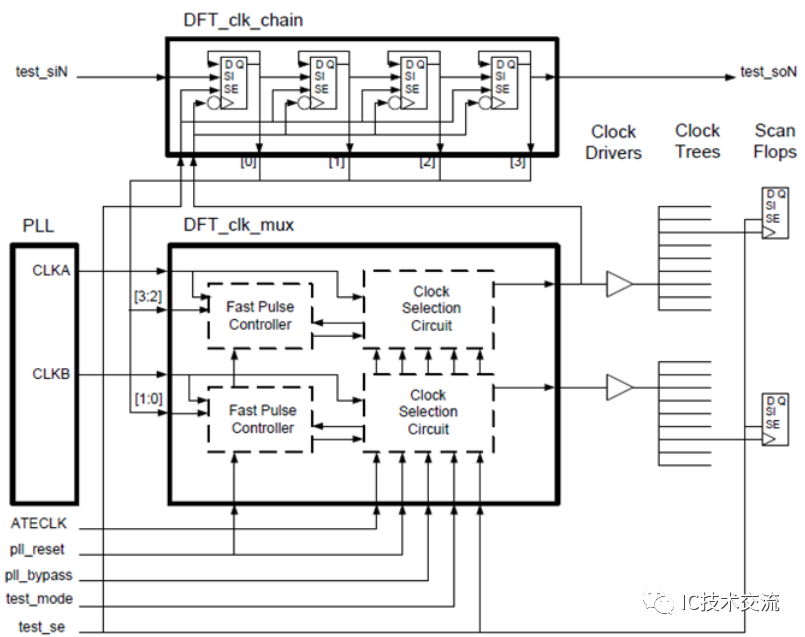

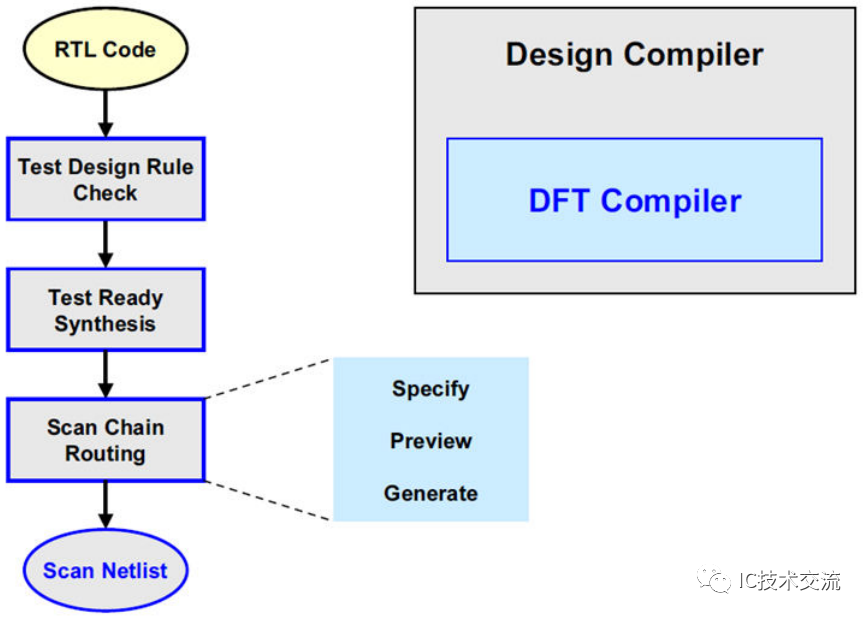

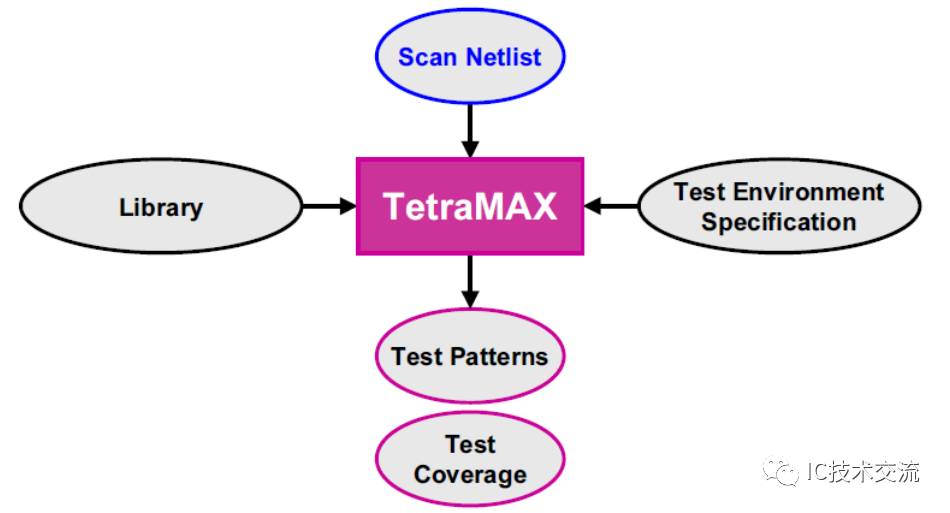

前面一期的公众号文章“让你彻底理解DFT”帮助大家理解了DFT所解决的问题。一句话来概括之就是:借助特定的辅助性设计,产生高效率的结构性测试向量以检测生产制造过程中引入芯片中的各种物理缺陷。Scan

2016-06-14 14:20:20

成为必不可少的环节。可测性设计(Design ForTest,DFT)是在芯片的设计阶段就考虑以后测试的需要,使芯片测试更加容易和充分,并降低测试成本。一个SoC包含各种可复用的功能IP核,其中嵌入式

2019-09-20 07:09:28

急招DFT工程师,职位JD如下,有兴趣简历请投递1736253011@qq.comDFT工程师Responsibilities: 1. Participate in SoC level

2017-04-14 14:11:16

改进PCB电路设计规程提高可测试性随着微型化程度不断提高,元件和布线技术也取得巨大发展,例如BGA外壳封装的高集成度的微型IC,以及导体之间的绝缘间距缩小到0.5mm,这些仅是其中的两个

2017-11-06 09:11:17

改进PCB电路设计规程提高可测试性随着微型化程度不断提高,元件和布线技术也取得巨大发展,例如BGA外壳封装的高集成度的微型IC,以及导体之间的绝缘间距缩小到0.5mm,这些仅是其中的两个

2017-11-06 10:33:34

的PCB设计布线PCB设计方式,对以后制作流程中的测试能否很好进行,影响越来越大。下面介绍几种重要规则及实用提示。 通过遵守一定的规程( DFT-Design for Testability ,可测试

2015-01-14 14:34:27

改进电路设计规程提高可测试性 随着微型化程度不断提高,元件和布线技术也取得巨大发展,例如BGA外壳封装的高集成度的微型IC,以及导体之间

2009-05-24 23:01:19

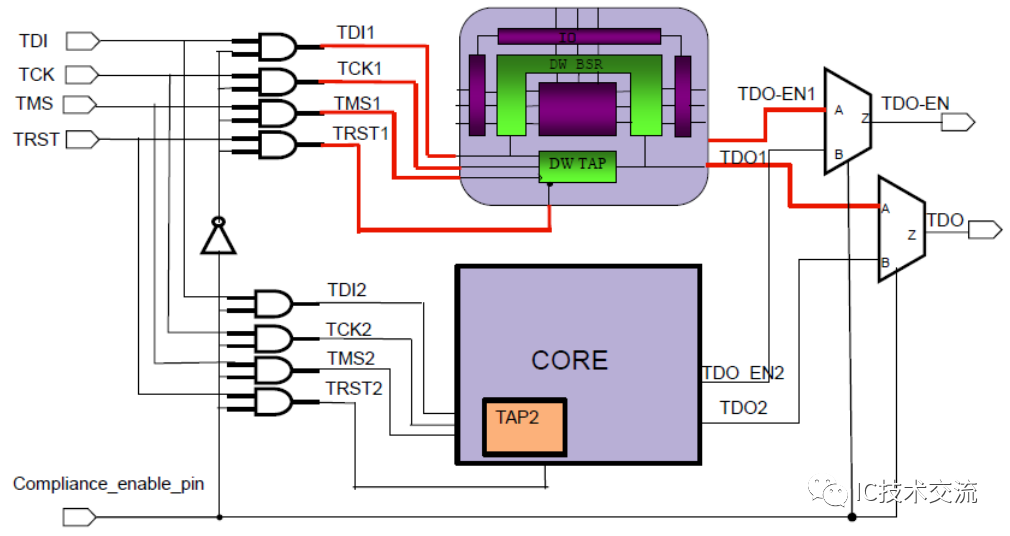

实际产品的测试需要,提出了基于JTAG接口的,包括了上述四中测试手段的可测性设计方案。该方案经过SMIC 0.18微米工艺流片验证,不仅证明功能正确,而且在保证了一定的覆盖率的条件下实现了较低的测试成本,是‘项非常实用的测试设计方案。数模混合SOC芯片的可测性方案的实现[hide][/hide]

2011-12-12 17:58:16

汽车电子的测试挑战和策略是什么

2021-05-12 06:55:18

当今硬件设计变得愈加复杂,如何创建出足够的测试来保证设计的正确性是每个硬件工程师需要面对的问题。Accellera的可移植激励测试规范(PSS、又称便携激励标准)[1]旨在希望能够提供一个独立

2020-12-18 06:23:31

的。影响测试策略的参数包括:可访问性。完全访问和大的测试焊盘总是为制造设计电路板的目标。通常不能提供完全访问有四个原因:板的尺寸。设计更小;问题是测试焊盘的“额外的”占板空间。不幸的是,多数设计工程师认为测试

2018-08-23 10:15:10

本帖最后由 gk320830 于 2015-3-4 13:43 编辑

电路板设计可测试性技术电路板制板可测试性的定义可简要解释为:电路板测试工程师在检测某种元件的特性时应该尽可能使用最简单

2013-10-08 11:26:12

本帖最后由 gk320830 于 2015-3-7 13:19 编辑

电路板设计可测试性技术电路板制板可测试性的定义可简要解释为:电路板测试工程师在检测某种元件的特性时应该尽可能使用最简单

2013-10-16 11:41:06

电路板制板可测试性的定义可简要解释为:电路板测试工程师在检测某种元件的特性时应该尽可能使用最简单的方法来测试,以确定该元件能是否到达预期的功能需求。进一步含义即: 1 检测产品是否符合技术规范

2018-11-27 10:01:40

开始,掌握了其芯片设计技术,再在高起点上进行整合各个功能的IC,可最大程度地减少工程师的工作量。 芯片解密在SiP中的应用作为替代方案,SiP 跃上整合晶片的舞台。和 SoC 不同,它是购买各家的IC

2017-06-28 15:38:06

了电路结构一致,功能自然而然也就是一致的。 接下来言归正传,DFT的全称是design for test(可测试性设计),DFT技术就是前面我们寻求的检测post-routing netlist

2016-05-25 15:32:58

DFT是什么原理?

2021-06-17 08:54:06

请问有什么策略可以提高芯片的性能?

2021-06-23 13:08:50

(Integrated Circuit,简称IC)进入超大规模集成电路时代,可测试性设计(Design for Test,简称DFT)是电路和芯片设计的重要环节,它通过在芯片原始设计中插入各种用于提高芯片可测试

2011-12-15 09:32:30

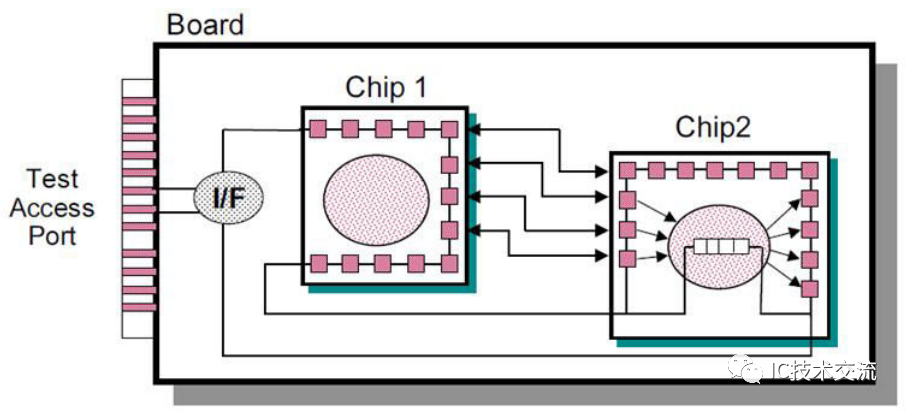

以复用为基础,通过测试访问机制(TAM, Test Access Mechanism)实现对深嵌在SOC(System On Chip)内部的IP 核(Intellectual Property, 知识产权模块)的测试,是解决SOC 测试的根本方法。本文将

2009-08-27 14:39:54 8

8 随着集成电路设计复杂度的提高和产品上市时间压力的增大,基于IP 核复用的SoC 设计已成为一种重要的设计方法。在SoC 中集成的IP 核越来越多时,IP 核的互连策略和方法就成

2009-11-28 14:40:46 8

8 本文简单描述了 SOC 芯片测试技术的复杂性,模数转换器(ADC)是SOC 芯片中的重要模块,随着器件时钟频率的不断提高,高效、准确地测试ADC 的动态参数和静态参数是当今SOC 芯

2009-12-23 15:50:21 13

13 随着自动测试设备成为电子装配过程整体的一部分,DFT必须不仅

2006-04-16 22:05:43 283

283 DFT:数字电路(fpga/asic)设计入门之可测试设计与可测性分析,离散傅里叶变换,(DFT)Direct Fouriet Transformer

可测试性技术(Design For Testability-

2010-06-07 11:00:48 29873

29873 本文通过对一种控制芯片的测试,证明通过采用插入扫描链和自动测试向量生成(ATPG)技术,可有效地简化电路的测试,提高芯片的测试覆盖率,大大减少测试向量的数量,缩

2010-09-02 10:22:52 2024

2024

什么是soc芯片

SoC(System on Chip)。SoC是在一个芯片上由于广泛使用预定制模块IP而得以快速开发的集成电路。

2010-09-10 22:50:51 45585

45585

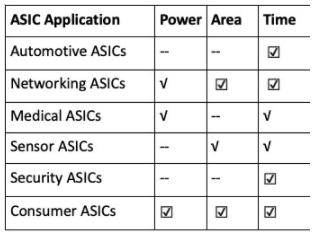

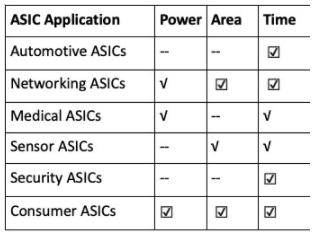

ASIC设计的平均门数不断增加,这迫使设计团队将20%到50%的开发工作花费在与测试相关的问题上,以达到良好的测试覆盖率。尽管遵循可测试设计(DFT)规则被认为是好做法,但对嵌入式R

2011-05-28 11:56:59 1357

1357

现今流行的可测试性设计(DFT:Design For Testability)为保证芯片的良品率担任着越来越重要的角色。

2012-04-20 09:39:05 6249

6249

可测试设计(DFT)是适应集成电路的发展要求所出现的一种技术,主要任务是对电路的结构进行调整,提高电路的可测性,即可控制性和可观察性。

2012-04-27 11:11:59 3154

3154

本内容介绍了DFT可测试性设计的相关知识,并列举了3中常见的可测性技术供大家学习

2012-05-30 16:42:27 7082

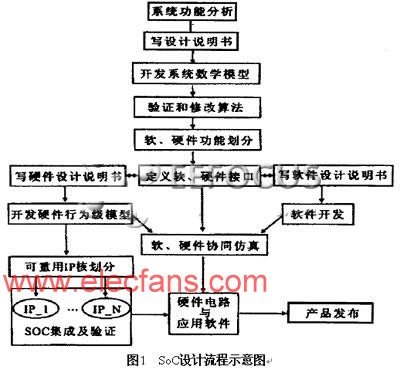

7082 本专题为你简述片上系统SoC相关知识及设计测试。包括SoC定义,SoC设计流程,SoC设计的关键技术,SoC设计范例,SoC设计测试及验证方法,最新SoC芯片解决方案。

2012-10-12 17:57:20

电池SOC估算策略研究,又需要的下来看看。

2017-01-13 13:26:03 11

11 随着芯片规模的增大,低功耗不仅是在功能与性能方面对设计者的挑战越来越大,同时对于测试而言,随着SCAN CELL的增多,在SCAN测试时,芯片的功耗也会增大。功耗越大,则芯片的温度升高,导致芯片内部

2017-11-11 16:20:38 4

4 可测试性设计 (DFT) 在市场上所有的电子设计自动化 (EDA) 工具中是最不被重视的,纵然在设计阶段提高芯片的可测试性将会大幅缩减高昂的测试成本,也是如此。最近的分析数据表明,在制造完成后测试

2017-11-28 11:28:38 0

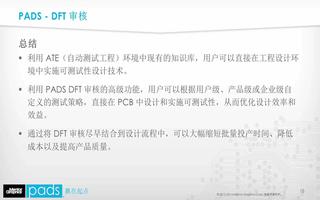

0 通过此视频可快速浏览 PADS DFT 审核的一些主要功能、优点和易用性。在设计流程的早期使用 PADS DFT 审核可大幅降低 PCB 的批量投产时间,确保 100% 的测试点覆盖和制造前所有网络的可测试性。

2019-05-21 08:06:00 2927

2927 PADS 可测试性设计 (DFT) 审核可以缩短上市时间。了解如何尽早在设计流程中利用 PCB 测试点和 DFT 审核优化设计。

2019-05-14 06:26:00 3018

3018

DFT 可以降低通过问题器件的风险,如果最终在实际应用中才发现器件有缺陷,所产生的成本将远远高于在制造阶段发现的成本。它还能避免剔除无缺陷器件,从而提高良率。插入 DFT 亦能缩短与测试开发相关的时间,并减少测试装配好的芯片所需的时间。

2019-09-16 14:31:51 1648

1648

。可测性设计(DFT)给整个测试领域开拓了一条切实可行的途径,目前国际上大中型IC设计公司基本上都采用了可测性设计的设计流程,DFT已经成为芯片设计的关键环节。

2020-07-06 11:38:47 9188

9188

随着ASIC电路结构和功能的日趋复杂,与其相关的测试问题也日益突出。在芯片测试方法和测试向量生成的研究过程中,如何降低芯片的测试成本已经成为非常重要的问题。DFT(可测性设计)通过在芯片原始设计中插入各种用于提高芯片可测性的逻辑,从而使芯片变得容易测试,大大降低了芯片的测试成本。

2020-08-18 14:57:13 2880

2880

用元素和测试点补充您的操作设计以促进电路板的功能测试被称为可测试性( DFT )设计。 DFT 与制造设计( DFM )不应混淆,尽管两者都是基于 CM 设备和过程能力的设计人员活动。 DFM

2020-10-12 20:42:17 3771

3771 Labs)业务工程处总监王钧锋先生在第四届无人驾驶及智能驾舱中国峰会AutoAI 2021上分享如何通过测试提高车载SoC芯片功能安全,探讨汽车封装与测试类型、市场需求及AEC-Q100认证等。 随着汽车行业进一步迈向智能化发展,汽车相关芯片的复杂度和

2021-06-01 10:37:25 3916

3916 下面以我所做过的一款SOC芯片来说明SOC芯片集成一个DCDC, 该DCDC具有动态电压调节,可以通过配置寄存器调节输出电压大小,另外DCDC输出的电压可能有偏差,通过TRIM值可以调节精度。SOC

2021-11-08 12:36:06 20

20 在本文中,我们检查了扫描压缩确实有助于减少 ASIC 设计中的测试时间 (DFT),但扫描通道减少也是一种有助于顶层测试时间的方法。

2022-06-02 14:25:09 1504

1504

在市场上所有的电子设计自动化 (EDA) 工具中,可测试设计 (DFT) 可能是最不被重视的。即使在设计阶段将可测试性构建到芯片中也会显着降低高昂的测试成本。根据最近的分析,在制造后测试一批芯片以确定哪些部件没有制造缺陷的成本已达到制造芯片成本的 40% 的惊人阈值。

2022-08-22 14:26:30 732

732

高级测试设计 (DFT) 技术通过提高顺序翻牌的可控性和可观察性,提供高效的测试解决方案,以应对更高测试成本、更高功耗、测试面积和较低几何尺寸下的引脚数。这反过来又提高了SoC的良率,可靠性和可测试性是当今ASIC世界的重要因素。

2022-11-23 14:53:53 672

672

在本篇白皮书中,我们介绍了一个典型设计的 DFT 组件,并提出了多种可大幅改善 DFT 项目进度的智能 DFT 方法。我们展示了如何将结构化 DFT 和即插即用原则用于 DFT 基础结构,来支持与其他设计开发工作相似的并行 DFT 开发和集成。

2022-11-30 10:15:00 575

575 相信很多ICer们在Light芯片的过程中无论前后端都听过DFT设计测试,DFT全称Design for Test(即可靠性设计),众所周知,测试的目的是为了保证芯片成品的质量以及功能逻辑的可靠性的必须 措施。

2023-03-06 14:45:10 2413

2413 DFT是确保芯片在制造过程中具有可测试性的一种技术。DFT友好的ECO是指在进行ECO时, 不会破坏芯片的DFT功能或降低DFT覆盖率的设计方法。

2023-03-06 14:47:07 1371

1371 测试SoC芯片需要专业的测试设备、软硬件工具和测试流程,同时需要一定的测试经验和技能。并且在测试过程中需要注意安全问题,避免对芯片造成损坏。

2023-05-03 08:26:00 3600

3600 DFT是确保芯片在制造过程中具有可测试性的一种技术。DFT友好的ECO是指在进行ECO时, 不会破坏芯片的DFT功能或降低DFT覆盖率的设计方法。DFT不友好的ECO会对芯片的测试和调试带来很大的困难,可能导致芯片测试效率降低甚至无法测试。

2023-05-05 15:06:37 1262

1262

AI芯片和SoC芯片都是常见的芯片类型,但它们之间有些区别。本文将介绍AI芯片和SoC芯片的区别。

2023-08-07 17:38:19 2103

2103 景芯SoC项目是个付费培训项目,项目数据在服务器上。景芯SoC在tessent完成edt occ插入并且仿真OK后,去综合,然后做scan chain insertion就一堆error S1,首先是28个S1 violation报告出来,

2023-08-09 10:11:32 1398

1398

随着半导体技术的飞速发展,系统级芯片(SoC)设计已成为现代电子设备中的主流。在SoC设计中,可测试性设计(DFT)已成为不可或缺的环节。DFT旨在提高芯片测试的效率和准确性,确保产品质量和可靠性。

2023-09-02 09:50:10 1513

1513 DFT PLL向量,ATE怎么用? 自动测试设备(ATE)对PLL(锁相环)进行测试时,我们首先要明白PLL在系统级芯片(SoC)中的重要性。它是SoC中关键的时钟或信号同步部件,其性能直接影响

2023-10-30 11:44:17 662

662

DFT全称为Design for Test,可测性设计。就是说我们设计好一个芯片后,在仿真时可能99%的用例都通过了,怎么保证流片出来的实际芯片也能正常工作呢?

2023-12-06 15:02:43 405

405 SOC ( System on Chip)是在同一块芯片中集成了CPU、各种存储器、总线系统、专用模块以及多种l/O接口的系统级超大规模集成电路。

由于SOC芯片的规模比较大、内部模块的类型以及来源多样,因此SOC芯片的DFT面临着诸多问题。

2023-12-22 11:23:51 503

503

近日,谷歌在半导体委外策略上迎来了一次重大转变,其自研手机系统单芯片(SoC)“Tensor”首次释出测试订单给台湾的京元电。这一举动打破了以往与三星合作的统包晶圆代工与封测的模式。

2024-01-18 15:28:00 299

299

电子发烧友App

电子发烧友App

评论