日前,德州仪器(TI)宣布推出全新系列的时钟发生器,此次推出的产品可提供100飞秒(fs)的超低抖动以及灵活独特的引脚控制选项。与传统的参考时钟解决方案相比,此次推出的新型时钟发生器所具备的抖动性能可让系统设计人员优化系统定时容限和误码率(BER),以减少数据传输错误。

2015-10-12 13:54:03 3205

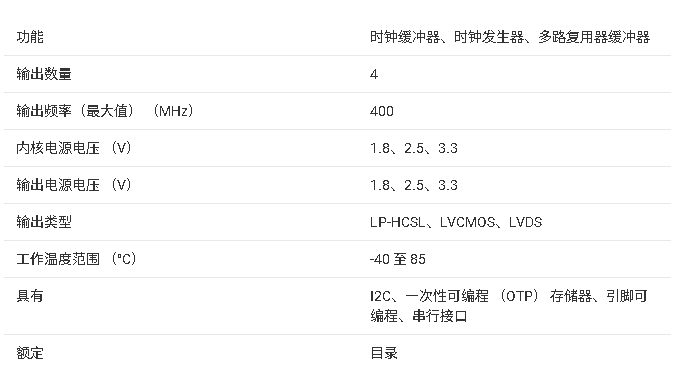

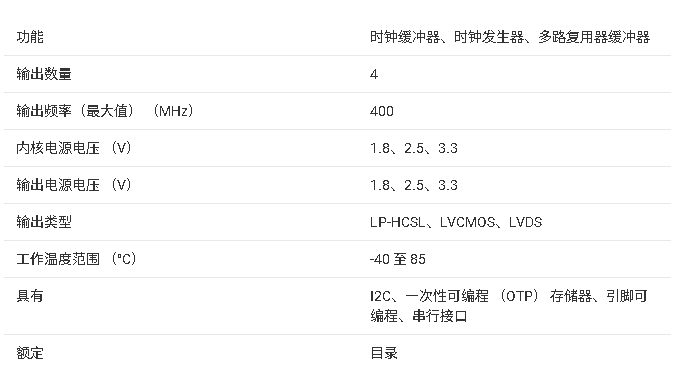

3205 业界领先的全新 1.8V 版 VersaClock® 3S 可编程时钟发生器,为消耗品和计算系统创造具有竞争力的性能、能耗和灵活性。

2017-09-28 10:15:46 9025

9025 德州仪器(TI)日前宣布推出一款具有业界最佳抖动性能的高度集成的时钟发生器。LMK03806可以帮助设计人员运用一个低成本晶体合成所需的时钟频率

2011-10-10 09:19:30 3063

3063 转换器应用的需求,搭配ADI高速ADC器件使用可获得良好的性能。这些时钟发生器以及ADI的时钟分配产品和ADC可以组合起来,打造超高性能的时序解决方案。这些产品可以通过公司网站订购,数据手册也可通过 www.analog.com/cn 获取。

2018-10-18 11:29:03

概述:AD9577是一款既提供一个多路输出时钟发生器功能,又带有两个片上锁相环内核PLL1和PLL2,专门针对网络时钟应用而优化。PLL设计基于ADI公司成熟的高性能、低抖动频率合成器产品系列,确保实现最高的网

2021-04-06 06:49:57

系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。然而,如果不慎重考虑时钟发生器的相位噪声和抖动性能,数据转换器动态范围和线性度性能可能受到严重的影响。

2019-07-30 07:57:42

输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。 产品名称:时钟发生器 AD9520-3BCPZ特征低相位噪声、锁相环(PLL)片内VCO的调谐频率范围为

2019-07-09 11:50:41

(LVDS工作模式) AD9571ACPZPEC产品详情AD9571具有多路输出时钟发生器功能,内置专用PLL内核,针对以太网线路卡应用进行了优化。整数N PLL设计基于ADI公司成熟的高性能、低抖动

2019-07-09 10:19:09

AKD8140A Ver.2,AK8140A可编程多时钟发生器评估板。评估抖动性能和功能很容易

2020-07-27 15:01:46

串行时钟发生器用来产生 I2C 通信的波特率时钟 SCL。串行时钟发生器采用 PCLK 作为输入时钟,通过 1 个 8bit的计数器计数,输出所需波特率的 I2C 时钟信号。

SCL 时钟频率计

2025-12-15 07:26:02

串行时钟发生器用来产生 I2C 通信的波特率时钟 SCL。串行时钟发生器采用 PCLK 作为输入时钟,通过 1 个 8bit的计数器计数,输出所需波特率的 I2C 时钟信号。

SCL 时钟频率计

2025-12-08 08:16:31

我要做毕业设计 叫 基于lmk03806的高性能可编程时钟发生器的设计与fpga实现,需要有protel 99se画 lmk03806的原理图和fpga的配置电路,用vhdl编程仿真,用fpga来配置lmk03806,求高手求助{:1:}

2013-05-03 23:06:27

AD9576 / PCBZ,AD9576评估板提供多输出时钟发生器功能,包括两个专用锁相环(PLL)内核,具有灵活的频率转换功能,经过优化,可作为整个系统的强大异步时钟源,提供扩展功能通过监控和冗余

2019-02-25 09:40:01

描述TIDA-00597 可为时钟发生器提供噪声非常低的输出电源。主要特色低噪声,适用于时钟发生器输出电流高达 800mA低相位噪声输出功率启用和禁用

2018-08-22 07:43:40

TIDA-00597 可为时钟发生器提供噪声非常低的输出电源。

2009-05-07 15:12:41 0

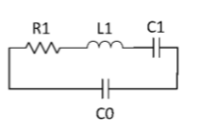

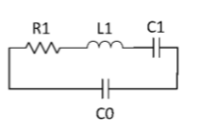

0 针对直接数字频率合成(DDS)和集成锁相环(PLL)技术的特性,提出了一种新的DDS 激励PLL 系统频率合成时钟发生器方案。且DDS 避免正弦查找表,即避免使用ROM,采用滤波的方法

2009-12-14 10:22:00 36

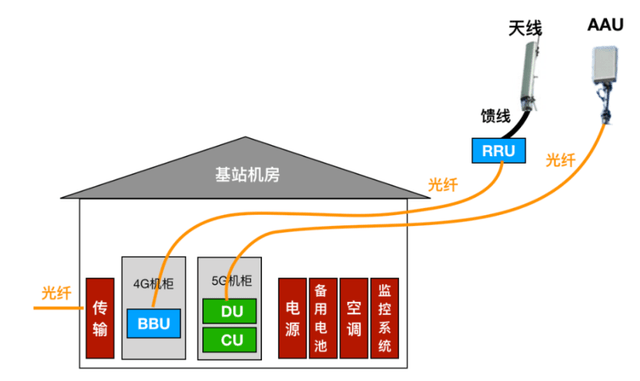

36 AC1571 是用于 5G 基站应用的基于 PLL的时钟发生器,该芯片采用全数字锁相环技术,以实现最佳的高频低相噪性能,并具有低功耗和高PSRR能力。典型应用场景:· 无线基站·

2023-12-12 14:25:17

时钟发生器芯片厂家 时钟芯片是一种基于PLL的时钟发生器,采用ADPLL(全数字锁相环)技术,以实现的高频低相噪性能,并具备低功耗和高PSNR能力,可实现小于0.3ps RMS的相位抖动性能

2023-12-29 09:29:50

时钟发生器芯片厂家 时钟芯片是一种基于PLL的时钟发生器,采用ADPLL(全数字锁相环)技术,以实现的高频低相噪性能,并具备低功耗和高PSNR能力,可实现小于0.3ps RMS的相位抖动性能

2024-02-04 11:41:14

MAX9489/MAX9471多输出时钟发生器构建集成时钟源

摘要:与典型的“本地”时钟方案相比,集成的多输出时钟发生器有许多优势。本文探讨了集中时钟发生器(如

2008-10-04 20:43:25 1179

1179

Si5338 业界首个任意频率、任意输出的时钟发生器

高性能模拟与混合信号领导厂商Silicon Laboratories日前发表全新的时钟发生器和缓冲器系列,可为业

2008-11-10 09:39:44 2208

2208

精密时钟发生器电路图

2009-03-25 09:35:22 1456

1456

振荡器时钟发生器电路图

2009-04-13 08:54:22 934

934

摘要:MAX9450/MAX9451/MAX9452是集成了VCXO,具有相同PLL内核和三种不同输出(LVPECL, HSTL,LVDS)的高精度时钟发生器。MAX945x时钟发生器具有四个主要的特点:集成VCXO,工作频率范围宽,PLL

2009-04-22 09:42:01 1345

1345

摘要:与典型的“本地”时钟方案相比,集成的多输出时钟发生器有许多优势。本文探讨了集中时钟发生器(如MAX9489和MAX9471)的优点,如:降低系统成本、良好的信号完整性、抑制干

2009-04-22 10:11:53 538

538

摘要:与典型的“本地”时钟方案相比,集成的多输出时钟发生器有许多优势。本文探讨了集中时钟发生器(如MAX9489和MAX9471)的优点,如:降低系统成本、良好的信号完整性、抑制干

2009-05-03 11:07:05 852

852

AC1571 是用于 5G 基站应用的基于 PLL的时钟发生器,该芯片采用全数字锁相环技术,以实现最佳的高频低相噪性能,并具有低功耗和高PSRR能力。典型应用场景:· 无线基站·

2025-11-11 16:43:24

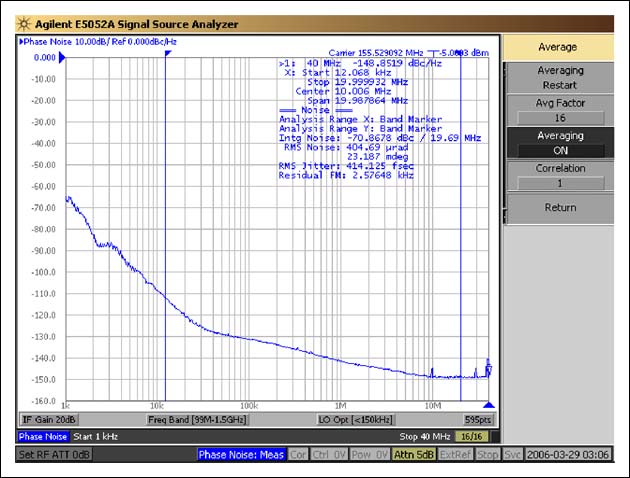

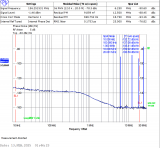

评估低抖动PLL时钟发生器的电源噪声抑制性能

本文介绍了电源噪声对基于PLL的时钟发生器的干扰,并讨论了几种用于评估确定性抖动(DJ)的技术方案。推导出的关系式提

2009-09-18 08:46:32 1854

1854

Maxim推出高性能、三路输出时钟发生器MAX3625B

Maxim近日推出高性能、三路输出时钟发生器MAX3625B,适用于以太网和光纤通道网络设备。器件采用低噪声VCO和PLL架构,能够

2009-12-14 17:25:04 1254

1254 MAX3625B 抖动仅为0.36ps的PLL时钟发生器

概述

MAX3625B是一款低抖动、精密时钟发生器,优化用于网络设备。器件内置晶体振荡器和锁相环(PLL)

2010-03-01 08:56:18 1616

1616

MAX3679A高性能四路输出时钟发生器(Maxim)

Maxim推出用于以太网设备的高性能、四路输出时钟发生器MAX3679A。器件采用低噪声

2010-04-14 16:51:49 1151

1151 如何利用GPS OEM来进行二次开发,产生高精度时钟发生器是一个研究的热点问题。在电力系统、CDMA2000、DVB、DMB等系统中,高精度的GPS

2010-07-24 15:45:26 944

944 德州仪器(TI)(纽约证券交易所代码:TXN)今天宣布推出一款具有业界最佳抖动性能的高度集成的时钟发生器。LMK03806可以帮助设计人员运用一个低成本晶体合成所需的时钟频率,从而

2011-10-08 11:36:42 1062

1062 MAX3636是一个高度灵活,高精度锁相环(PLL)时钟发生器为下一代网络设备的要求低抖动时钟发生器和强大的高速数据传输的分布进行了优化。

2011-10-11 11:15:22 1699

1699

Pericom推出一项全新的HiFlex时钟发生器产品系列,该系列产品可提供多频率输出,同时具有超低噪声(抖动)、高集成度及高灵活性的特点,完美地适用于网络、云计算和其他需要多频率及输出的高性能平台。

2013-01-29 09:14:04 2898

2898 双环路时钟发生器可清除抖动并提供多个高频输出

2016-01-04 17:41:13 0

0 10GHz扩频时钟发生器的设计_胡帅帅

2017-01-07 21:28:58 1

1 系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。然而,如果不慎重考虑时钟发生器、相位噪声和抖动性能,数据转换器、动态范围和线性度性能可能受到严重的影响。

2017-11-17 02:00:58 1249

1249

Microchip基于MEMS的时钟发生器

2018-06-07 13:46:00 5526

5526

Microchip基于MEMS的时钟发生器

2018-07-08 01:23:00 4893

4893 据麦姆斯咨询报道,Microchip推出了业界尺寸最小的MEMS时钟发生器DSC613。这款新器件可在电路板上最多替换掉三个晶振和振荡器,从而减少高达80%的时钟元件布板空间。

2018-11-15 16:38:26 4926

4926 AD9523:14路LVPECL/LVDS/HSTL输出 或29路LVCMOS输出 低抖动时钟发生器

2019-07-04 06:18:00 4965

4965 TI推出超低抖动时钟发生器,以实现更可靠的电信基础设施设备,设计人员可以优化系统性能,简化设备配置并减少设计周期时间。

2019-08-09 15:10:28 2668

2668 系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。

2019-08-07 17:51:43 7378

7378

系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。然而,如果不慎重考虑时钟发生器的相位噪声和抖动性能,数据转换器动态范围和线性度性能可能受到严重的影响。

2020-11-22 11:34:38 3555

3555

AD9525: 8路LVPECL输出低抖动时钟发生器

2021-03-21 15:00:20 0

0 AD9540:655 MHz低抖动时钟发生器数据表

2021-03-22 19:57:57 0

0 AD9518-3:6输出时钟发生器,集成2.0 GHz压控振荡器数据表

2021-04-13 11:13:25 2

2 AD9517-0:12输出时钟发生器,集成2.8 GHz压控振荡器数据表

2021-04-13 12:10:21 0

0 ADF4360-9:集成压控振荡器数据表的时钟发生器PLL

2021-04-14 14:10:44 0

0 AD9571:以太网时钟发生器,10个时钟输出

2021-04-16 10:21:56 3

3 AD9548:四/八路输入网络时钟发生器/同步器数据表

2021-04-16 11:41:04 10

10 AD9520-5:12 LVPECL/24 CMOS输出时钟发生器数据表

2021-04-27 21:31:55 2

2 AD9516-5:14-输出时钟发生器数据表

2021-04-27 21:41:19 5

5 AD9551:多业务时钟发生器数据表

2021-04-28 10:30:52 0

0 AD9522-5:12 LVDS/24 CMOS输出时钟发生器数据表

2021-04-28 10:53:01 0

0 AD9547:双/四输入网络时钟发生器/同步器数据表

2021-04-30 08:48:14 10

10 AN-1576:采用AD9958 500 MSPS DDS或AD9858 1 GSPS DDS和AD9515时钟分配IC的高性能ADC的低抖动采样时钟发生器

2021-04-30 09:48:42 14

14 AD9517-4:12输出时钟发生器,集成1.6 GHz压控振荡器数据表

2021-04-30 15:51:42 10

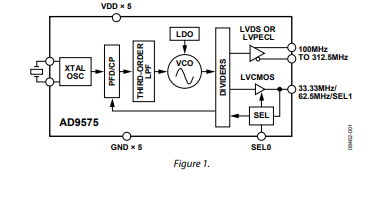

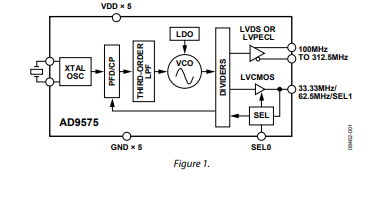

10 AD9575:网络时钟发生器,双输出数据表

2021-05-09 11:06:44 1

1 AD9531:3通道时钟发生器,24输出数据表

2021-05-15 15:24:07 11

11 AD9576:双锁相环异步时钟发生器数据表

2021-05-16 12:57:55 0

0 超低抖动时钟发生器和分配器最大限度地提高数据转换器的信噪比

2021-05-18 20:57:30 0

0 AD9517-0 12输出时钟发生器,集成2.8 GHz压控振荡器数据表

2021-06-16 12:14:49 4

4 集成2.0 GHz压控振荡器数据表的AD9518-3 6输出时钟发生器

2021-06-17 15:38:27 3

3 集成2.5 GHz压控振荡器数据表的AD9517-1 12输出时钟发生器

2021-06-17 15:57:38 6

6 时钟发生器AD9516-0技术手册

2022-01-25 15:59:42 8

8 。Cypress时钟发生器兼容大量增值性能,如VCXO,扩频和输出相位校准,及其兼容流行接口标准的参考时钟/3.0,如PCIe1.0/2.0/3.0、10GbE、SATA1.0/2.0和USB1.0

2022-04-22 09:02:09 1314

1314 这是带有板上芯片(COB)的1Hz时钟发生器电路。通常,为数字时钟和计数器电路应用产生1Hz时钟的电路将IC与晶体和微调电容器等结合使用。

2022-06-07 10:43:50 3856

3856

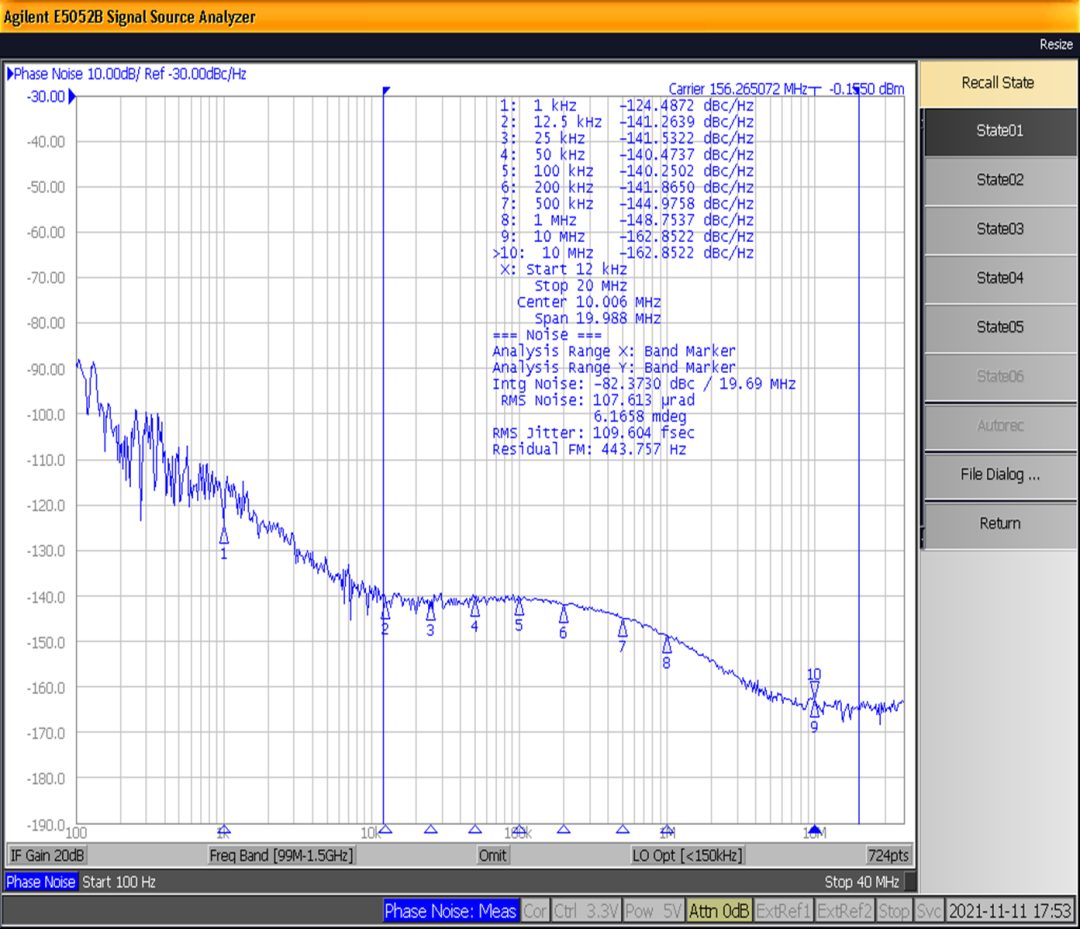

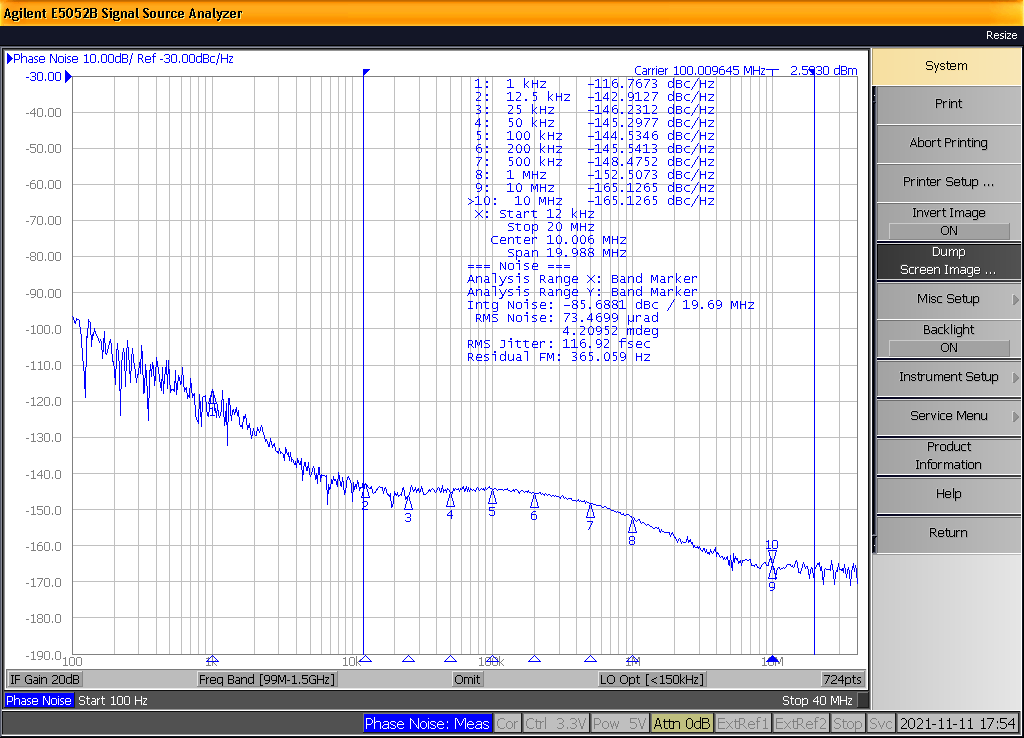

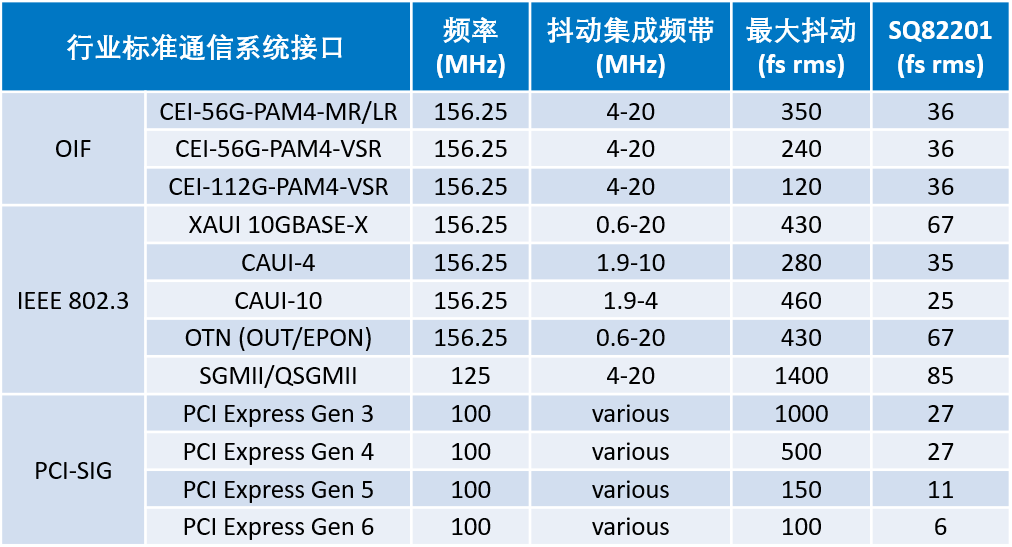

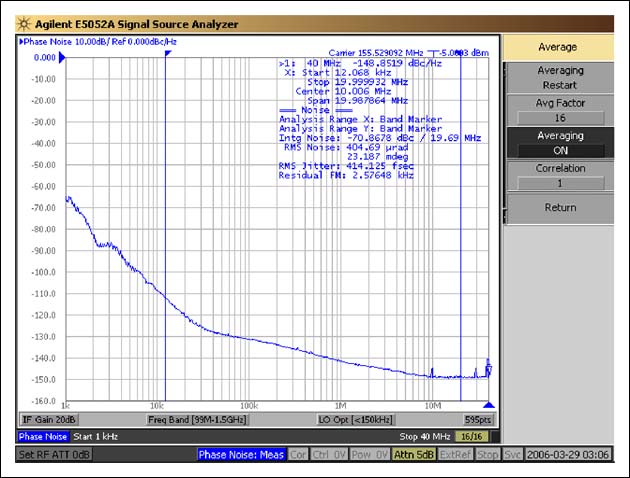

超低抖动时钟发生器如何优化串行链路系统性能

2022-11-04 09:50:15 0

0 9ZXL1951D PCIe 时钟发生器评估板用户指南

2023-03-21 19:21:13 1

1 本文讨论电源噪声干扰对基于PLL的时钟发生器的影响,并介绍几种用于评估由此产生的确定性抖动(DJ)的测量技术。派生关系显示了如何使用频域杂散测量来评估时序抖动行为。实验室台架测试结果用于比较测量技术,并演示如何可靠地评估参考时钟发生器的电源噪声抑制(PSNR)性能。

2023-04-11 11:06:39 2462

2462

CLG5908是一颗高性能的任意频率任意输出格式通用时钟发生器,可以支持1~750M任意频点输出,频率精度 < 0.001 PPM,并且jitter性能优越,通常模式下RMS jitter<200fs,同时支持Down-Spread和Center-Spread SSC。

2023-04-23 14:43:12 2036

2036

9ZXL1951D PCIe 时钟发生器评估板用户指南

2023-07-07 19:19:11 0

0 时钟发生器由哪些部分组成?锁相环pll的特点是什么?如何用硬件配置pll 时钟发生器是指通过特定的电路设计产生适合各种电子设备使用的时钟信号的器件。时钟发生器由多个部分组成,其中最核心的是锁相环

2023-10-13 17:39:50 2233

2233 时钟合成器和时钟发生器是两种用于产生时钟信号的电子器件,它们在功能和应用上有一些区别。

2023-11-09 10:26:56 1541

1541 的时钟发生器件的选择上往往少有考虑。目前市场上有性能属性大相径庭的众多时钟发生器。然而,如果不慎重考虑时钟发生器、相位噪声和抖动性能,数据转换器、动态范围和线性度性能可能受到严重的影响。...

2023-11-28 14:33:57 0

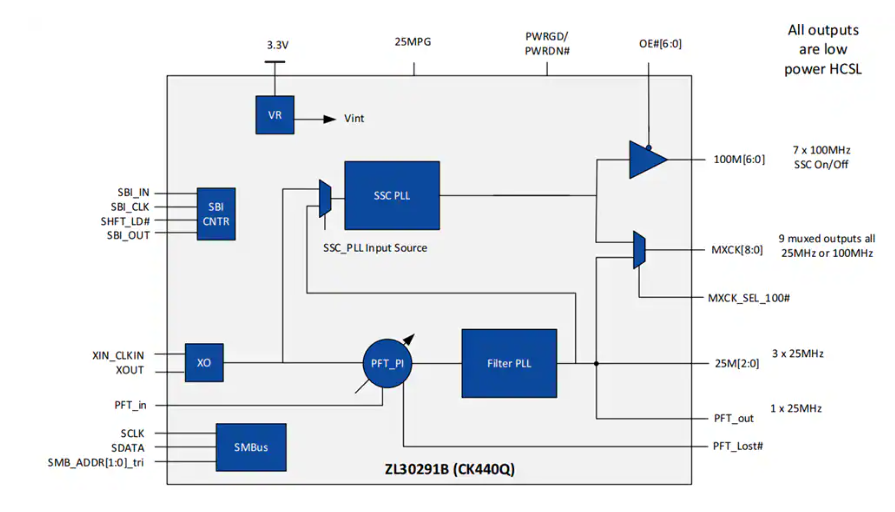

0 “核芯互联CLG440是一颗专为高性能服务器、计算中心应用推出的支持PCIe 6.0、符合CK440Q标准的高性能时钟发生器。

2024-01-16 15:57:40 2049

2049

核芯互联近日发布了一款专为高性能服务器和计算中心应用打造的支持PCIe 6.0的高性能时钟发生器——CLG440。这款产品符合CK440Q标准,旨在满足下一代服务器和数据中心的需求。

2024-01-16 16:09:07 2131

2131 电子发烧友网站提供《CDCE6214超低功率时钟发生器数据表.pdf》资料免费下载

2024-02-28 15:38:40 0

0 电子发烧友网站提供《CDCE62002高性能时钟发生器数据表.pdf》资料免费下载

2024-08-21 11:11:25 0

0 电子发烧友网站提供《CDCE62005高性能时钟发生器和分配器数据表.pdf》资料免费下载

2024-08-21 11:12:13 0

0 电子发烧友网站提供《LMK05318B超低抖动时钟发生器数据表.pdf》资料免费下载

2024-08-21 10:03:58 0

0 电子发烧友网站提供《CDCS501 SSC时钟发生器/缓冲器数据表.pdf》资料免费下载

2024-08-22 10:05:11 0

0 电子发烧友网站提供《CDC421Axxx高性能低相位噪声时钟发生器数据表.pdf》资料免费下载

2024-08-23 10:38:44 0

0 高性能抖动衰减器和时钟发生器的推荐晶体、TCXO和OCXO参考手册本文档的目的是提供一份经过测试并符合SiliconLabs高性能抖动使用条件的晶体、TCXO和OCXO清单衰减器和时钟发生器。对本

2024-11-06 14:40:33 1513

1513

时钟发生器,作为一种关键的电子设备,负责生成精确且稳定的时钟信号。这些信号在各类电子系统中作为时间基准,确保系统的正常运行和性能。本文将深入探讨时钟发生器的定义、工作原理、特点及其在实际应用中的广泛案例,以期为相关领域的研究者和工程师提供全面的技术参考。

2025-02-05 17:17:34 1712

1712 中国领先的时钟解决方案提供商——核芯互联,正式发布CLG5908集成MEMS硅振荡器版本CLG5908M。作为国内首颗集成MEMS硅振荡器的高性能任意时钟发生器,这一全新版本在原有CLG5908

2025-03-05 17:17:43 1716

1716

AD9575是一款高度集成的双路输出时钟发生器,包括一个针对网络定时而优化的片内PLL内核。整数N分频PLL设计基于ADI公司成熟的高性能、低抖动频率合成器系列,可实现线路卡的较高性能。对相位噪声和抖动要求苛刻的其它应用也能受益于该器件。

2025-04-10 17:00:26 962

962

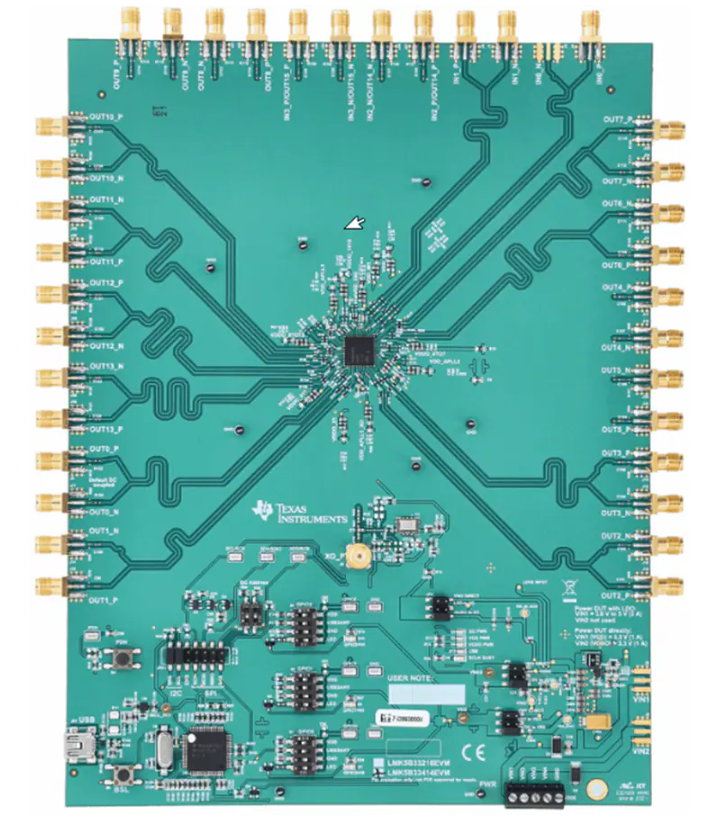

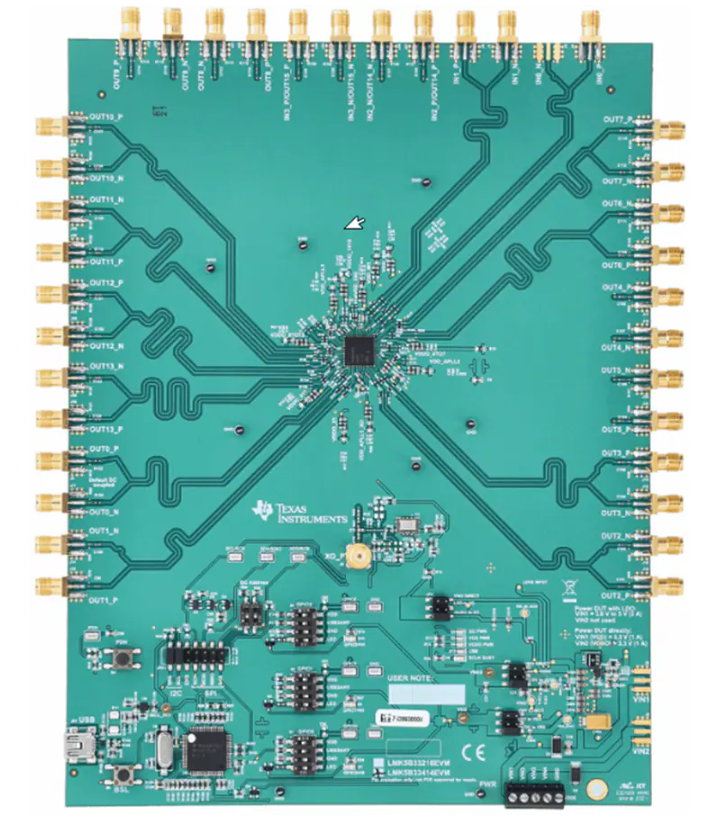

Texas Instruments LMK5B33414EVM时钟发生器和合成器评估模块 (EVM) 是一个用于对LMK5B33414网络时钟发生器和同步器进行器件评估、合规性测试和系统原型设计的平台。

2025-09-08 15:03:16 684

684

LMK3H2104 是一款基于 BAW 的时钟发生器,不需要任何外部 XTAL 或 XO。该器件可用作PCIe时钟发生器或通用时钟发生器。2 个 FOD(分数输出分频器)同时提供频率灵活性、低功耗

2025-09-10 09:21:33 713

713

CDCE62002器件是一款高性能时钟发生器,具有低输出抖动、 通过SPI接口实现高度可配置,并确定可编程启动模式 通过片上EEPROM。专为时钟数据转换器和高速数字量身定制 信号,CDCE62002实现低于0.5 ps RMS的抖动性能 ^(1)^ .

2025-09-17 13:48:23 647

647

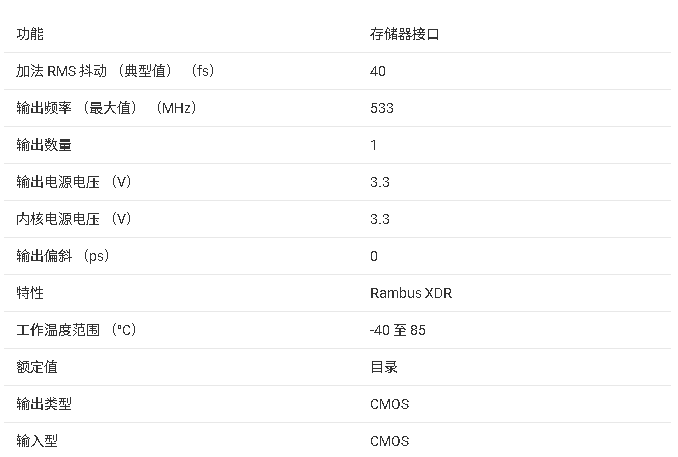

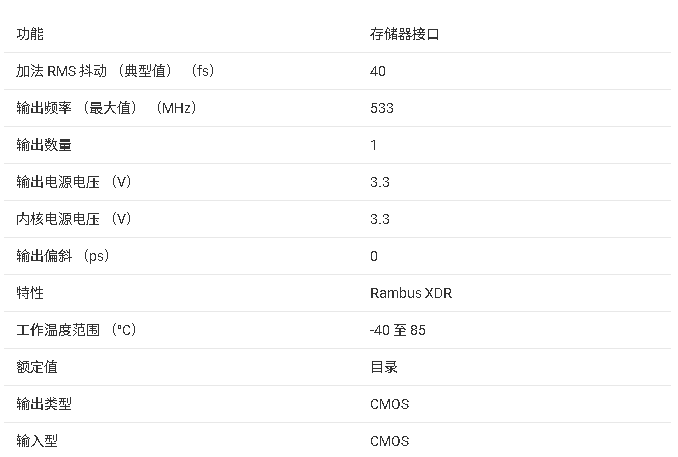

直接串斗时钟发生器 (DRCG) 提供必要的时钟信号以支持 直接串斗 内存子系统。它包括将直接 Rambus 通道时钟同步到外部系统的信号,或者 处理器时钟。它旨在支持台式机、工作站、服务器和移动

2025-09-19 15:22:20 701

701

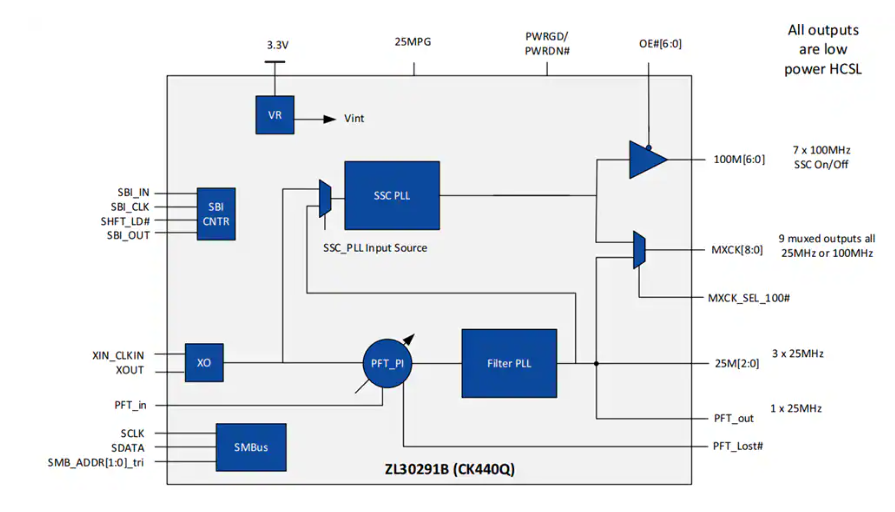

Microchip Technology ZL30291B时钟发生器完全符合Intel CK440Q标准。超低抖动、低功耗时钟发生器采用3.3V±10%电源供电,符合PCIe机电规格,该规格要求3.3V电源容差为 ±9%。

2025-09-28 14:23:38 608

608

随着科技的进步,电子设备对时钟信号的要求愈发严格,而时钟发生器作为提供这些关键信号的核心组件,其性能直接影响到整个系统的稳定与效率。本文将深入探讨时钟发生器的竞争优势,揭示其在激烈市场竞争中脱颖而出

2025-10-23 17:20:30 495

495

深入剖析RC2121xA:高性能汽车可编程时钟发生器的卓越之选 在汽车电子领域,时钟发生器的性能和可靠性直接影响着整个系统的稳定性和运行效率。今天,我将深入剖析Renesas的RC2121xA系列

2025-12-29 09:55:03 81

81 深入解析RC22112A FemtoClock时钟发生器:高性能与低功耗的完美结合 在高速数据传输和精密时钟同步的领域中,时钟发生器的性能直接影响着整个系统的稳定性和数据处理能力。Renesas

2025-12-29 15:45:06 93

93

电子发烧友App

电子发烧友App

评论