直接串斗时钟发生器 (DRCG) 提供必要的时钟信号以支持 直接串斗 内存子系统。它包括将直接 Rambus 通道时钟同步到外部系统的信号,或者 处理器时钟。它旨在支持台式机、工作站、服务器和移动设备上的 Direct Rambus 内存 PC 主板。DRCG 还为各种 Direct Rambus 存储器提供现成的解决方案 应用。

DRCG 为 Direct Rambus 存储器子系统提供时钟倍增和相位对齐,以启用 Rambus 通道和 ASIC 时钟域之间的同步通信。在直达 Rambus 中 存储器子系统,系统时钟源为 DRCG 提供 REFCLK 和 PCLK 时钟参考,并 内存控制器。DRCG 将 REFCLK 相乘并将高速 BUSCLK 驱动到 RDRAM 和内存控制器。存储器控制器中的齿轮比逻辑将PCLK和BUSCLK频率分开 通过比率 M 和 N,使得 PCLKM = SYNCLKN,其中 SYNCLK = BUSCLK/4。DRCG 检测相位 PCLKM 和 SYNCLKN 之间的差异,并调整 BUSCLK 的相位,使 PCLKM 和 SYNCLKN 最小化。这允许跨 SYNCLK/PCLK 边界传输数据 不会产生额外的延迟。

*附件:cdcfr83a.pdf

用户控制由乘法和模式选择端子提供。多码端子提供一种选择 四个时钟频率乘法比,生成范围为 267 MHz 至 533 MHz 的 BUSCLK 频率,具有 时钟基准范围为 33 MHz 至 100 MHz。模式选择端子可用于选择旁路 模式下,频率乘法参考时钟直接输出到 Rambus 通道,适用于以下系统: 不需要 Rambus 时钟和系统时钟之间的同步。测试模式提供给 旁路Rambus通道上的PLL和输出REFCLK,并将输出置于高阻抗状态 用于电路板测试。

该CDCFR83A具有故障安全上电初始化状态机,支持在所有 通电条件。

该CDCFR83A的特点是在 –40°C 至 85°C 的自由空气温度下运行。

特性

- 用于直接Rambus™存储系统的533 MHz差分时钟源,数据传输速率为1066 MHz

- 故障安全上电初始化

- 将 Rambus 通道的时钟域与外部系统或处理器时钟同步

- 三种电源工作模式可最大限度地降低移动和其他功耗敏感型应用的功耗

- 采用3.3 V单电源供电,300 MHz(典型值)时为120 mW

- 采用收缩小外形封装 (DBQ) 封装

- 支持倍频器:4、6、8、16/3

- PLL 无需外部元件

- 支持独立通道时钟

- 扩频时钟跟踪功能可降低 EMI

- 设计用于 TI 的 133MHz 时钟合成器 CDC924 和 CDC921

- 533 MHz时周期抖动小于40 ps

- 经 Gigatest Labs 认证,超过 Rambus DRCG 验证要求

- 支持–40°C至85°C的工业温度范围

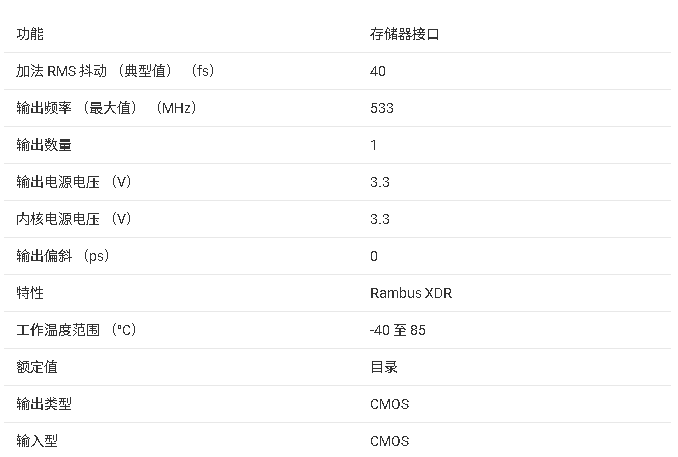

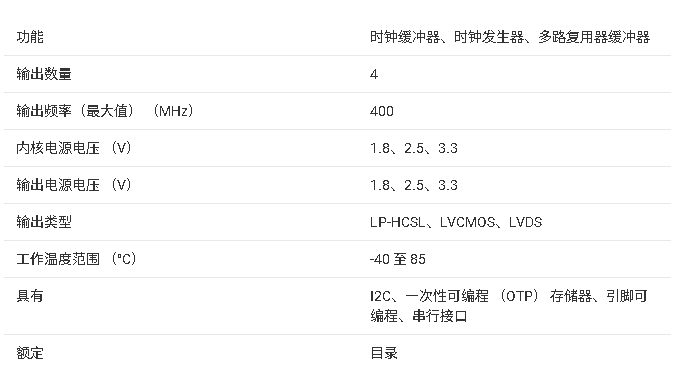

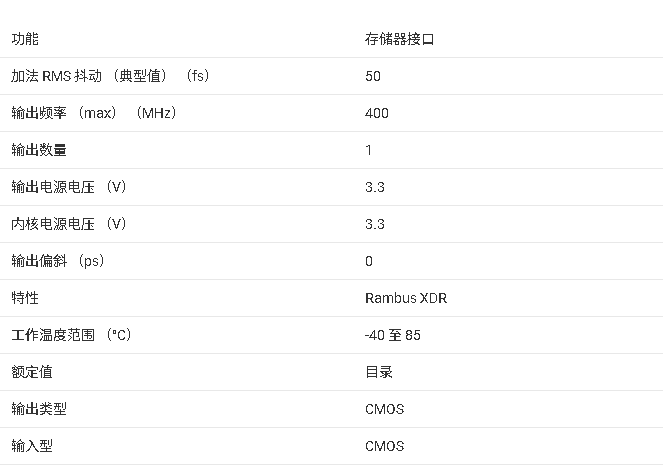

参数

1. 产品概述

CDCR83A 是一款专为 Direct Rambus™ 内存系统 设计的时钟发生器(DRCG),主要用于台式机、工作站、服务器和移动PC主板。其核心功能是提供高频差分时钟信号,支持 800MHz 数据传输速率,并同步 Rambus 通道与外部系统/处理器时钟域。

2. 关键特性

- 高性能时钟:400MHz 差分时钟输出,支持 800MHz 数据传输。

- 低功耗设计:三种电源模式,适用于移动设备(典型功耗 120mW @300MHz)。

- 集成化设计:无需外部 PLL 组件,支持 4/6/8/16/3 倍频。

- 抗干扰能力:支持扩频时钟跟踪(减少 EMI),工业级温度范围(-40°C~85°C)。

- 认证标准:通过 Gigatest Labs 认证,满足 Rambus DRCG 验证要求。

3. 功能描述

- 时钟同步:通过 REFCLK 和 PCLK 输入,生成 BUSCLK 驱动 RDRAM 和内存控制器。

- 相位对齐:检测 PCLKM 与 SYNCLKN 的相位差,确保内存子系统同步通信。

- 多场景支持:兼容 TI 的 133MHz 时钟合成器(CDC924/CDC921)。

4. 封装与引脚

- DBQ 封装(24 引脚),包含电源(VDD)、地线(GND)、时钟输入/输出(REFCLK/CLK/CLKB)及模式控制引脚(S0-S2、MULT0-MULT1)。

5. 应用场景

适用于需要高速内存同步的 Rambus 内存子系统,如高性能计算、移动设备等。

-

存储器

+关注

关注

39文章

7753浏览量

172157 -

服务器

+关注

关注

14文章

10344浏览量

91737 -

内存

+关注

关注

9文章

3231浏览量

76496 -

时钟发生器

+关注

关注

1文章

357浏览量

70160 -

时钟信号

+关注

关注

4文章

509浏览量

30077

发布评论请先 登录

MAX3679A高性能四路输出时钟发生器(Maxim)

Cypress时钟发生器的分类,它有哪些应用

LMK3H2104 4-Output PCIe时钟发生器技术文档总结

探索时钟发生器的竞争优势

CDCFR83A 直接 Rambus™ 时钟发生器文档总结

CDCFR83A 直接 Rambus™ 时钟发生器文档总结

评论