声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADI

+关注

关注

150文章

46086浏览量

270432 -

振荡器

+关注

关注

28文章

4155浏览量

142302 -

时钟发生器

+关注

关注

1文章

268浏览量

69876

发布评论请先 登录

相关推荐

热点推荐

探索时钟发生器的竞争优势

随着科技的进步,电子设备对时钟信号的要求愈发严格,而时钟发生器作为提供这些关键信号的核心组件,其性能直接影响到整个系统的稳定与效率。本文将深入探讨时钟发生器的竞争优势,揭示其在激烈市场

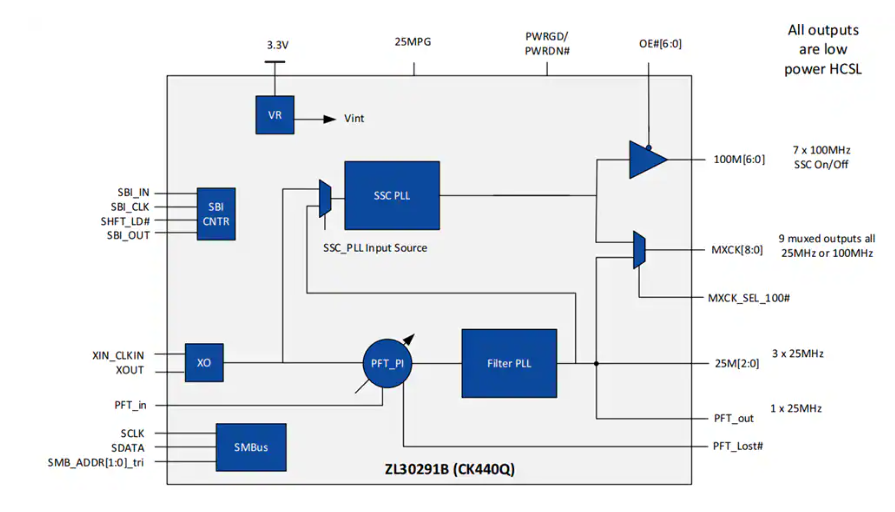

ZL30291B:面向PCIe Gen6与平台时序的高性能时钟发生器

Microchip Technology ZL30291B时钟发生器完全符合Intel CK440Q标准。超低抖动、低功耗时钟发生器采用3.3V±10%电源供电,符合PCIe机电规格,该规格要求3.3V电源容差为 ±9%。

CDCE62005 时钟发生器芯片技术文档总结

CDCE62005是一款高性能时钟发生器和分配器,具有低输出 抖动、通过SPI接口实现高度可配置以及可编程启动模式 由片上EEPROM确定。专为时钟数据转换器和高速定制 数字信号,该C

CDCE62002 四输出时钟发生器/抖动清除器技术文档总结

CDCE62002器件是一款高性能时钟发生器,具有低输出抖动、 通过SPI接口实现高度可配置,并确定可编程启动模式 通过片上EEPROM。专为时钟数据转换器和高速数字量身定制 信号,C

LMK3H2104 4-Output PCIe时钟发生器技术文档总结

LMK3H2104 是一款基于 BAW 的时钟发生器,不需要任何外部 XTAL 或 XO。该器件可用作PCIe时钟发生器或通用时钟发生器。2 个 FOD(分数输出分频器)同时提供频率灵

LMK5B33414EVM网络时钟发生器评估模块技术解析

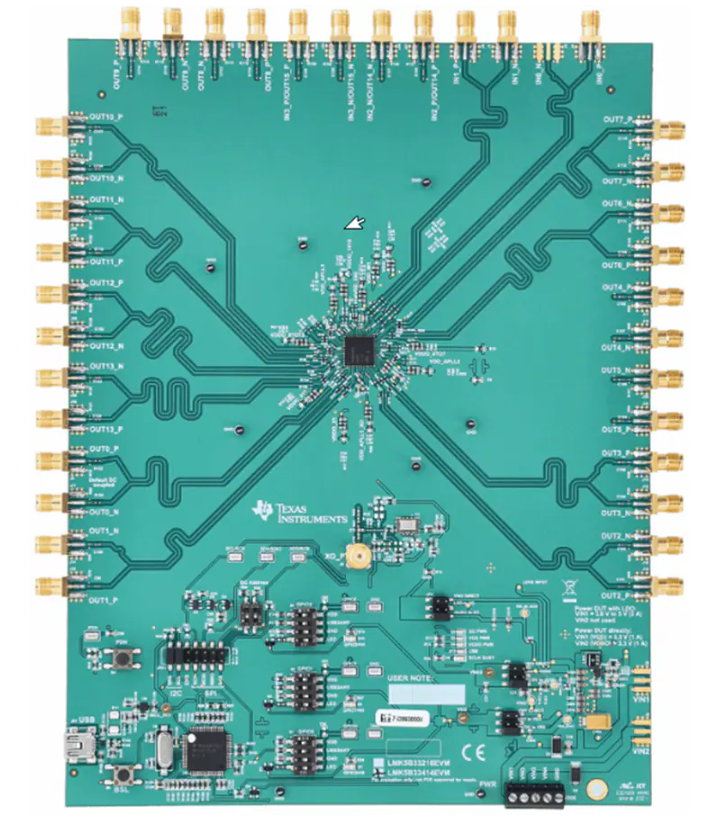

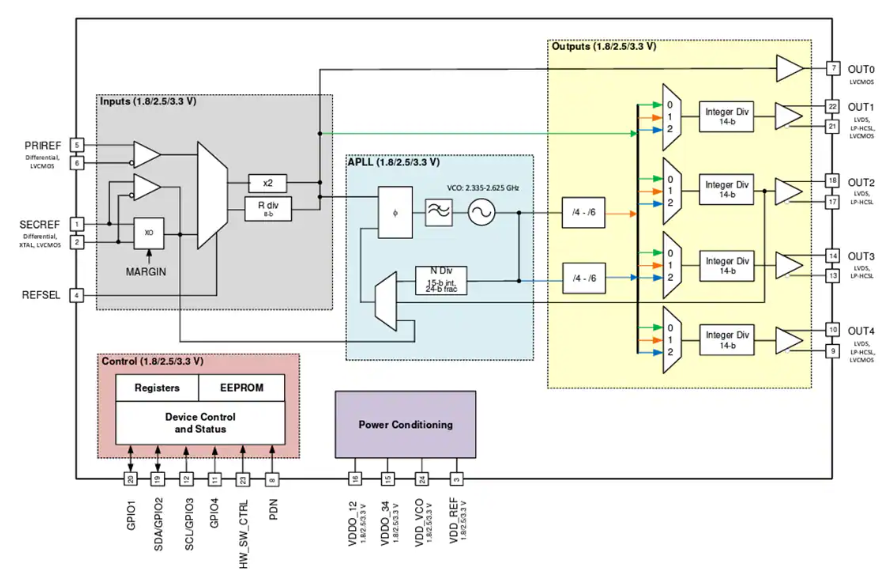

Texas Instruments LMK5B33414EVM时钟发生器和合成器评估模块 (EVM) 是一个用于对LMK5B33414网络时钟发生器和同步器进行器件评估、合规性测试和系统原型设计的平台。

德州仪器CDCE6214Q1TM超低功耗时钟发生器技术解析

Texas Instruments CDCE6214Q1TM超低功耗时钟发生器是是一款适合汽车应用的4通道、中级抖动时钟发生器,可生成五个独立时钟输出。这些输出在各种驱动器模式之间可选

面向5G和GNSS的微型MEMS移动时钟发生器

SiTimeCorporation宣布推出Symphonic,这是其首款移动时钟发生器,零件编号为SiT30100,带有集成的MEMS谐振器。Symphonic为5G和GNSS芯片组提供准确且有弹性

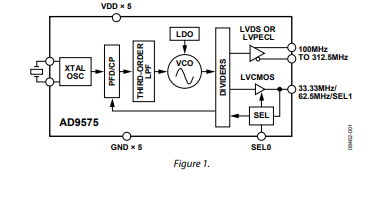

AD9575双路输出网络时钟发生器技术手册

AD9575是一款高度集成的双路输出时钟发生器,包括一个针对网络定时而优化的片内PLL内核。整数N分频PLL设计基于ADI公司成熟的高性能、低抖动频率合成器系列,可实现线路卡的较高性能。对相位噪声和抖动要求苛刻的其它应用也能受益

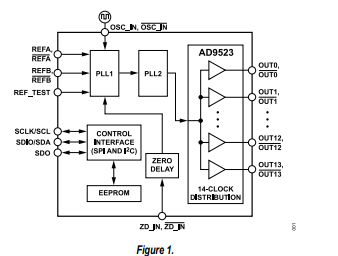

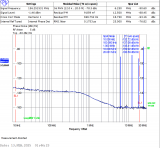

AD9523 14路输出、低抖动时钟发生器技术手册

AD9523提供低功耗、多路输出时钟分配功能,具有低抖动性能,还配有片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为3.6 GHz至4.0 GHz。

核芯互联推出高性能任意时钟发生器CLG5908M

中国领先的时钟解决方案提供商——核芯互联,正式发布CLG5908集成MEMS硅振荡器版本CLG5908M。作为国内首颗集成MEMS硅振荡器的高性能任意

时钟发生器的特点和应用

时钟发生器,作为一种关键的电子设备,负责生成精确且稳定的时钟信号。这些信号在各类电子系统中作为时间基准,确保系统的正常运行和性能。本文将深入探讨时钟发生器的定义、工作原理、

面向Switchtec和数据中心应用的预配置时钟发生器器件编号

电子发烧友网站提供《面向Switchtec和数据中心应用的预配置时钟发生器器件编号.pdf》资料免费下载

发表于 01-15 15:27

•0次下载

AD9523时钟发生器的性能特点及应用分析

AD9523时钟发生器的性能特点及应用分析

评论