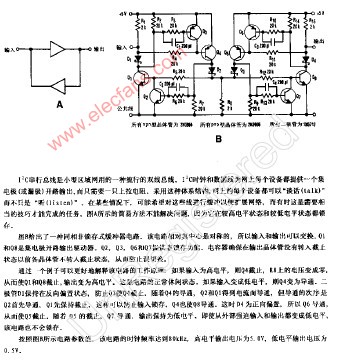

1Hz正弦波振荡器

本电路利用两个运算

2009-10-07 11:44:47 2823

2823

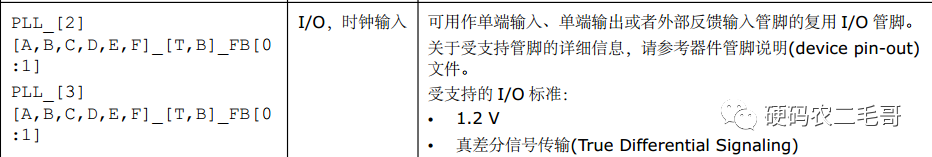

嗨,大家好,我向时钟向导提供50 Mhz输入,并使用MMCM方案生成80 MHz方案。在模拟中,我看到输入时钟和生成的时钟之间存在延迟。这种延迟是什么?有什么办法可以控制这种延迟吗?任何建议都会非常

2019-04-26 13:01:43

,AD9106的输入时钟和我系统的采集卡时钟是同步 的,这样DDS输出的波形就和采集卡的不同步,会导致采集有误差!期待你们帮助!谢谢!另外DDSAD9834也存在这样的问题!

2023-12-13 08:45:46

AD9163的时钟输入范围多大,输入时钟大小与输入数据速率是什么关系?

2023-12-08 08:20:20

如果不对Ad9959进行写操作,sync_clk时钟输出为输入时钟的1/4。但是如果对输入时钟进行放大之后,sync_clk时钟输出不是放大之后的1/4;使用spi,时序都正确。求帮助。

2018-11-12 09:21:24

右对齐方式存储在16位数据寄存器中。模拟看门狗特性允许应用程序检测输入电压是否超出用户定义的高/低阀值。ADC 的输入时钟不得超过14MHz,它是由PCLK2经分频产生。图1 ADC框图...

2021-08-05 07:16:30

看了ADS1178的数据手册,输入时钟CLK范围是100kHz到27MHz之间,SCLK推荐为CLK的1、1/2等

问题:

1、转换速率是否只与MODE有关,与输入时钟无关?若设置MODE为0

2025-01-24 07:21:21

在System Control and Interrupts Reference Guide中描述GPIO:GPIOINENCLK设置是否使能GPIO的输入时钟,关于GPIO的输入时钟有点晕,GPIO需要时钟做什么?

2018-05-14 08:50:24

本帖最后由 zyf630197730 于 2015-3-30 10:36 编辑

用DAQ控件设计一个数据采集系统,采样频率为1HZ。起初用while循环,可是运行时间久了,发现采样间隔不是1s。怎样做到严格的1Hz啊。现在想用电脑上的时钟作为采样时钟的频率源,怎样调用电脑系统的时钟呢?

2015-03-27 16:38:39

MMCM是否也适用于40 Mhz或其他输入时钟?如果不工作,如何配置动态输入时钟MMCM?感谢您的帮助!以上来自于谷歌翻译以下为原文Hi, I have a question about

2019-03-14 17:04:56

你好,最近在用PCM1794做一款产品,在模式选择时,FTM1脚给一个高电平(3.3v)时,会把3.3v电位拉低到1V左右,FTM0脚则不会出现这种现象,在此存在疑惑,另外,对于PCM1794的输入时钟存在较小误差,会引起PCM1794无法工作吗?望解答,谢谢

2024-12-20 08:25:11

你好,我们在设计中需要使用 hmc7044 产生一系列频率为 204MHz 且相位对齐的时钟,并且所有的 204MHz 时钟都由 外部VCO输入时钟 816MHz 所产生。

目前所有的时钟都已经获取

2023-12-01 10:15:39

一个1Hz的时钟信号可否驱动led闪烁?

2014-03-29 14:05:05

本人在使用DS90CR286A芯片时出现如下情况,输入稳定的40M差分时钟,但是输出时钟时有时无,我的power dowm管脚是直接拉高的。

输入时钟

输出时钟

不知道出现这种情况的可能

2025-01-07 07:25:21

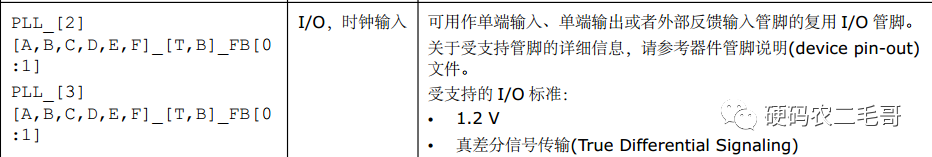

奇怪的行为。在深入了解“Ouroboros”时钟之前,我们来看一下基本的时钟切换术语和标准输入时钟切换配置。

2021-02-26 07:50:42

想用555定时器提供一个1hz的信号给数字时钟,结果连接完了,输出也正常,但是时钟却是从35s开始的,,不知道为啥,

2016-04-15 18:59:41

如果xilinx V5板子 程序中使用外部输入时钟,clk=36.15MHz,现在需要使用36.15*6=216.9MHz的时钟进行运算,如何生成该时钟?求指导。ucf文件中已定义NET "

2014-12-16 16:12:31

频率计,multisim仿真,用晶振做1Hz和10Hz的时钟,六位计数器,译码,数码管显示

2015-12-09 16:19:31

AD9163的时钟输入范围多大,输入时钟大小与输入数据速率是什么关系?

2018-07-31 09:42:19

1、参考时钟REFin输入采用方波输入时:1)交流耦合还是直流耦合?2)采用3.3Vcmos方波输入电平时,是直接直流耦合输入还是交流耦合?手册中的输入口推荐电路该如何理解2、供电Vvco管脚的供电是否需要和VDD、AVDD供电分开,是否可以合用?

2019-03-04 16:01:45

,AD9106的输入时钟和我系统的采集卡时钟是同步 的,这样DDS输出的波形就和采集卡的不同步,会导致采集有误差!期待你们帮助!谢谢!另外DDSAD9834也存在这样的问题!

2018-08-15 07:04:44

我们使用开发板,想实现输入时钟和输出时钟相位同步的功能,输入和输出时钟都是LVCMOS电平,一路输入时钟12.288M,一路输出时钟49.152M。

要求输入12.288M时钟相位变化时,输出时钟

2024-11-11 08:25:23

lvds时钟的时钟。例如,SVGA的时钟对频率为40MHz,串行数据频率为280MHz。但是selectIO向导假设输入时钟是280MHz?因为我看到它在源代码中将输入时钟分为1/7。以上来自于谷歌翻译以下

2019-07-17 07:20:11

我有一个输入时钟(SCKx4),它是我的RTL发送器端的源时钟,这个时钟通过FPGA传送出去(命名为TDM_SCKx4)到另一个设备。此SCKx4的原理图中的路径如下:SCKx4 - >

2020-08-18 10:16:10

请问如果将c6457定时器的时钟输入源配置为内部时钟输入,那么它的实际输入时钟频率怎么计算呢?谢谢!

2018-07-25 06:47:09

请问我要用74ls161怎么计数到2400时钟频率1HZ

2019-04-22 05:37:25

最小RBW 提高到1Hz升级文件

2017-12-25 16:04:36

DS1081L是扩展频谱时钟调制器IC,可降低高频时钟数字设备的EMI。DS1081L采用集成锁相环(PLL),输入时钟信号范围20MHz至134MHz,输出经过频谱扩展调制的时钟。可通过引脚设

2008-04-15 09:07:29 36

36 DS26504是楼宇综合定时供给系统(BITS)的时钟恢复器件。该芯片还可用作基本的T1/E1收发器。接收部分可以从T1、E1、64kHz复合时钟(64KCC)和6312kHz同步定时接口恢复时钟。在T1/E1模式下,

2008-08-04 09:31:40 24

24 DS1083L是扩展频谱时钟调制器IC,可降低高频时钟数字电子设备的EMI。DS1083L采用集成锁相环(PLL),输入时钟信号范围为16MHz至134MHz,输出经过频谱扩展调制的时钟信号。可通过引

2008-08-10 09:26:45 24

24

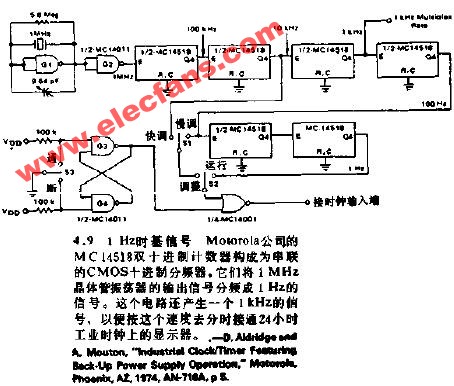

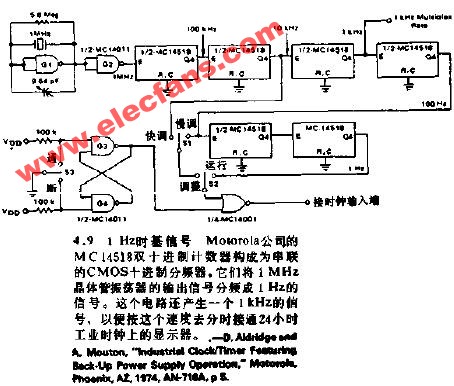

1HZ时基信号电路

2009-01-13 19:22:59 3262

3262

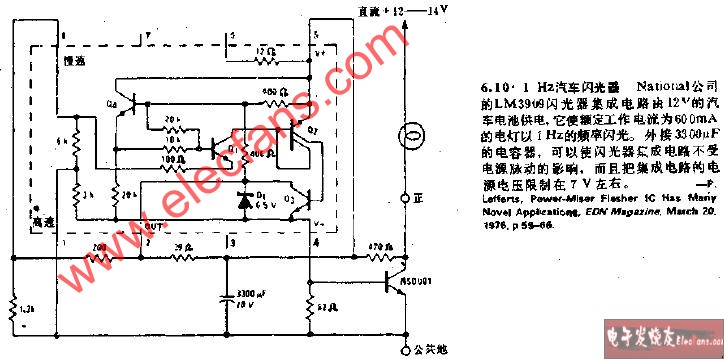

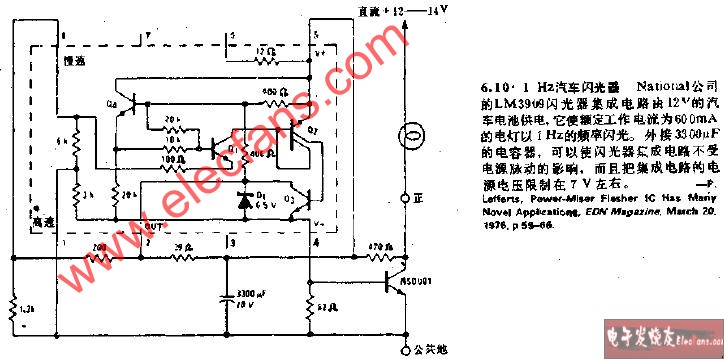

1Hz汽车闪光器电路

2009-01-17 13:57:58 2006

2006

AC2301是一款3GHz、10路差分扇出缓冲器,用于高频、低抖动时钟/数据分配和电平转换。可从两个差分输入或一个晶体输入中选择输入时钟。所选择的输入时钟被分配到两组输出,每组输出包含5个差分输出

2025-11-11 16:41:47

IC数据和时钟时钟线缓冲电路

2009-09-12 11:57:02 1707

1707

基于FPGA的提取位同步时钟DPLL设计

在数字通信系统中,同步技术是非常重要的,而位同步是最基本的同步。位同步时钟信号不仅用于监测输入码元信号,确保收发

2010-01-25 09:36:18 3699

3699

同步网时钟及等级

基准时钟 同步网由各节点时钟和传递同步定时信号的同步链路构成.同步网的功能是准确地将同步定时信号从基

2010-04-03 16:27:34 4060

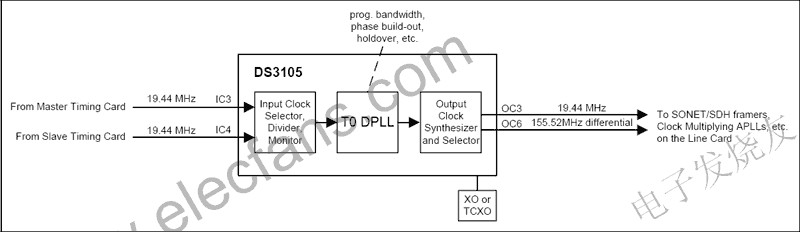

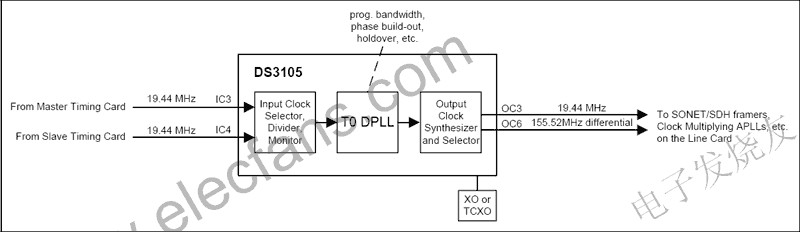

4060 DS3105是一款低成本、功能丰富的时钟IC,用于电信线卡。通常,器件从双冗余系统时钟卡接收两路参考时钟。DS3105连续监测两路输入时钟,并在主参考时钟失效时自动地无缝切

2010-09-15 09:35:41 1174

1174

DS31400是一款灵活的高性能定时IC,用于各种频率转换和频率合成应用。该器件的8路输入时钟和14路输出时钟的任何一

2010-11-24 09:35:36 1137

1137 DS31408是一个灵活的,高性能的不同频率转换时间和频率合成中的应用集成电路。在其八个输入时钟和14个输出时钟,

2011-03-21 11:40:29 2070

2070 DS31404是一个灵活的,高性能的不同频率转换时间和频率合成中的应用集成电路。在其四个和八个输入时钟的输出时钟,每个设备可以接受或生成几乎任何2kHz和750MHz的频率之间

2011-03-21 11:42:52 1592

1592 Abstract: This application note describes how Maxims DS314xx clock-synchronization ICs can be field

2011-03-28 09:44:09 41

41 基于实时时钟模块 时钟芯片DS1302

2017-10-16 11:35:07 40

40 v2,SyncEth,ToP,TDM时钟同步等,以满足无线设备和传输设备的时钟同步和传输需求。 微波时钟同步组网 针对微波自身特点,将对目前常用的几种同步方法进行简要介绍,以加深时钟同步的认识度。 1. 通过E1/T1实现时钟同步 在这种方式下,E1/T1业务将携带的TDM原始时钟

2017-12-07 20:51:01 1085

1085 对DS80C320双串行口的运用,简化了系统设计,并扩展了1PPM,1PPH等同步对时脉冲的输出。该GPS卫星同步时钟已用于变电站自动化系统中,其运行结果表明,它为整个系统提供了精确的时间信息,具有较高的可靠性和实用性,完全能够满足电力系统对高精度对时信号源

2018-02-10 11:17:57 4

4 DS12887是美国达拉斯半导体公司最新推出的时钟芯片,采用CMOS技术制成,把时钟芯片所需的晶振和外部锂电池相关电路集于芯片内部,同时它与目前IBM AT计算机常用的时钟芯片MC146818B

2018-03-16 16:29:42 11

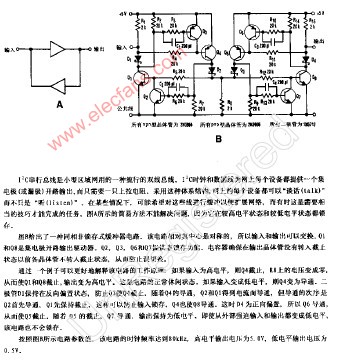

11 1Hz至1MHz的信号发生电路,1Hz~1MHz Signal generating circuit

关键字:运放方波信号发生电路

以

2018-09-20 19:58:21 2834

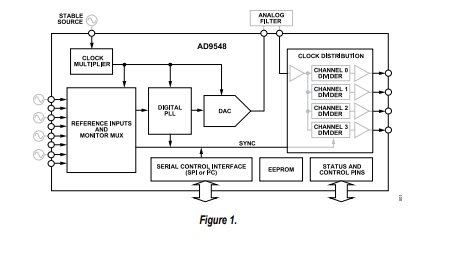

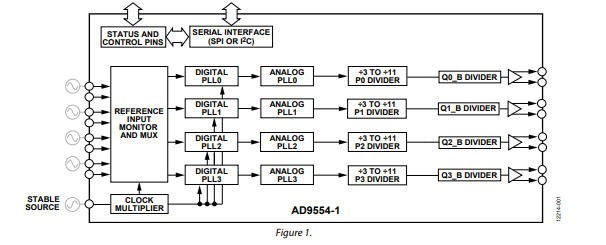

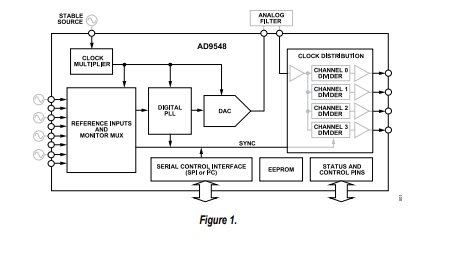

2834 AD9548: 8通道1HZ~750MHZ参考输入,4通道1HZ~400MHZ差分输出,典型输出抖动小于1PS rms。应用范围:网络时钟同步、GPS 1PPS同步、抖动滤除、2级钟/3级钟同步/保持/切换功能、无线基站时钟同步。

2019-06-10 06:17:00 6942

6942 RTC 时钟模块 DS1302实时时钟 SPI接口

板载纽扣电池座 支持三线或四线同步串行通信 应用于手持设备 电子手表 闹钟

型号 DS1302 RTC Board

2019-12-30 10:03:10 4180

4180

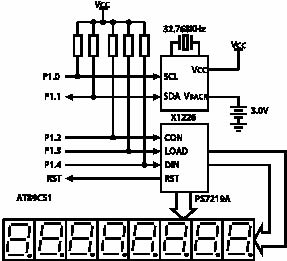

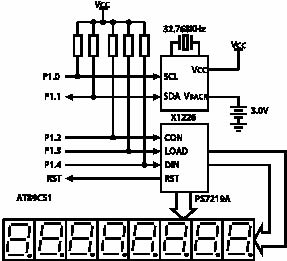

X1226具有时钟和日历的功能,时钟依赖时、分、秒寄存器来跟踪,日历依赖日期、星期、月和年寄存器来跟踪,日历可正确显示至2099年,并具有自动闰年修正功能。拥有强大的双报警功能,能够被设置到任何时钟/日历值上,精确度可到1秒。可用软件设置1Hz、4096Hz或32768Hz中任意一个频率输出。

2020-06-13 11:13:13 3752

3752

程序实现对输入时钟信号的7分频介绍。

2021-03-17 14:59:23 11

11 电子发烧友网为你提供基本时钟切换术语和标准输入时钟切换配置资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-05 08:40:34 7

7 EE-393:保护ADSP-CM41x器件免受输入时钟/电源故障

2021-05-07 13:55:11 2

2 存储实时时钟/日历的 31 字节的静态 RAM,可通过简单的串行接口与微处理器通讯,将当前的是时钟存于RAM。DS1302芯片对于少于 31 天的月份月末会自动调整,并会自动对闰年进行校正。由于有一个...

2022-01-17 13:03:59 29

29 1.介绍DS1302是一种串行接口的实时时钟,芯片内部具有可编程的日历时钟和31个字节的静态RAM。2.内部结构(1)SCLK:串行时钟输入端,控制数据输入与输出。(2)I/O:双向输入线(3)CE

2022-01-18 08:54:59 3

3 DS1302时钟比起DS18B20而言要简单的多。需要注意的大概两点:1. 写入时分秒void set_time(unsigned char shi, unsigned char fen

2022-01-18 08:55:59 4

4 实验18:DS1302时钟主程序

2022-01-18 09:08:02 29

29 如何使用实时时钟 IC DS1307 制作准确的时钟。时间将显示在液晶显示屏上。

2022-04-26 17:23:31 8101

8101

这是带有板上芯片(COB)的1Hz时钟发生器电路。通常,为数字时钟和计数器电路应用产生1Hz时钟的电路将IC与晶体和微调电容器等结合使用。

2022-06-07 10:43:50 3854

3854

ISE版本为14.7 1、时 钟IP核(Clocking Wizard) 第一页 Clocking Features选项框中: (1)Frequency synthesis选项是允许输出与输入时钟

2022-07-03 14:42:10 5988

5988 2022-11-17 12:42:26 0

0 电子发烧友网站提供《Arduino Shield NCS314 NIXIE电子管时钟.zip》资料免费下载

2022-11-22 11:58:45 0

0 Maxim的DS314xx系列时钟同步IC是功能强大、灵活的电信系统同步定时解决方案。这些器件最初设计用于锁定2kHz至750MHz的输入时钟频率,该频率范围可满足大多数电信系统的需求。然而,有时

2023-01-29 19:05:34 1835

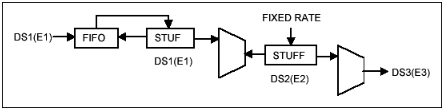

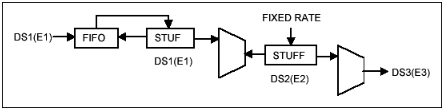

1835 在发射端,DS3(E3)时钟和DS1(E1)时钟由输入引脚派生,但DS2(E2)时钟频率是DS3(E3)时钟频率的一小部分。出于设计原因,分数将表示为整数比率,这取决于设备的模式。DS1(E1)时钟可以容忍基于DS3(E3)时钟频率和器件模式的频率范围。

2023-02-22 10:10:18 1372

1372

本应用笔记介绍了ADI公司的DS314xx时钟同步IC如何进行现场升级,以接受并锁定至1Hz输入时钟信号。它还描述了在少数情况下需要1Hz时钟监控功能和系统软件支持。有了这些元件,使用DS314xx器件构建的系统就可以与1Hz和更高速输入时钟的任意组合实现符合标准的时钟同步行为。

2023-03-08 15:22:00 2248

2248 目前使用AD9545方案,备注:1PPS_IN为上升沿500ms的1HZ的时钟信号,Rise time 160us左右,现在有以下问题请帮忙Spport一下

2023-03-08 16:00:00 1971

1971 DS3112具有六种不同的发送时钟和六种不同的接收时钟类型:发送DS3、DS2、DS1、E3、E2和E1时钟,以及接收DS3、DS2、DS1、E3、E2和E1时钟。由于电路中同一级的时钟具有相似

2023-06-13 15:39:46 1210

1210

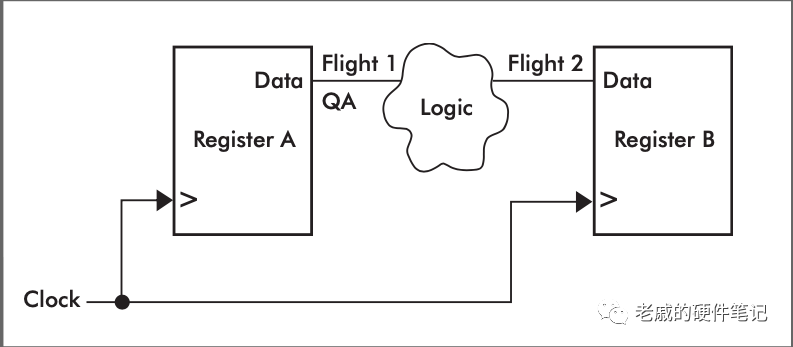

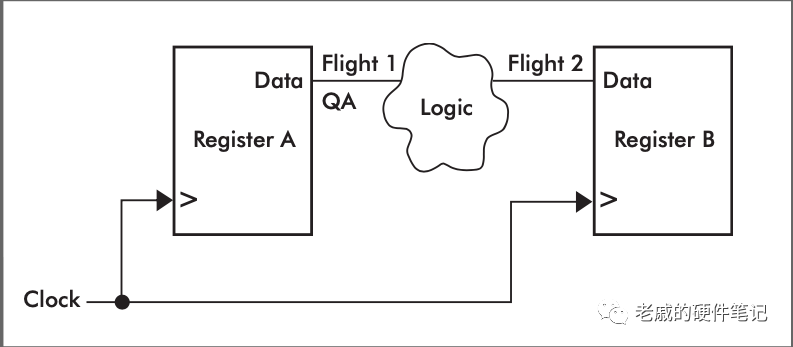

高速数字电路模块通常以 同步 (synchronous)电路的形式实现,它们由一个或者多个时钟驱动(触发)。对于 单一时钟(域) 的同步电路而言,只要输入和时钟的关系满足 建立(setup)时间

2023-06-23 17:53:00 2782

2782

几年前FPGA时钟只需要连接一个单端输入的晶振,非常容易。现在不同了,差分时钟输入,差分信号又分为LVDS和LVPECL,时钟芯片输出后还要经过直流或交流耦合才能接入FPGA,有点晕了,今天仔细研究一下。

2023-08-21 11:28:44 14322

14322

怎样用CD40106芯片分别产生1Hz和50Hz的时钟信号? 首先,让我们了解一下CD40106芯片的基本原理和功能。CD40106芯片是一种多功能CMOS集成电路,内部有6个门电路,主要用于触发器

2023-10-25 15:07:52 3077

3077 如何用时钟振荡器产生稳定的100hz或1hz的时钟信号? 时钟信号是电子系统中至关重要的组成部分,用于同步各种信号和操作。它需要稳定、准确、可靠地工作,以确保系统性能。时钟信号的产生可以通过许多

2023-10-25 15:07:55 2951

2951 DS1302时钟芯片是一种实时时钟芯片,采用三线串行接口与微处理器相连,可以提供年、月、日、时、分、秒等时间信息。

2023-11-18 09:39:40 7050

7050 实现数据的正确传输和协调。 网络时钟同步的要求主要包括以下几个方面: 1. 精度要求:根据不同的应用场景和需求,对网络时钟同步的精度要求也有所不同。例如,对于金融交易系统来说,时钟同步的精度要求非常高,通常要求在毫

2024-01-16 16:03:25 2667

2667 FPGA输入的时钟信号必须是方波么?正弦波会有影响么? FPGA是一种可编程逻辑器件,通常用于实现数字电路。输入时钟信号是FPGA中非常重要的时序信号,对整个系统的稳定性和性能都有很大影响。在

2024-01-31 11:31:42 5410

5410 等领域得到了广泛应用。 1. GPS卫星同步时钟的工作原理 GPS卫星同步时钟的工作原理可以分为以下几个步骤: GPS卫星信号接收:GPS接收机接收来自多颗GPS卫星的导航信号,其中包含卫星的精确时间信息。 时间信息提取:接收机对接收到的导航信号

2024-03-19 10:28:04 3646

3646

电子发烧友网站提供《CDCLVP111-SP具有可选输入时钟驱动器的低电压1:10 LVPECL数据表.pdf》资料免费下载

2024-08-20 09:15:44 0

0 电子发烧友网站提供《CDCLVP111低压1:10 LVPECL,内置可选输入时钟驱动器数据表.pdf》资料免费下载

2024-08-21 11:37:08 0

0 电子发烧友网站提供《CDCLVP110带可选输入时钟驱动器数据表.pdf》资料免费下载

2024-08-22 10:52:47 0

0 ,以确保视频信号的同步和稳定。以下是关于视频时钟合成芯片的使用指南: 1. 视频时钟合成芯片的基本概念 视频时钟合成芯片是一种数字电路,它通过相位锁定环(Phase-Locked Loop,PLL)技术来生成稳定的时钟信号。这种芯片可以接收一个输入时钟信号,并根据需要生成

2024-10-10 11:17:18 1231

1231 时钟缓冲器是一种用于生成、处理和分配时钟信号的电子电路,主要用于确保数字系统中各模块的同步操作。其核心功能是对输入时钟信号进行调理和分配,以提供高质量、低抖动的时钟信号。

2025-02-17 14:34:51 2136

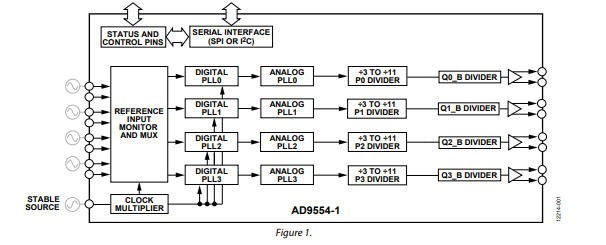

2136 AD9554-1是一款低环路带宽时钟倍频器,可针对包括同步光纤网络(SONET/SDH)的许多系统提供抖动清除和同步功能。 AD9554-1产生的输出时钟可以与多达四路外部输入参考时钟同步

2025-04-10 11:21:01 794

794

AD9547针对许多系统提供同步功能,包括同步光纤网络(SONET/SDH)。该器件产生的输出时钟可以与两路差分或四路单端外部输入参考时钟之一同步。数字锁相环(PLL)可以降低与外部参考时钟

2025-04-11 09:37:58 758

758

AD9548可为包括同步光纤网络(SONET/SDH)在内的许多系统提供同步。它可以产生一个与高达四个差分或者八个单端外部输入基准之一同步的输出时钟。数字PLL能减少与外部基准有关的输入时间抖动或者

2025-04-11 10:40:04 810

810

CDC1104是一个 1 到 4 可配置的时钟缓冲器。该器件接受输入参考时钟,并创建 4 个缓冲输出时钟,输出频率等于输入时钟的一半 频率。四个控制输入,S1、S2、S3、S4 时钟输出的可配置相位。

2025-09-16 09:37:34 658

658

探索RC192xx:PCIe Gen5/6 2 - 输入时钟复用器家族的卓越性能 在当今高速发展的电子领域,对于高性能时钟复用器的需求日益增长。Renesas的RC192xx系列时钟复用器,包括

2025-12-30 09:55:12 91

91

电子发烧友App

电子发烧友App

评论