D触发器的稳态

D触发器是数字电路中常用的一种存储元件,它有两种稳态,即低电平稳态和高电平稳态。当输入D为低电平时,输出Q保持为低电平;当输入D为高电平时,输出Q保持为高电平。

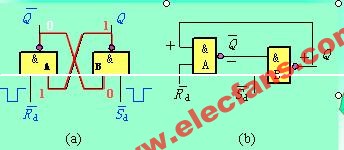

D触发器和RS触发器的区别

- 输入方式不同:

D触发器只有一个输入端D,用来接收输入信号;

RS触发器有两个输入端R和S,在不同情况下,分别用来置位和复位。 - 输出方式不同:

D触发器有一个输出端Q和一个补码端Q',可以分别输出D和D的补码;

RS触发器有两个输出端Q和Q',分别输出R的补码和S的补码。 - 输入控制方式不同:

D触发器的输入D可以直接控制Q的状态,而与此同时不影响Q的状态;

RS触发器的输入R和S是控制输入端,分别用来控制Q的置位和复位。 - 稳态数量不同:

D触发器有两个稳态,即低电平稳态和高电平稳态;

RS触发器有四个稳态,即禁止态、置位态、复位态和反转态。 - 触发方式不同:

D触发器属于正沿触发器,只有在时钟上升沿才会被触发;

RS触发器既可以是正沿触发器,也可以是负沿触发器。 - 其他功能不同:

D触发器还有一个使能端使能输入端D,控制输入D是否起作用;

RS触发器可以通过使能端来控制不同状态的切换。

D触发器的特点和应用

- 特点:

- D触发器具有较高的稳定性,可以储存和传递信号的状态。

- D触发器适用于时序电路的设计,实现数据的锁存和延迟。

- D触发器可以连接成扩展触发器,实现更复杂的功能。

- 应用:

- 数字时钟等计时电路,使用D触发器存储并控制时间信号的传输。

- 寄存器等存储电路,使用D触发器实现数据的存储和传输。

- 时钟触发的逻辑电路,使用D触发器实现时序逻辑功能。

总结:

本文详细介绍了D触发器的稳态、与RS触发器的区别,以及D触发器的工作原理、特点和应用。D触发器具有稳定的高低电平稳态,适用于时序电路的设计和数据的锁存。与RS触发器相比,D触发器具有较简单的输入方式和输出方式,并且能够通过使能端来控制输入的有效性。D触发器的主要实现方式包括异或门和与非门两种,可以通过连接形成更复杂的触发器电路,应用于数字时钟、寄存器等电路中。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

存储

+关注

关注

13文章

4693浏览量

89570 -

元件

+关注

关注

4文章

1212浏览量

38462 -

D触发器

+关注

关注

3文章

181浏览量

49532 -

RS触发器

+关注

关注

3文章

101浏览量

18812 -

高电平

+关注

关注

6文章

225浏览量

22690

发布评论请先 登录

相关推荐

热点推荐

rs触发器和d触发器的区别 钟控rs触发器的作用是什么

由于RS触发器实现方式的不同,对输入信号抖动(即短时间内多次变化)的响应也不同。原始的电路设计可能导致RS触发器对输入信号的抖动比较敏感。

rs触发器和双稳态触发器的区别

RS触发器是由两个交叉连通的反相器(NOT门)和两个逻辑门组成的,通常是由两个与门(AND门)和一个非门(NOT门)构成。而双稳态触发器(也

d触发器有几个稳态 触发器上升沿下降沿怎么判断

稳态是指触发器在某个特定的输入状态下稳定保持输出的状态。根据触发器的类型和触发方式,触发器分为很多种类,不同类型的

t触发器与d触发器的区别和联系

在数字电路设计中,触发器是一种非常重要的存储元件,用于存储一位二进制信息。触发器的种类很多,其中最为常见的是T触发器(Toggle Flip-Flop)和D

t触发器变为d触发器的条件

在数字电路设计中,触发器是一种非常重要的存储元件,用于存储一位二进制信息。触发器的种类很多,其中最为常见的有JK触发器、D

rs触发器的工作原理 rs触发器和sr触发器的区别

RS触发器是一种双稳态触发器,它有两个输入端:R(Reset)和S(Set),以及两个输出端:Q和Q'(Q的反相)。RS

d触发器有几个稳态 d触发器和rs触发器的区别

d触发器有几个稳态 d触发器和rs触发器的区别

评论