先给大家简单快速地介绍一下 Vivado 集成设计环境,即 IDE。当打开 Vivado 工程后,会有一个工程概要,向您介绍工程的设置、警告和错误信息以及工程的一般状态。

2012-04-25 09:00:43 6408

6408 本在生产力方面进行了两大改进。Vivado设计套件2013.1版本新增了一款以IP为中心的设计环境,用以加速系统集成;而其提供的一套完整数据库,则可加速C/C++系统级设计和高层次综合(HLS)。

2013-04-08 15:08:54 902

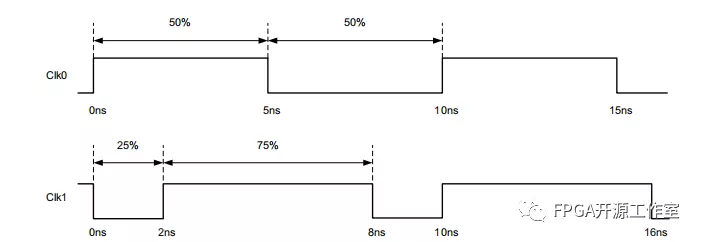

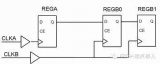

902 跨时钟域路径分析报告分析从一个时钟域(源时钟)跨越到另一个时钟域(目标时钟)的时序路径。

2020-11-27 11:11:39 5449

5449

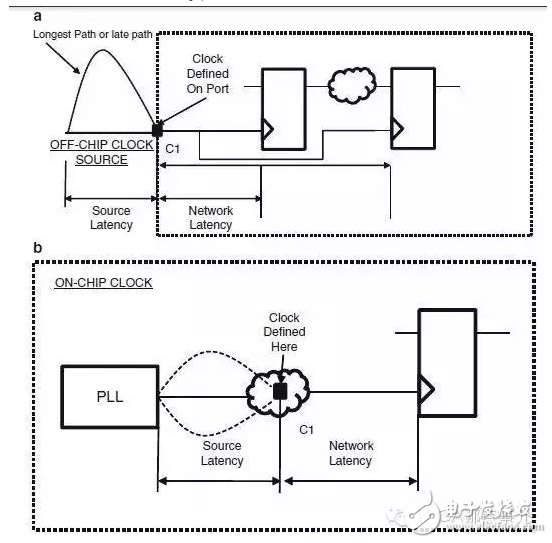

1. 时钟介绍 在数字设计中,时钟代表从寄存器(register)到寄存器可靠传输数据的时间基准。Xilinx Vivado集成设计环境(IDE)时序引擎使用ClocK特征计算时序路径要求,并通过

2020-11-29 10:51:45 5359

5359

作者:Mculover666 1.实验目的 通过例程探索Vivado HLS设计流 用图形用户界面和TCL脚本两种方式创建Vivado HLS项目 用各种HLS指令综合接口 优化Vivado HLS

2020-12-21 16:27:21 3153

3153 Xilinx的新一代设计套件Vivado相比上一代产品ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言XDC以及脚本语言Tcl的引入则成为了快速掌握Vivado使用技巧的最大障碍,以至于两年多后的今天,仍有很多用户缺乏升级到Vivado的信心。

2022-09-14 09:09:56 1526

1526 FPGA中的BUFGCE_DIV/BUFG_GT以及Versal中的MBUFG/BUFG_GT等。对于这类时钟,Vivado会自动创建时钟,并不需要用户手工通过create_generated_clock创建。

2024-01-11 09:50:09 400

400

,只有在时钟的支持下,电子产品才能正常工作。 那么时钟产品有哪些种类,它们分别有什么特性,工程师在选用的时候需要注意些什么呢,我们今天就来一起聊一聊。 时钟产品的分类 时钟产品主要分为两大类,一类是异步时钟产品,

2021-09-06 07:18:00 6088

6088 Vivado概述 / 251.3.1 Vivado下的FPGA设计流程 / 251.3.2 Vivado的两种工作模式 / 261.3.3 Vivado的5个特征 / 30参考文献 / 31第2章

2020-10-21 18:24:48

1.实验目的通过例程探索Vivado HLS设计流用图形用户界面和TCL脚本两种方式创建Vivado HLS项目用各种HLS指令综合接口优化Vivado HLS设计来满足各种约束用不用的指令来探索

2021-11-11 07:09:49

Vivado下set_multicycle_path该怎样去使用呢?在两个不同时钟主频的情况下使用set_multicycle_path的情况是怎样的?

2022-02-16 08:00:49

和Vivado的综合性能,管脚位置与电平约束完全一致。PS:若时钟和管脚约束直接敲命令,两者除了语法,没有明显区别。6、综合实现——点评:Vivado默认策略情况下从综合到生成bit共计23分50秒。而

2021-01-08 17:07:20

)无法通过放置阶段,会产生大量的放置错误,如下所示。基本上,Vivado不能放置与时钟相关的任何原语 -BUFG,BUFH,PLLE2_ADV,GTHE2_COMMON等。设计针对xc7vx690t

2018-11-02 11:32:44

Vivado综合可以理解多种多样的RAM编写方式,将其映射到分布式RAM或块RAM中。两种实现方法在向RAM写入数据时都是采取同步方式,区别在于从RAM读取数据时,分布式RAM采用异步方式,块RAM

2020-09-29 09:40:40

Vivado 设计分为 Project Mode 和 Non-project Mode 两种模式,一般简单设计中,我们常用的是 Project Mode。在本手册中,我们将以一个简单的实验案例,一步一步的完成 Vivado的整个设计流程。

2023-09-20 07:37:39

图所示:接下来的页面是选择用于采样待测信号的时钟域,Vivado会自动识别出各个待测信号所属的时钟域并将其自动设定为其采样时钟,例如,我们刚刚添加的这“led_OBUF”和“cnt”两个信号就属于

2023-04-17 16:33:55

你好,我在Win10中使用vivado 2016.2 for zynq7020。我的时钟方案是zynq PS FCLK_CLK0-->时钟向导IP输入(Primitive PLL)的输入。合成

2018-11-05 11:40:53

想到要写这一系列关于工具和方法学的小文章是在半年多前,那时候Vivado®已经推出两年,陆续也接触了不少客户和他们的设计。我所在的部门叫做“Tools & Methodology

2023-09-20 06:31:14

使用的是18.1版本的VIVADO。 这次的练习选择的是ZYNQ的芯片,原本工程是工作在100MHz的时钟,但是作为练习,我们可以把时钟调到一个极限的程度来进行优化。 首先,打开一个工程,更改一下时钟频率,使得工程

2018-08-22 11:45:54

距离2016智能硬件开发者创客大会召开的日子越来越近了,作为本次亮点之一的第十九届电路保护与电磁兼容技术工作坊将会给我们带来什么样的惊喜了,据小编了解此次工作坊将会分为两大会场,前有各大知名公司老总

2016-03-29 14:00:52

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG NODE-LOCKED LICENSE

2023-03-30 12:04:13

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG NODE-LOCKED LICENSE

2023-03-30 12:04:13

现代高级雷达系统正在受到多方面的挑战——频率分配上的最新变化导致许多雷达系统的工作频率非常接近通信基础设施和其他频谱要求极高的系统。

2019-07-22 07:50:19

RTC时钟具有哪些特性应用?

2021-10-13 06:09:16

RTC时钟具有哪些特性? RTC正常工作的一般配置步骤是怎样的?

2021-11-23 06:52:26

STM32F407之时钟、频率、存储概述文章目录STM32F407之时钟、频率、存储概述1.整体特性1.1存储器组织架构1.2 内嵌SRAM1.3Flash和自举程序2.电源3.时钟介绍3.1系统

2021-08-02 07:24:37

为什么要使用thumb模式,与ARM相比较,Thumb代码的两大优势是什么?

2022-11-02 14:17:55

问候!我正在使用Virtex7 / XC7V2000T / ***1925。我有两个clcoks,pipe3_clk和ulpi_clk,连接到同一时钟区域的两个CCIO,X1Y7。但Vivado在

2020-07-16 14:18:54

伺服电机分为交流伺服和直流伺服两大类。交流伺服电机的基本构造与交流感应电动机(异步电机)相似。在定子上有两个相空间位移90°电角度的励磁绕组Wf和控制绕组WcoWf,接恒定交流电压,利用施加到Wc上

2021-06-28 09:45:02

,设置的主时钟频率是250M,实际送给cpu的也是这个频率,但是看了一下nuclei studio里面的system_hbirdv2.c文件里面的时钟频率确是80M,这俩已经不匹配了,但是在vivado

2023-08-11 11:18:54

单片机最小系统电路包括哪两大类

2023-10-31 07:28:49

我在vivado 2016.3中看到了以下地方的错误错误:[放置30-675]支持全局时钟的IO引脚和BUFG对的次优放置。如果此子设计可接受此子优化条件,则可以使用.xdc文件中

2018-11-09 11:37:33

如果我有两个设计项目,让我调用项目A和B.现在我需要做的是将这两个项目组合成一个项目C,如何在Vivado中进行这种组合?提前致谢。以上来自于谷歌翻译以下为原文If I have two

2019-02-28 09:26:27

秒(100 Mhz)关闭和打开一个LED,我这样做是为了验证如何更改ZYNQ的时钟频率使用vivado的约束。这是我放在.xdc文件中生成不同的时钟频率set_property PACKAGE_PIN

2020-04-01 08:46:16

完整的小车控制程序,包括上位机和下位机两大部分attach://147399.rar

2013-07-20 09:31:30

。标准的嵌入式系统架构有两大体系,RISC处理器和CISC处理器体系。嵌入式主板分为比较常见的两大类:1、基于X86的嵌入式主板,Intel的X86 处理器就属于CISC体系,(一般使用INTEL、AMD、威盛、或其他产家的...

2021-12-16 06:41:20

逻辑门控无法映射到Vivado中的一个时钟区域时,BUFHCTRL能够复制自身并将逻辑映射到多个时钟区域吗?谢谢,雨翔

2020-07-27 14:26:34

大家好,据我了解,Vivado仅在合成过程的地点和路线部分使用多线程。那么,真正改变vivado性能的方法(性能=从头开始合成项目的速度+在vivado合成时在计算机上执行其他工作的能力)主要是核心

2019-04-25 06:33:01

嗨,我想创建一个设计,我需要2Mhz clk,我想用16Mhz输入时钟的vivado套装中的“时钟向导”IP核生成它。根据Xilinx手册(下面的链接),这可以通过CLKOUT4_CASCADE选项

2020-07-27 06:32:48

量级。如要对晶振老化漂移优化,需要得到晶振在上级时钟良好、时钟板处于锁定状态下的漂移,通过读取锁定电压值即可。 需要特别注意的是,这个锁定值会在晶振老化漂移的基础上叠加晶振温度特性的影响,如果晶振温度

2013-12-17 16:10:55

你好,有没有办法在新的vivado IDE中使用时钟向导(v3.5)实现“旧”生成的IP?特别是我遇到了问题,当我自动升级时,有一些输出缺失。例如,是否在较新版本的时钟向导(v5.1)中实现了一个输出,它具有与向导生成的CLK_VALID输出相同的功能(v3.5)?谢谢!

2020-07-29 10:52:20

本帖最后由 iioloii 于 2022-4-24 10:44 编辑

分析A、B两个信号(由同一个时钟驱动)之间的时序时发现源时钟和目的时钟经过相同的元件或走线的延时是不一样的,不知道为甚会是

2022-04-24 10:32:49

谁来阐述一下电感式传感器可分为哪两大类?

2019-11-18 15:14:40

癌细胞生长速度比一般人快24倍;我国每年出生的2000万儿童中,有35万为缺陷儿,其中25万为智力残缺,有专家认为,电磁辐射是影响因素之一因此,电磁辐射问题越来越受到世界各国的普遍重视。高尔生教授在他的《空调使用对***质量的影响》中指出,电磁辐射对人体的危害,表现为热效应和非热效应两大方面。

2019-05-31 06:45:55

`错误提示截图放在二楼,用vivado14.4写了个1×8和8×8矩阵相乘的程序,调用了64个ip核乘法器,IO口用的有些多。综合和实现网表都能成功,就是仿真总是提示这两个错误,仔细检查了几遍程序

2020-04-26 19:21:25

vivado自己设置的工程目录本身比较深,而文件路径太深会导致某些奇怪的错误。这是windows系统本身的特性决定的,windows的路径名不能超过260字节,所以大家设计的时候一定注意路径名长度

2019-09-11 11:52:42

亲爱的大家,我现在正在使用Vivado 2013.3。我试图将PL结构时钟从1 MHZ更改为500KHZ。 (1 MHZ下没问题)但是,Vivado在运行综合时崩溃了。对我来说减少PL结构时钟非常重要,因为我打算在一个时钟周期内收集更多的XADC数据。我该怎么办?谢谢!

2020-03-25 08:40:07

在Vivado中通过set_clock_groups来约束不同的时钟组,它有三个选项分别是-asynchronous,-logically_exclusive

2017-02-08 08:39:49 919

919

Suite 和 UltraFast™ 设计方法加速设计生产力: . 查看 UltraFast 设计方法指南 · 观看 Vivado 快速入门视频 ,深入了解 Vivado Design Suite 的各种工具与特性,视

2017-02-09 09:06:11 295

295 搭载“部分重配置技术”的 Vivado 2017.1 的 HLx 版本软件现在可以下载了!

2018-07-08 06:23:00 4534

4534 此篇文章里,我们将通过使用InTime来检验Vivado 2017.1和Vivado2016.4之间的性能对比。 概要:分别进行了3个Vivado 2017.1对Vivado2016.4的性能测试

2018-07-04 11:23:00 9674

9674

无论此刻你是一个需要安装Xilinx Vivado工具链的入门菜鸟,还是已有license过期的Vivado老铁,今儿咱就借着这篇文章,把学习「Vivado如何获取License」这档子事儿给说通透咯~ 手把手教程,分三部分讲述。

2018-07-03 09:54:00 58889

58889

vivado设计套件资料

2017-10-31 09:49:03 43

43 Xilinx的新一代设计套件Vivado相比上一代产品ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言XDC以及脚本语言Tcl的引入则成为了快速掌握

2017-11-18 03:52:01 4675

4675

时钟扩展对使用赛灵思Vivado设计套件的工程师来说是一个很大的挑战,但不是一个不可逾越的障碍。随着越来越多的赛灵思用户开始使用Vivado®设计套件,部分用户对未扩展时钟表示困惑。那么什么是未扩展

2017-11-18 13:28:01 761

761 1 Vivado HLS简介 2创建一个Vivado-HLS工程 2.1打开Vivado HLS GUI 2.2创建新工程 在 Welcome Page, 选择Create New Project

2017-12-04 10:07:17 0

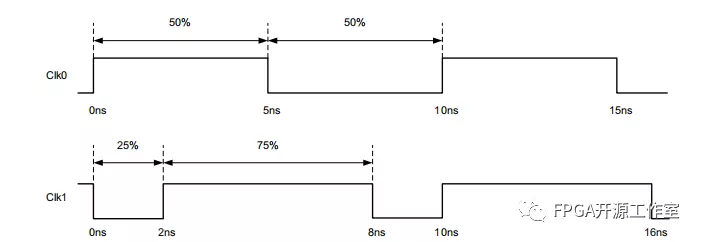

0 现在的硬件设计中,大量的时钟之间彼此相互连接是很典型的现象。为了保证Vivado优化到关键路径,我们必须要理解时钟之间是如何相互作用,也就是同步和异步时钟之间是如何联系。 同步时钟是彼此联系的时钟。

2018-05-12 10:15:00 19563

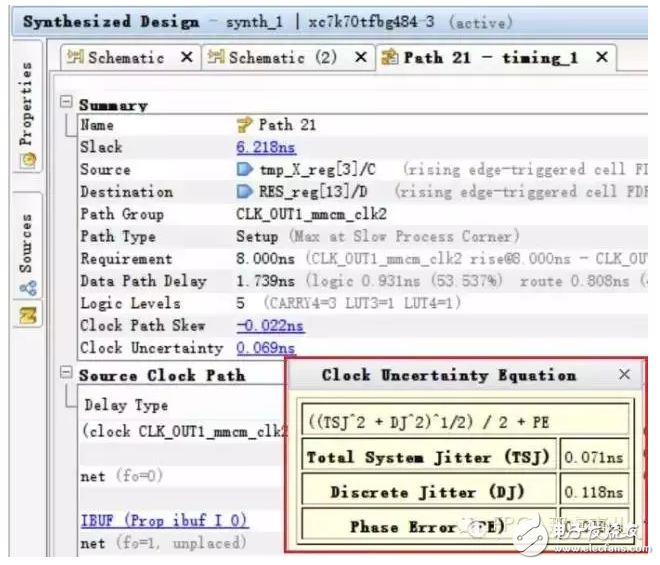

19563 时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习Vivado软件时序分析的笔记,小编这里使用的是18.1版本的Vivado。 这次

2019-09-15 16:38:00 5787

5787

本视频将指您介绍如何使用Vivado设计套件中的交互式“IO Pin Planning”和“Device Exploration”功能。具体来说,IO规划包括:在设计中创建,配置,分配和管理IO端口以及时钟逻辑

对象。该视频教程描述了在设计流程的不同阶段如何执行IO规划的步骤。

2018-11-20 06:36:00 4709

4709 2015年Club Vivado开发者大会的预览。

2018-11-20 11:51:25 992

992 该视频演示了如何使用Vivado IP Integrator组装具有多个时钟域的设计。

它显示了Vivado中的设计规则检查和功能如何帮助用户自动执行此流程。

2018-11-27 07:40:00 3539

3539 了解report_design_analysis,这是一个新的Vivado报告命令,可以独特地了解时序和复杂性特征,这些特性对于分析时序收敛问题很有价值。

2018-11-26 07:01:00 3314

3314 了解如何使用2014.1中引入的新激活许可为Vivado工具生成许可证。

另外,了解Vivado 2014.1中的许可更改如何影响您,以及如何在激活客户端中使用新的Vivado License Manager

2018-11-22 07:10:00 2614

2614 在Vivado Design Suite中,Vivado综合能够合成多种类型的属性。在大多数情况下,这些属性具有相同的语法和相同的行为。

2019-05-02 10:13:00 3750

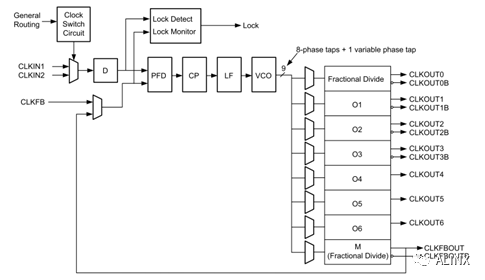

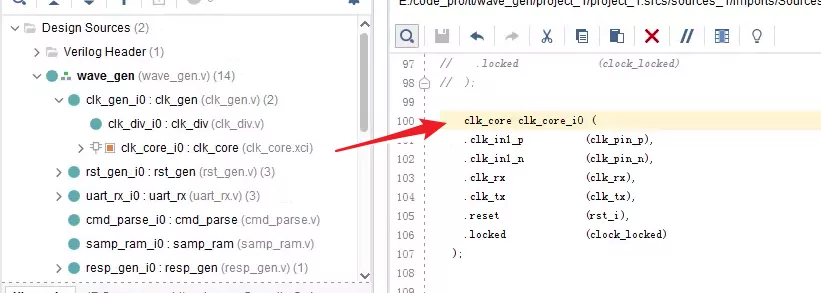

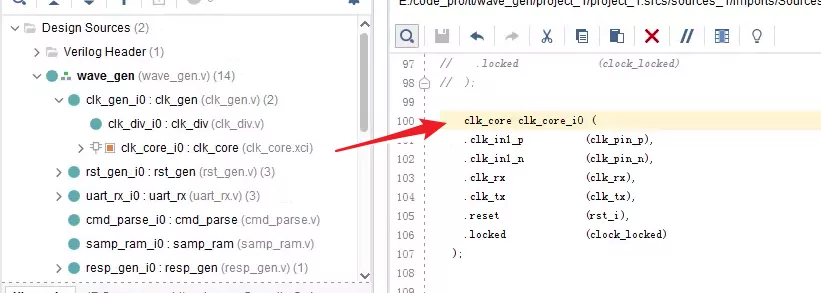

3750 在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,下面就介绍一下在vivado2017.3中进行PL开发时调用IP的方法。

2018-12-22 14:26:38 4468

4468 在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,这是同步时序电路的关键,这时就需要使用到时钟向导IP,下面就介绍一下在vivado中进行PL开发时调用IP的方法。

2018-12-22 15:14:38 10069

10069 关于Vivado Dashboard的功能可阅读这篇文章(Vivado 2018.3这个Gadget你用了吗)Vivado 2019.1的Dashboard功能进一步增强。

2019-06-12 14:49:24 7677

7677

交互式时钟域的交叉分析:该功能支持设计人员在设计早期阶段调试CDC问题。结合Vivado设计套件的交互式时序分析和交叉探测特性,CDC分析功能可提供强大的时序分析和调试功能,并加速产品上市进程。

2019-08-01 09:14:54 1862

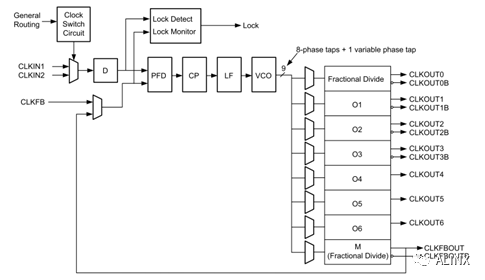

1862 ,但是也有类似的功能模块,通过PLL可以倍频分频,产生其他很多时钟。本实验通过调用PLL IP core来学习PLL的使用、vivado的IP core使用方法。

2022-02-08 15:13:17 3306

3306

Vivado 的XDC设置输出延时 Vivado 的XDC设置输出延时,用于输出伴随时钟和数据的,数据是由系统时钟125M驱动,伴随时钟是由125M经过Pll相位移动-90度。 设置输出时钟

2021-06-09 17:28:01 3888

3888

,只有在时钟的支持下,电子产品才能正常工作。 那么时钟产品有哪些种类,它们分别有什么特性,工程师在选用的时候需要注意些什么呢,我们今天就来一起聊一聊。 时钟产品的分类 时钟产品主要分为两大类,一类是异步时钟产品,它的

2021-09-08 14:23:44 4940

4940 Vivado License Manager在使用Vivado License Manager时,如果通过如下图所示方式指定license的路径时,要保证路径仅包含ASCII字符而没有中文字

2021-09-12 15:15:19 5055

5055 和FPGA设计进行连接。由于VIO核与被监视和驱动的设计同步,因此应用于设计的时钟约束也适用于VIO核内的元件。当使用这个核进行实时交互时,需要使用Vivado逻辑分析特性。 接下来将介绍VIO的原理及应用,内容主要包括设计原理、添加VIO核、生成比特流文件和下载并调试设计。 设计原理

2021-09-23 16:11:23 6841

6841

【流水灯样例】基于 FPGA Vivado 的数字钟设计前言模拟前言Vivado 设计流程指导手册——2013.4密码:5txi模拟

2021-12-04 13:21:08 26

26 Vivado下set_multicycle_path的使用说明 vivado下多周期路径约束(set_multicycle_path)的使用,set_multicycle_path一般...

2021-12-20 19:12:17 1

1 对于7系列FPGA,需要对GT的这两个时钟手工约束:对于UltraScale FPGA,只需对GT的输入时钟约束即可,Vivado会自动对这两个时钟约束。

2022-02-16 16:21:36 1229

1229

数字设计中,“时钟”表示在寄存器间可靠地传输数据所需的参考时间。Vivado的时序引擎通过时钟特征来计算时序路径需求,通过计算裕量(Slack)的方法报告设计时序空余。时钟必须有合适的定义,包含如下特性:

2022-04-20 10:40:48 7882

7882 Vivado 2022.1已正式发布,今天我们就来看看其中的一个新特性。

2022-07-03 17:00:25 1785

1785 Vivado可以导出脚本,保存创建工程的相关命令和配置,并可以在需要的时候使用脚本重建Vivado工程。脚本通常只有KB级别大小,远远小于工程打包文件的大小,因此便于备份和版本管理。下面把前述脚本升级到Vivado 2020.2为例,讨论如何升级Vivado工程脚本。

2022-08-02 10:10:17 1542

1542 今天介绍的是vivado的三种常用IP核:时钟倍频(Clocking Wizard),实时仿真(ILA),ROM调用(Block Memory)。

2023-02-02 10:14:01 2529

2529 Xilinx的新一代设计套件Vivado相比上一代产品 ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言 XDC 以及脚本语言 Tcl 的引入则成为

2023-04-15 09:43:09 958

958 今天推出Xilinx已发布的《Vivado使用误区与进阶》系列:用TCL定制Vivado设计实现流程。

2023-05-05 09:44:46 674

674

使用“时钟校准去歪斜”时,在 Vivado 中会显示下列消息以指明是否启用该功能特性

2023-07-07 14:14:50 347

347

vivado开发软件自带了仿真工具,下面将介绍vivado的仿真流程,方便初学者进行仿真实验。

2023-07-18 09:06:59 2137

2137

电子发烧友网站提供《Vivado设计套件用户:使用Vivado IDE的指南.pdf》资料免费下载

2023-09-13 15:25:36 3

3 电子发烧友网站提供《Vivado Design Suite用户指南:I/O和时钟规划.pdf》资料免费下载

2023-09-13 15:10:58 0

0 在Vivado中禁止自动生成BUFG(Buffered Clock Gate)可以通过以下步骤实现。 首先,让我们简要了解一下什么是BUFG。BUFG是一个时钟缓冲器,用于缓冲输入时钟信号,使其更稳

2024-01-05 14:31:06 454

454

电子发烧友App

电子发烧友App

评论