声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

33文章

1798浏览量

133638 -

IP

+关注

关注

5文章

1881浏览量

156664 -

时钟

+关注

关注

11文章

1999浏览量

135224

发布评论请先 登录

相关推荐

热点推荐

Vivado时序约束中invert参数的作用和应用场景

在Vivado的时序约束中,-invert是用于控制信号极性的特殊参数,应用于时钟约束(Clock Constraints)和延迟约束(Delay Constraints)中,用于指定信号的有效边沿或逻辑极性。

E203移植genesys2(差分时钟板)生成比特流文件全过程

在windows环境下实现移植流程,因为板子是差分时钟,在最初移植的过程中时序报告一直出错,经过调整分频设置之后可以成功生成bit文件。本文章带大家完成vivado阶段所有工作,从源代码到生成bit

发表于 10-27 07:16

采用xc7a200开发板移植蜂鸟E203

Vivado移植过程

本次板级验证基于vivado.2020.02,完成工程建立,所用FPGA板型为:xc7a200tfbg484-2,主要挑几个上板易错点进行分享。

2.1 时钟和复位IP

发表于 10-24 13:50

vcs和vivado联合仿真

我们在做参赛课题的过程中发现,上FPGA开发板跑系统时,有时需要添加vivado的ip核。但是vivado仿真比较慢,vcs也不能直接对添加了vivado

发表于 10-24 07:28

E203分享之DDR扩展方案实施流程(中)

的S00_AXI_ACLK、M00_AXI_ACLK,分别接系统顶层时钟hfextclk、mig产生的用户时钟ui_clk,以此来实现跨时钟域。

(2)例化DDR3模型(仿真的时候需要

发表于 10-24 07:25

Vivado浮点数IP核的握手信号

Vivado浮点数IP核的握手信号

我们的设计方案中,FPU计算单元将收到的三条数据和使能信号同步发给20多个模块,同时只有一个模块被时钟使能,进行计算,但结果都会保留,发给数选。计

发表于 10-24 07:01

Vivado浮点数IP核的一些设置注意点

Vivado浮点数IP核的一些设置注意点

我们在vivado2018.3中使用了Floating-point(7.1)IP核,可以自定义其计算种类及多模式选择。有时多种计算可以用同一

发表于 10-24 06:25

如何在Vivado上仿真蜂鸟SOC,仿真NucleiStudio编译好的程序

如标题所示,我们分享如何在Vivado上仿真蜂鸟SOC,仿真NucleiStudio编译好的程序

具体步骤

1. 将蜂鸟soc移植到Vivado

只要将端口映射好,注意配置好时钟和bank

发表于 10-21 11:08

AMD Vivado IP integrator的基本功能特性

我们还将带您了解在 AMD Zynq UltraScale+ MPSoC 开发板与 AMD Versal 自适应 SoC 开发板上使用 IP integrator 时,两种设计流程之间存在的差异。

LMK03318 具有单 PLL 的超低抖动时钟发生器系列技术手册

LMK03318器件是一款超低噪声PLLATINUM™时钟发生器,具有一个小数N频率合成器,集成了VCO、灵活的时钟分配和扇出,以及存储在片上EEPROM中的引脚可选配置状态。该器件可以为各种多千兆

黑芝麻智能跨域时间同步技术:消除多域计算单元的时钟信任鸿沟

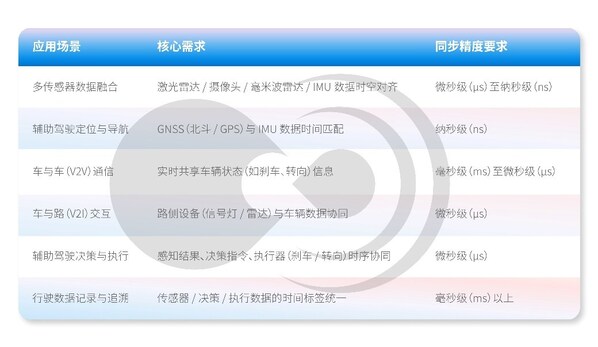

,并以黑芝麻智能武当 C1296 芯片为例,通过多方式同步实现多域高精度对齐,消除时钟信任鸿沟的实测效果。 智能汽车的核心是通过多维度感知、实时决策和精准控制实现辅助驾驶与智能交互,而这一切的前提是 "时间基准一致",由于不同传感器采集数据的频率、机制不同,只有在时间

跨异步时钟域处理方法大全

该方法只用于慢到快时钟域的1bit信号传递。在Xilinx器件中,可以使用(* ASYNC_REG = "TRUE" *)标记,将两个寄存器尽量靠近综合,降低 亚稳态因导线延迟太大而传播到第二个寄存器的可能性。

如何使用Vivado IP Integrator组装具有多个时钟域的设计

如何使用Vivado IP Integrator组装具有多个时钟域的设计

评论